传统的 SDR SDRAM 只能在信号的上升沿进行数据传输,而 DDR SDRAM 却可以在信号的上升沿和下降沿都进行数据传输,所以 DDR 内存在每个时钟周期都可以完成两倍于 SDRAM 的数据传输量,这也是 DDR 的意义——Double Data Rate,双倍数据速率。举例来说,DDR266 标准的 DDR SDRAM 能提供 2.1GB/s 的内存带宽,而传统的 PC133 SDRAM 却只能提供 1.06GB/s 的内存带宽。

一般的内存条会注明 CL 值,此数值越低表明内存的数据读取周期越短,性能也就越好,DDR SDRAM 的 CL 常见值一般为 2 和 2.5 两种。

DDR

DDR 是双倍数据速率(Double Data Rate)。DDR 与普通同步动态随机存储器(DRAM)非常相象。普通同步 DRAM(现在被称为 SDR)与标准 DRAM 有所不同。

标准的 DRAM 接收的地址命令由二个地址字组成。为接省输入管脚,采用了多路传输的方案。第一地址字由原始地址选通(RAS)锁存在 DRAM 芯片。紧随 RAS 命令之后,列地址选通(CAS)锁存第二地址字。经过 RAS 和 CAS,存储的数据可以被读取。

同步动态随机存储器(SDR DRAM)由一个标准 DRAM 和时钟组成,RAS、CAS、数据有效均在时钟脉冲的上升边沿被启动。根据时钟指示,可以预测数据和剩余指令的位置。因而,数据锁存选通可以精确定位。由于数据有效窗口的可预计性,所以可将存储器划分成 4 个区进行内部单元的预充电和预获取。通过脉冲串模式,可进行连续地址获取而不必重复 RAS 选通。连续 CAS 选通可对来自相同源的数据进行再现。

DDR 存储器与 SDR 存储器工作原理基本相同,只不过 DDR 在时钟脉冲的上升和下降沿均读取数据。新一代 DDR 存储器的工作频率和数据速率分别为 200MHz 和 266MHz,与此对应的时钟频率为 100MHz 和 133MHz。

SDR

DRAM 是动态存储器(DynaMIC RAM)的缩写 SDRAM 是英文 SynchronousDRAM 的缩写,译成中文就是同步动态存储器的意思。从技术角度上讲,同步动态存储器(SDRAM)是在现有的标准动态存储器中加入同步控制逻辑(一个状态机),利用一个单一的系统时钟同步所有的地址数据和控制信号。使用 SDRAM 不但能提高系统表现,还能简化设计、提供高速的数据传输。在功能上,它类似常规的 DRAM,且也需时钟进行刷新。可以说,SDRAM 是一种改善了结构的增强型 DRAM。目前的 SDRAM 有 10ns 和 8ns。

审核编辑 黄昊宇

-

DDR

+关注

关注

11文章

747浏览量

68542 -

SDR

+关注

关注

7文章

241浏览量

51787

发布评论请先 登录

【教程】一文教会你CE31-MD01X从绑定到场景控制

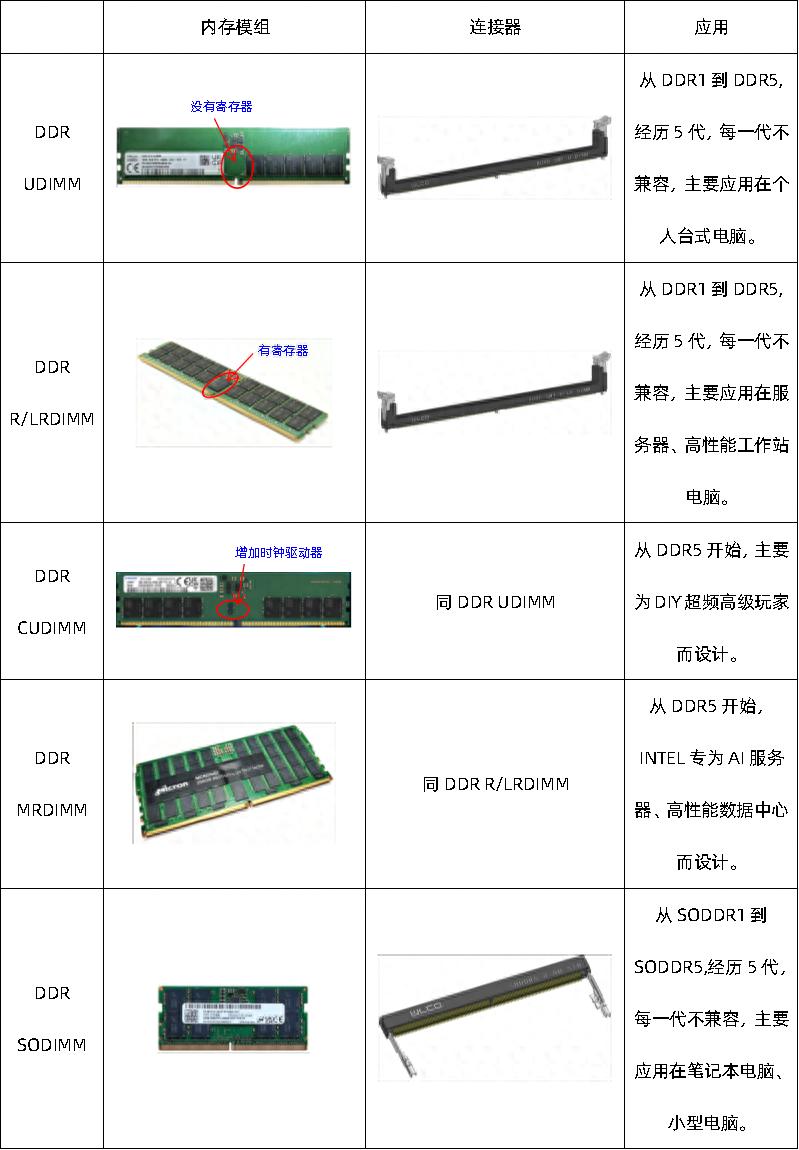

一文读懂DDR家族:UDIMM等全解析

DDR存储拓展教程

手把手教会你 EWM104-BT57U与 EWD104-BT57(485)蓝牙配对与数据透传

国产替代先锋:紫光国芯SDR–DDR4全覆盖,适配工业、电力、安防场景

AD设计DDR3时等长设计技巧

涨价!部分DDR4与DDR5价差已达一倍!

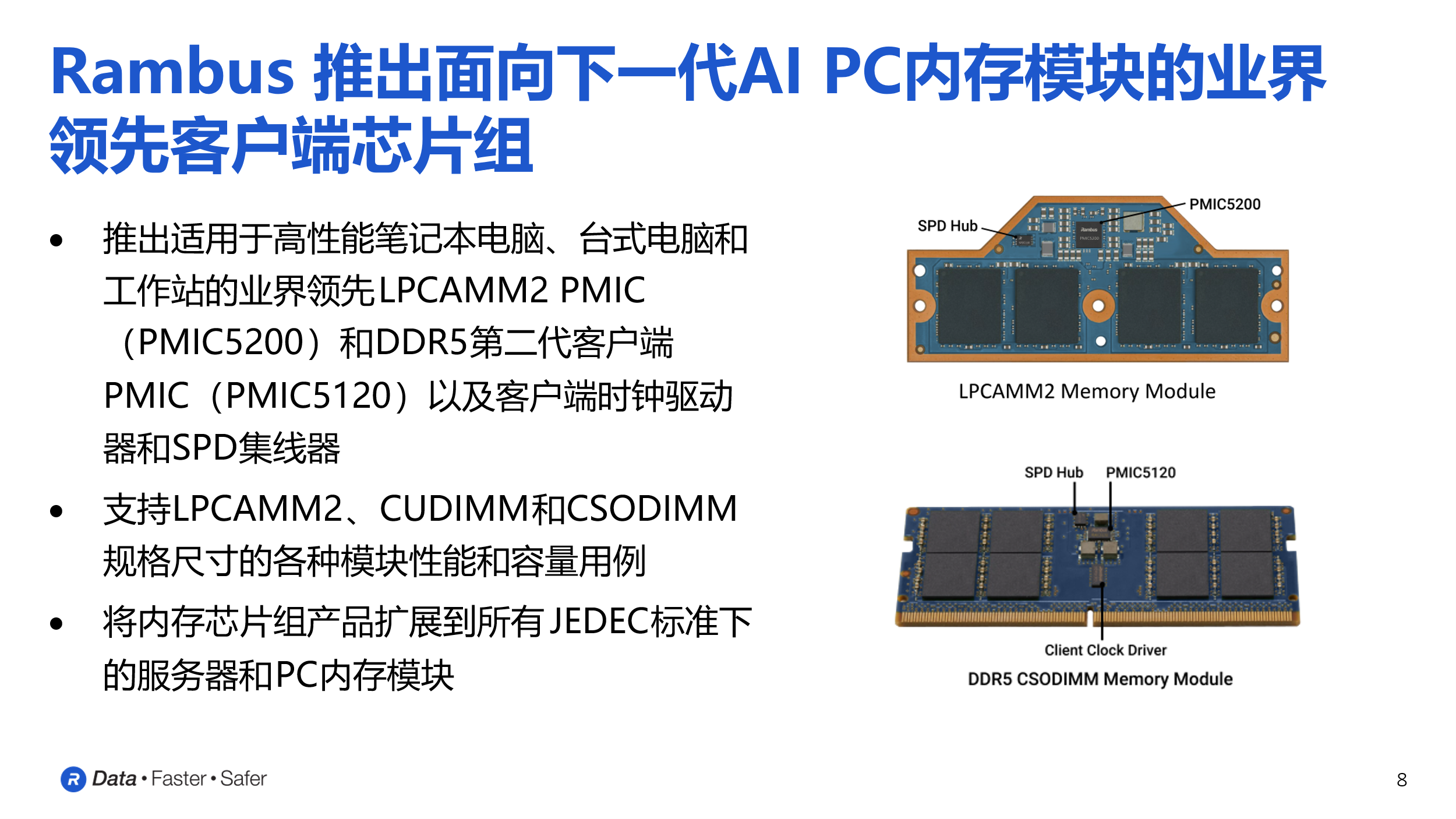

AI PC内存升级,这颗DDR5 PMIC一马当先

DDR3 SDRAM配置教程

一文教会你辨别SDR和DDR

一文教会你辨别SDR和DDR

评论