IP核描述

10 Giga Ethernet Sub System , 参考文档PG157:

https://www.xilinx.com/support/documentation/ip_documentation/axi_10g_et...

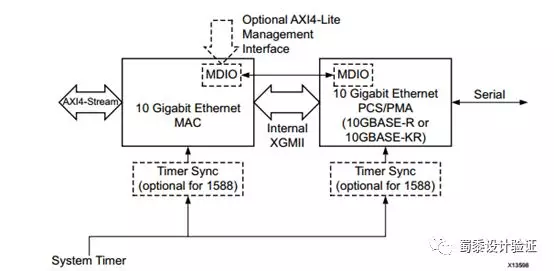

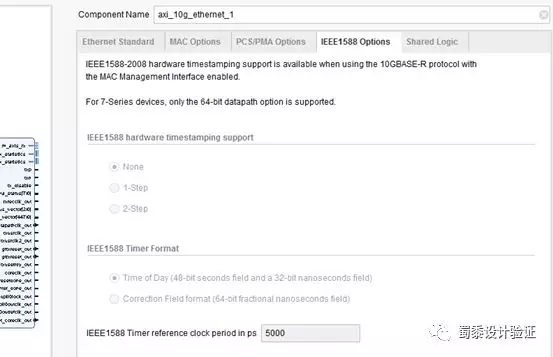

IP核提供一个MAC模块和一个PCS/PMA模块,PCS/PMA模块支持10GBASE-R/10GBASE-KR。客户端接口协议为AXI4 Stream,有32bits和64bits两种位宽,对于10GBASE-R,32bits位宽接口有着低延迟和低资源消耗的优势。AXI4-lite为可选接口,用于配置IP核内部寄存器。IP核支持DIC机制,支持Vlan和jumbo帧,支持客户定制Preamble。支持BASE-R上的1588时钟机制(onestep & two step)。

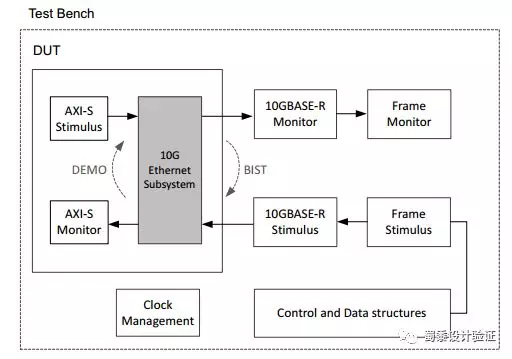

IP核总体框架如下图所示:

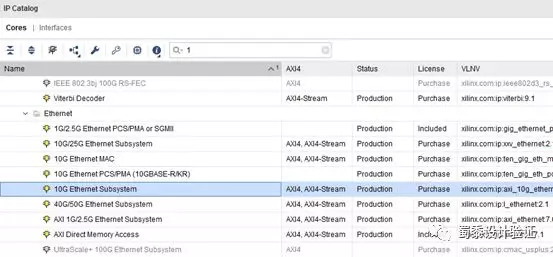

IP核生成

按如下步骤生成IP核:

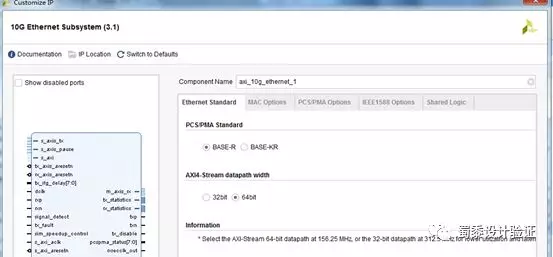

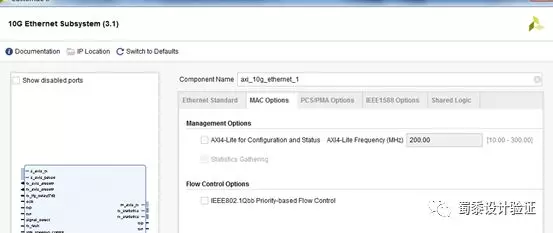

在生成IP核过程中有如下几个注意点:

1. MAC option模块中去除了AXI4-lite选项。此接口是连接至CPU接口的配置接口,这里去除是因为不知道CPU配置接口支持什么协议,在去除了这组接口后,IP核会将配置寄存器全部作为一组vector呈现在IP核端口上。

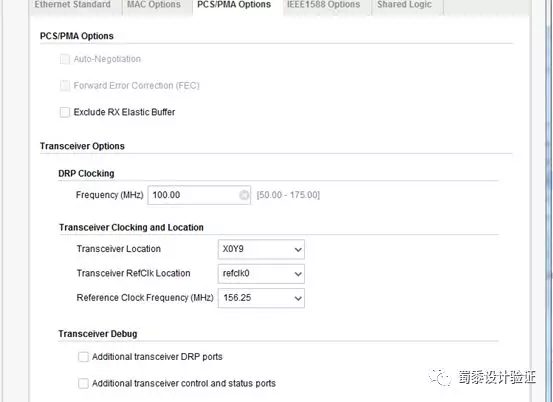

2. KCU105模块两个XG口的Transeiver绑定的x0y9和x0y10,所以选择其中之一即可(根据板子的具体情况去选择)。

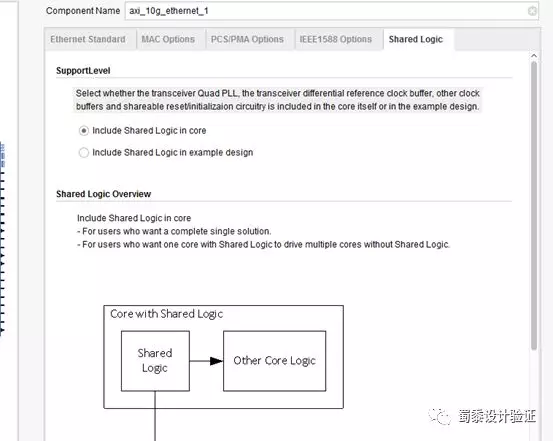

3. Shared Logic在Core和example中的区别就是GTHCHANNLE3在Core外面还是Core里边。如果不是做级联只用1个Core,那么就放在core里。

IP核仿真

这个IP核的仿真网表文件(axi_10g_ethernet_0_sim_netlist.v)是坏的,不能用来进行仿真,仿真现象是Core接口上很多输出是高阻。如果要仿真,则必须使用如下文件:

Sync目录下的axi_10g_ethernet_0.v;

bd_0文件夹中的内容。

Example设计中提供了一套验证环境,验证顶层文件为: axi_10g_ethernet_0_demo_tb.v。

这里需要注意的是:

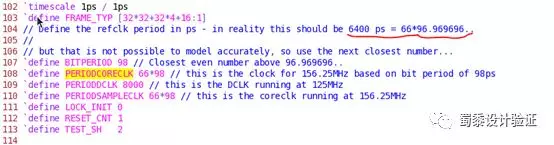

时间单位是1ps,精度也是1ps,serdes上是按66bits块串行打码流,那么比特周期就是6400/66,由于除不尽,就用了98这个整数,那么ref_clk就不能是6400了,所以这里的ref_clk是66*98.。如果不按这种处理,IP核在仿真时就不能link上,从RxGMII接口上看就是一直有link fault,码流是坏的。

仿真平台框图如下图所示:

Bench支持两种模式:

1. DEMO模式,这种模式下必须开启address swap功能,激励是从rx串行端口灌进去的,在PktGen模块中通过Axi4-Stream环回。

2. BIST模式,激励从Xgmii TX端口灌进去,在串行端口环回。

接口解析

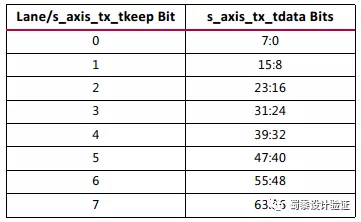

以64bits位宽为例

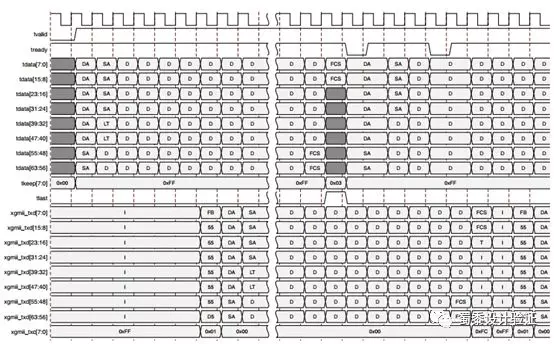

1. client Tx Interface

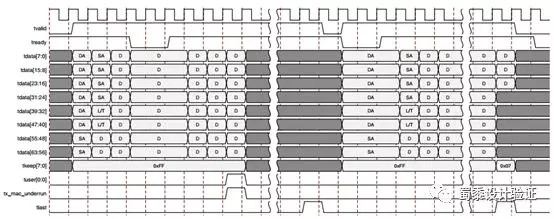

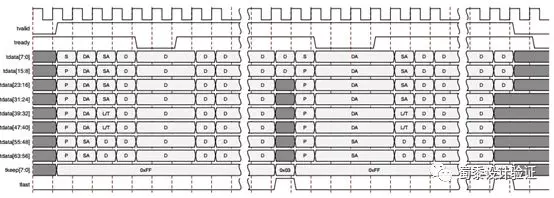

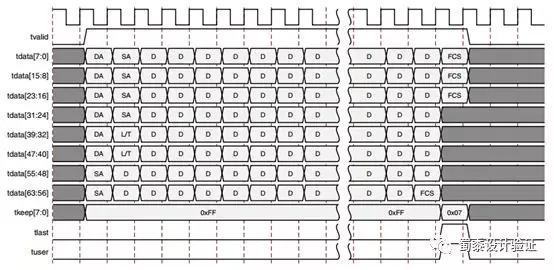

1.1. TX Normal

信号在tready为高时才能传输,当tready为低时数据必须保持到tready为高时发出,DA的第一个字节必须在数据通道0上,tlast表示传输的最后一片,有效字节靠tkeep来标识。

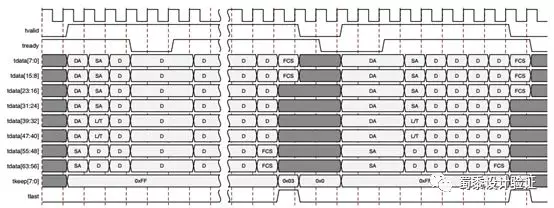

1.2.TX In band FCS padding

Core可以配置成in-band FCSpassing,意思是在包的尾部跟CRC,32个比特。当Core没有配置成这个模式时,如果client发了小于46Byte的payload,Core能自动padding,将包长度padding成符合以太网最小包长的包。如果配置了in-band FCS padding,则client需要保证最小包长,如果没有提供符合要求长度的包,则core在FCS后padding,并表示这是个无效包。

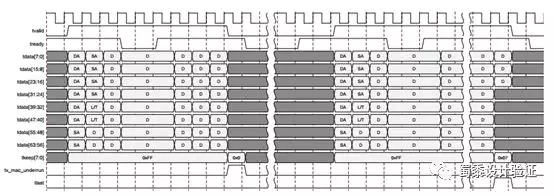

1.3. TX Abording Transmissio

假如要终止一次传输该怎么做?

在client interface处终止一个包的传输操作称为underrun,这种情况发生时由于在整包传输完成前发送端口处FIFO空了,有两种情况:

a. 在txvalid有效的情况下将tx_tuser置起。断包必须要有DA,SA,L/T域。

b. 包尾处tx_tlast没有置起。

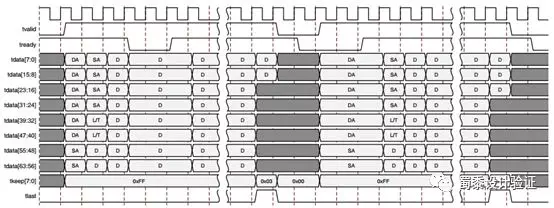

1.4. Back to Back

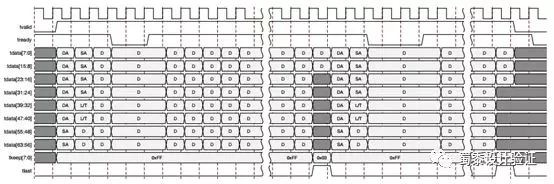

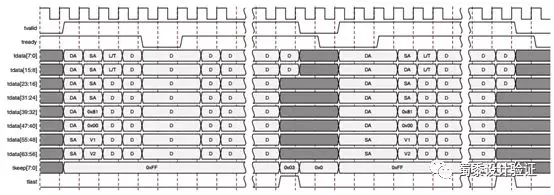

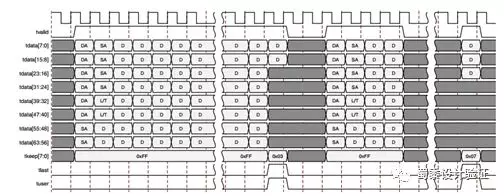

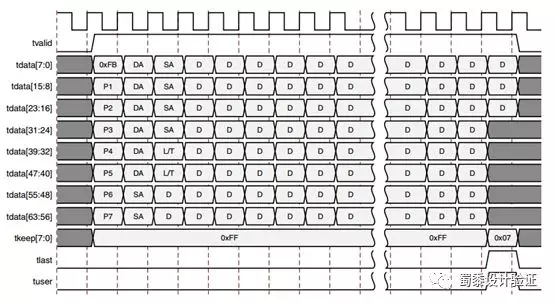

1.5. 自定义Preamble

就是在DA前将8字节Preamble加上。根据IEEE802.3规定,Strat必须在第0条数据通路上。分不连续传输和连续传输两种,分别如下图所示。

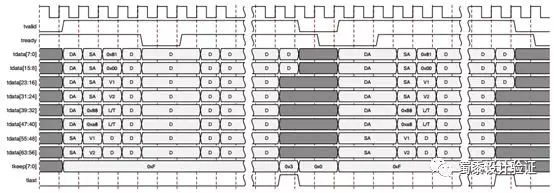

1.6. Vlan Tag Frame

提供Vlan Tag传输功能,客户端需提供8100tag标志。传输时序如图所示。

Vlan Tagged

Q in Q Vlan Tagged

1.7.Jumbo 帧传输

设计默认disable此功能,在此功能被关闭时若client传输超长帧,超长帧将被truncated,error code被插入显示此帧错误。

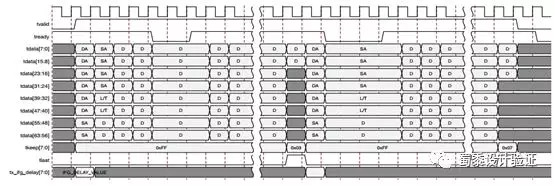

1.8. IPG 更改

你可以通过配置选择各种长度的IPG。通过ifg_delay_value来延迟XGMII column,Core产生反压来延迟下一帧的传送。

1.9. DIC机制

发送端支持DIC机制,有FCS和无FCS两种情况下均支持。Tx_valid必须持续为高保持数据传输最大效率化。

1.10. Link Fault

Core收到local/remotefault或者link interrupt时,在寄存器FaultInhibit被关闭的情况下,Core不会发送任何帧,Core中的RS层会被使能,当RS层收到LocalFault或者link interrupt ordered set,Core将发送Remote Ordered Sets.当收到Remote Fault 序列时,Core将发送IDLE。

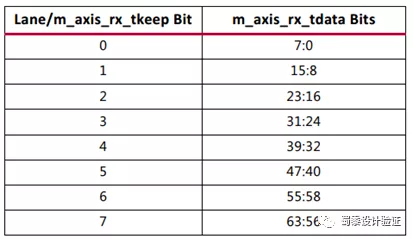

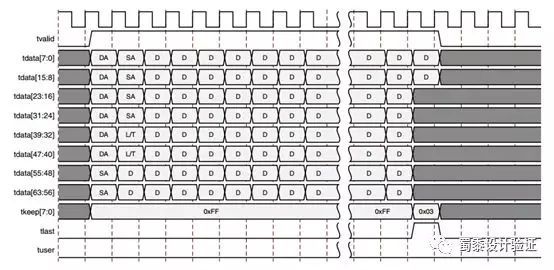

2. RX Client Interface

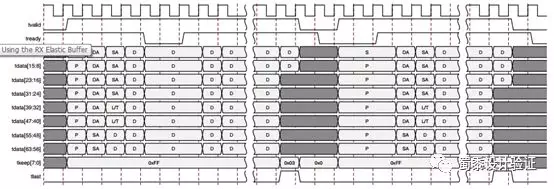

2.1.Normal Reception

rx_axis_tvalid为高表明接收数据有效,keep指示8条通路中有效的通路,这里要注意的是data是从最低为开始assign数据的,所以,最后一片数据的keep[0]一定为高。tx_usr为高持续一个时钟周期,表明收到的数据帧有效。

2.2. good frame or bad frame

传输的最后一片数据至少得有一个Byte有效,keep不能为0;

传输的实际帧帧长比length域显示的大,则在FCS –PASS功能没有打开的情况下,多出来的会被当做padding而被移除;

Lenth域小于46,收到实际报文不满64,如果lengthcheck没有关闭的情况下,这个帧被标记为坏帧.

2.3. Frame reception with errors

接收错误报文(runt或者不正确crc)

错误帧产生因素:

1. FCS ERROR

2. 小于64Byte 的帧

3. 在jumbo帧功能没有使能的情况下收到jumbo帧

4. 设置了MTU,收到的帧比设置的MTU大并且jumbo帧功能没有使能

5. 长度/类型字段是长度,其中长度值小于46。在这种情况下,需要padding。如果没有padding,这时这个帧就是错误帧。

6. 长度/类型字段是长度,其中长度值是46或更大,但是真实的接收帧的长度不匹配或超过长度/类型字段中的值

7. 在没有禁用控制帧长度检查功能时,收到的控制帧长度小于最小帧长度;

8. XGMII code中有ERROR

9. 有效pause帧,因为其已经被MAC逻辑使用;

2.4. Reception with FCS passing

如果FCS check failed ,则last为高时user信号为低;

2.5. Reception with Preamble

就是preamble出现在stream接口上,同TX

2.6. 带Vlan Tag

Vlan Tag使能,接收端会出现Vlan域,最大包长变成1522B

2.7. 超长帧传输

设置MTU(Max TransmitUnit)的值必须大于1518,jumbo 帧功能需要打开;

编辑:hfy

-

寄存器

+关注

关注

31文章

5589浏览量

129057 -

cpu

+关注

关注

68文章

11216浏览量

222933 -

Xilinx

+关注

关注

73文章

2192浏览量

129925

发布评论请先 登录

Molex EXTreme Ten60Power 混合电源连接器技术解析

求助,关于mcs文件生成的问题求解

win10环境下使用vivado生成.bit与.mcs文件

E203移植genesys2(差分时钟板)生成比特流文件全过程

FPGA利用DMA IP核实现ADC数据采集

Xilinx Shift RAM IP概述和主要功能

详解Xilinx的10G PCS PMA IP

Vivado FIR IP核实现

美国多ip服务器租用配置步骤

新加坡共享主机怎么设置ip

SRIO介绍及xilinx的vivado 2017.4中生成srio例程代码解释

Xilinx Ten Giga Sub System IP生成详细步骤

Xilinx Ten Giga Sub System IP生成详细步骤

评论