0、引言

CD4017C集成电路应用非常广泛,但大多资料对其内部电路逻辑功能的推导却是轻描淡写,甚至不乏错误之处,文中通过约翰逊计数器32种随机输出码状态转换的逻辑计算和分析,对CD4017C集成电路内部逻辑电路的结构、原理作了深入详细的阐述。

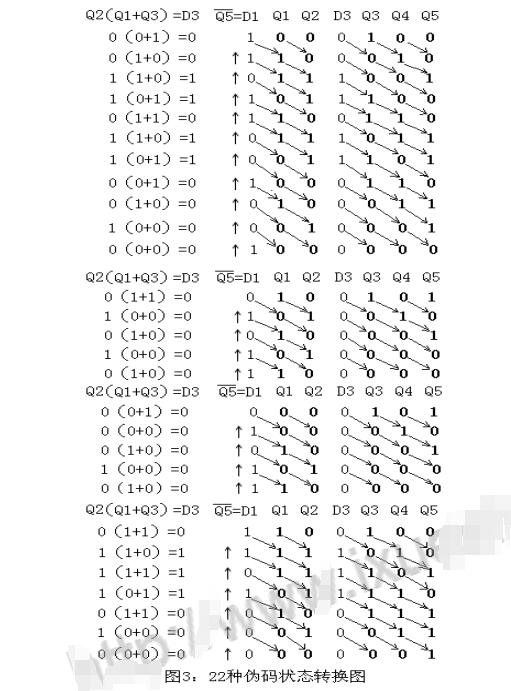

1、CD4017C集成电路的引脚功能(见图1)

CD4017C集成电路共有11个输出端:3脚(Y0)、2脚(Y1)、4脚(Y2)、7脚(Y3)、10脚(Y4)、1脚(Y5)、5脚(Y6)、6脚(Y7)、9脚(Y8)、11脚(Y9)分别为第0~第9输出端;12脚(Qco)为级联进位输出端。3个输入端:13脚(EN)为时钟脉冲输入端,下降沿计数有效;14脚(CP)为时钟脉冲输入端,上升沿计数有效;15脚(R)为复位清零输入端,加高电平或正脉冲时计数器清零。2个供电端:8脚(Vss)为电源负端;16脚(VDD)为电源正端3~18V。

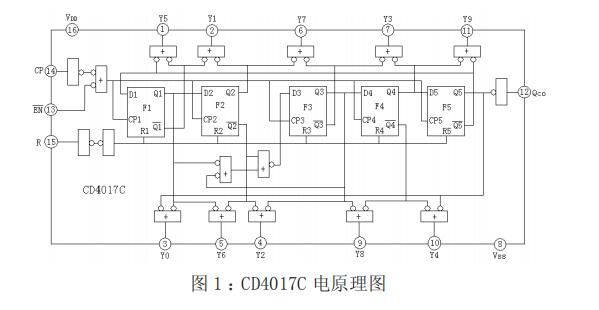

2、十进制约翰逊计数器电路分析(见图1)

十进制约翰逊计数器实质上是一种串行移位寄存器,由D触发器Fl~F5构成,除了第3个触发器是通过组合逻辑电路作用于F3的D3端以外,其余各级均是将前一级触发器的输出端Q连接到后一级触发器的输入端D的,计数器最后—级F5的 端连接到第一级的D1端。当加上清零脉冲后,Q1~Q5均为“0”,由于Q1的数据输入端D1是Q5输出的反码

端连接到第一级的D1端。当加上清零脉冲后,Q1~Q5均为“0”,由于Q1的数据输入端D1是Q5输出的反码 ,因此,输入第—个时钟脉冲后,Q1即为“l”,这时Q2-Q5均依次进行移位输出,Ql的输出移至Q2,Q2的输出需经组合逻辑电路转化成D3后才能移至Q3,Q3的输出移至Q4,Q4的输出移至Q5,Q5的输出被移出(溢出),如果继续输入脉冲,则Q1为新的

,因此,输入第—个时钟脉冲后,Q1即为“l”,这时Q2-Q5均依次进行移位输出,Ql的输出移至Q2,Q2的输出需经组合逻辑电路转化成D3后才能移至Q3,Q3的输出移至Q4,Q4的输出移至Q5,Q5的输出被移出(溢出),如果继续输入脉冲,则Q1为新的 ,Q2~Q5仍然依次按上述规律移位输出,从而导出十进制计数循环状态(见图2),这就是我们所需十进制计数循环的10种状态。

,Q2~Q5仍然依次按上述规律移位输出,从而导出十进制计数循环状态(见图2),这就是我们所需十进制计数循环的10种状态。

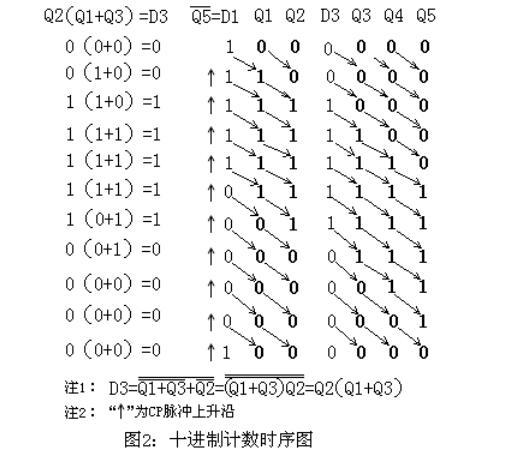

然而由五级计数单元组成的约翰逊计数器,其输出端可以有 =32种组合状态,而构成十进制计数器只需10种计数状态,因此,当电路接通电源之后,有可能进入我们所不需要的22种伪码状态中的任一状态,并伴随触发脉冲上升沿的出现自动进行移位寄存(见图3)

=32种组合状态,而构成十进制计数器只需10种计数状态,因此,当电路接通电源之后,有可能进入我们所不需要的22种伪码状态中的任一状态,并伴随触发脉冲上升沿的出现自动进行移位寄存(见图3)