完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > IP核

IP就是知识产权核或知识产权模块的意思,在EDA技术开发中具有十分重要的地位。美国著名的Dataquest咨询公司将半导体产业的IP定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。

IP就是知识产权核或知识产权模块的意思,在EDA技术开发中具有十分重要的地位。美国著名的Dataquest咨询公司将半导体产业的IP定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。IP主要分为软IP、固IP和硬IP。软IP是用Verilog/VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。固IP是完成了综合的功能块。硬IP提供设计的最终阶段产品——掩膜。

IP就是知识产权核或知识产权模块的意思,在EDA技术开发中具有十分重要的地位。美国著名的Dataquest咨询公司将半导体产业的IP定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。IP主要分为软IP、固IP和硬IP。软IP是用Verilog/VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。固IP是完成了综合的功能块。硬IP提供设计的最终阶段产品——掩膜。

基本分类

IP内核的三种类型

IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的方式,而这三种IP内核实现方法也各具特色。

软核

软核是用VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。软IP通常是以硬件描述语言HDL源文件的形式出现,应用开发过程与普通的HDL设计也十分相似,只是所需的开发硬软件环境比较昂贵。软IP的设计周期短,设计投入少。由于不涉及物理实现,为后续设计留有很大的发挥空间,增大了IP的灵活性和适应性。其主要缺点是在一定程度上使后续工序无法适应整体设计,从而需要一定程度的软IP修正,在性能上也不可能获得全面的优化。由于软核是以源代码的形式提供,尽管源代码可以采用加密方法,但其知识产权保护问题不容忽视。

硬核

硬核提供设计阶段最终阶段产品:掩膜。以经过完全的布局布线的网表形式提供,这种硬核既具有可预见性,同时还可以针对特定工艺或购买商进行功耗和尺寸上的优化。尽管硬核由于缺乏灵活性而可移植性差,但由于无须提供寄存器转移级(RTL)文件,因而更易于实现IP保护。

固核

固核则是软核和硬核的折衷。大多数应用于FPGA的IP内核均为软核,软核有助于用户调节参数并增强可复用性。软核通常以加密形式提供,这样实际的 RTL对用户是不可见的,但布局和布线灵活。在这些加密的软核中,如果对内核进行了参数化,那么用户就可通过头文件或图形用户接口(GUI)方便地对参数进行操作。对于那些对时序要求严格的内核(如PCI接口内核),可预布线特定信号或分配特定的布线资源,以满足时序要求。这些内核可归类为固核,由于内核是预先设计的代码模块,因此这有可能影响包含该内核的整体设计。由于内核的建立(setup)、保持时间和握手信号都可能是固定的,因此其它电路的设计时都必须考虑与该内核进行正确地接口。如果内核具有固定布局或部分固定的布局,那么这还将影响其它电路的布局。

技术应用

数字到模拟转换器(DACs)将一个二进制数转换为与之对应的电压值,常用的D/A转换器都是由电阻或电容加权网络、受码元控制的开关和基准电压或电流源组成。当D/A转换器需要转换的信号每次取样字长很长时,对这些电路的精度要求很高,并且还必须在整个温度范围和整个使用寿命期间内保持电路参数的稳定。例如,一个16位的D/A转换器,其MSB的精度必须在1/2 16以内,这是很困难的。所以,需寻求一种中保持高分辨率又可降低对电路精度和稳定度要求的方法。

可综合的Delta-Sigma DAC(术语Delta-Sigma分别指算术差与和,即Δ-∑DAC),是Xilinx公司提供的免费IP核,可从网上下载得到。

选择和配置

选择MAX7000S系列可编程逻辑器件,编译后由MAX+PLUS II软件自动配置进EMP7032SLC44芯片,将生成的目标文件通过编程电缆对器件进行编程。

将该IP核实现的D/A转换器用于新型智能电阻炉温度控制仪中,因为调节炉温的信号不要求变化很快,因此DAC的输入二进制信号为缓变信号。对于这种低频应用,可以将RC时间常数取得较大,以减小噪声。这样,可综合的VHDL语言Delta-Sigma DAC模块配置进EMP7032芯片后,达到了预期的效果。

IP核的分类及特点

IP核的知识产权核心分为三大种类:硬核,中核和软核。硬件中心是知识产权构思的物质表现。这些利于即插即用应用软件并且比其它两种类型核的轻便性和灵活性要差。像硬核一样,中核(有时候也称为半硬核)可以携带许多配置数据,而且可以配置许多不同的应用软件。三者之中最有灵活性的就是软核了,它存在于任何一个网络列表(一列逻辑门位和互相连接而成的集成电路)或者硬件描述语言(HDL)代码中。

IP核的设计原理

软IP内核通常是用某种HDL文本提交用户,它已经过行为级设计优化和功能验证,但其中不含有任何具体的物理信息。据此,用户可以综合出正确的门电路级网表,并可以进行后续结构设计,具有最大的灵活性,可以很容易地借助于EDA综合工具与其他外部逻辑电路结合成一体,根据各种不同的半导体工艺,设计成具有不同性能的器件。可以商品化的软IP内核一般电路结构总门数都在5000门以上。但是,如果后续设计不当,有可能导致整个结果失败。软IP内核又称作虚拟器件。

硬IP内核是基于某种半导体工艺的物理设计,已有固定的拓扑布局和具体工艺,并已经过工艺验证,具有可保证的性能。其提供给用户的形式是电路物理结构掩模版图和全套工艺文件,是可以拿来就用的全套技术。

固IP内核的设计深度则是介于软IP内核和硬IP内核之间,除了完成硬IP内核所有的设计外,还完成了门电路级综合和时序仿真等设计环节。一般以门电路级网表形式提交用户使用。

IP核的总线介绍

为了使IP 核集成更快速、更方便,缩短进入市场的时间,迫切需要一种标准的互联方案,在这一背景下产生的片上总线OCB(on-chip bus)技术。目前,基于IP 核互连的总线结构较有影响力的有三种:IBM公司的Core Connect,ARM 公司的AMBA(Advanced MicrocontrollerBusArchitecture)和SilicoreCorp公司的Wishbone。

1.CoreConnect 总线IBM 公司的CoreConnect 总线提供了三种基本结构:处理器内部总线PLB(Processor Local Bus)、片上外围总线OPB(On-ChipPeripheral Bus)和设备控制总线DCR(Device Control Register)。

(1) PLB 标准是为总线传输的主要发出者和接受者之间提供高带宽、低延迟的连接。其主要特征为: 高性能处理器内部总线;

交叠的读和写功能(最快每周期两次传输); 支持分段传输; 读和写分开; 32~64 位数据总线; 32 位地址空间; 支持16~64 字节突发传输模式; 4 级仲裁优先权; 特殊DMA(Direct Memory Access)模式。

(2) OPB 标准为连接具有不同的总线宽度及时序要求的外设和内存提供了一条途径,并尽量减小对PLB 性能的影响。其主要特性如下: 片上外围总线、支持多个主设备; 32 位地址空间; 读和写数据总线分开; 8~32 位数据总线; 动态总线宽度; 支持重试模式(如果主设备要求的从设备忙,主设备隔一段时间再次请求); 支持突发(burst)传输模式; 支持DMA。

(2) DCR 是用来规范CPU 通用寄存器设备,控制寄存器之间传输数据。DCR 总线在内存地址映射中取消了配置寄存器,减少取操作,增加处理器内部总线的带宽。其主要特征如下: 10 位地址总线; 32 位数据总线; 同步和异步的传输; 分布式结构。

CoreConnect 拥有完备的一整套技术文档,在技术上可行性较强,可以应用在类似于工作站这样的高性能系统的连接,对于简单的嵌入式应用来说可能有点太复杂,提供的许多特性无法用到。

2.AMBA 总线AMBA 总线体系结构定义了2 种总线:AHB(Advanced High-performanceSOC 设计初级培训(Bus)和APB(Advance Peripheral Bus),如图1-2 所示。图1-2 AMBA 总线体系结构(1) AHB 主要用于连接高性能、高吞吐率的设备,完成ARM 芯核与CPU外围部分例如存储通道控制器,DMA 控制器,SPI 接口等的整合。它的主要特性包括: 多控制器; 分段传输; 单周期总线控制权移交; 32~128 位总线宽; 包含一种访问保护机制,用来区别特权访问和无特权访问模式,或指令和数据提取等; 突发传输模式最大为16 节; 访问空间限制在32 位;

支持仲裁、REQ、GNT 和LOCK; 支持字节、半字和字传输。

(2) APB 是专为降低功耗以及接口复杂性而设计的外围互联总线,它常被用于连接一些低带宽、低速传输的外设,主要特征如下: 低性能、低功率外围总线; 单控制器; 32 位地址空间; 32 位数据总线; 分开读和写数据总线。

3.Wishbone 总线Wishbone 总线是Silicore 公司推出的片上总线协议。它的结构极其简单、灵活,又完全公开、完全免费,获得众多支持。主要特征如下: 所有应用使用一个总线体系结构; 支持多控制器; 64 位地址空间; 8~64 位数据总线(可扩展); 单周期读和写; 支持重试; 支持内存映射,FIFO(FISRT IN FIRSTO U T )和十字互连接口; 由终端用户定义仲裁方式。同前2 种总线结构相比,Wishbone 只定义了一种高速总线,在既需要高速总线又需要低速总线的系统中,使用两个Wishbone 接口,比起设计两个不同的接口要简单些。

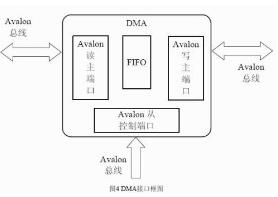

4.Avalon 总线这里,再介绍下将要用到的Avalon 总线。Avalon 总线发布于2000 年的秋天,是Altera 公司针对FPGAs 而设计的一种SOPC 接口标准。它提供了各设备之间连接的接口,可以用于片上处理器和外设之间的连接。Avalon 总线具有支持SOPC,结构简单和可参数化配置等特点。主要特征如下: 32 位地址空间,共计4Gbytes; 所有Avalon 总线信号都是和Avalon 总线时钟同步的,这种设计简化了Avalon 总线的时序行为,便于和高速外设的连接; 地址、数据和控制信号使用独立的端口,以简化外设的设计; Avalon 总线自动为所有外设产生片选信号,简化了Avalon 总线外设的设计; 支持多主设备结构。多个主设备可以共存于Avalon 总线之中,Avalon 总线会自动产生仲裁逻辑; 基于向导的配置。用户可以使用图形化的向导来配置Avalon 总线的相关参数; 动态的总线宽度。Avalon 总线会自动处理不同位宽设备间的信SOC 设计初级培训号,使不同位宽的设备可以顺利通讯;

常用的IP核介绍

众多的IP 提供商包括纯IP 提供商、设计服务公司等都可以向设计者提供各种各样的IP 核。目前,比较着名的IP 提供商包括ARM、Rambus、Synopsys、TTPCom、ParthusCeva、

Virage Logic、Artisan、MIPS、Mentor 和Mosys 等公司。ARM 作为业内领先的32 位嵌入式RISC(Reduced Instruction Set Computer CPU)微处理器解决方案供应商,自1990 年正式成立以来,发展迅速。下面就以ARM 公司为例,进行介绍。ARM 的IP 核技术包括芯片内核、结构延伸、软件开发工具和片上系统解决方案,具有功耗低、性能高、成本低等特点。适用于多种领域,ARM 的用户遍及多个行业,包括:汽车、消费、娱乐、成像、工业、控制、网络、存储、安保和无线应用。ARM 公司的“chipless”模式非常独特,它从不直接介入芯片的生产和销售领域,而是一直以IP 提供者的身份向各大半导体制造商出售知识产权。这种独特的模式,使设计公司、OEM、软件及工具开发公司及制造公司都与ARM结成了合作伙伴关系,使其半导体行业产业链上游的上游,成为许多全球性RISC 标准的缔造者。目前,采用ARM 公司IP 核的半导体公司已多达103 家,包括Intel、TI、Motorola、ST、IBM、ADI、美国国家半导体、Infineon、NEC、LSI 等半导体巨擘,RTOS 软件厂商超过50 家如微软、WindRiver 等公司,EDA工具厂商超过30 家如Cadence、Synopsys 等。ARM 处理器核当前有6 个系列产品ARM7,ARM9,ARM9E,ARM10E,SecurCore 以及ARM11 系列。进一步还包括与其合作伙伴一同研发的产品,如Intel XScale 微体系结构和StrongARM 产品。其中每一类又根据其包含的不同功能模块而分成多种型号。在ARM 内核中常用的四个模块分别用T、D、M 和I 来表示,它们可供生产厂商根据不同用户的需求来选择配置。

(1) T 表示Thumb,该内核可从16 位指令集扩充到32 位ARM 指令集。

(2) D 表示Debug,该内核中包含可用于调试的结构,通常为一个边界扫描链JTAG,以便进入CPU 调试模式,从而进行断点设置、单步调试等工作。

(3) M 表示Multiplier,是8 位乘法器。

(4) I 表示Embedded ICE Logic,包含用于实现断点观测及变量观测的逻辑电路,其中的TAP 控制器可接入到边界扫描链。

1.ARM7

ARM7采用ARMV4T结构,分为三级流水,空间统一的指令与数据Cache,平均功耗为0.6mW/MHz,时钟速度为20MHz~133MHz,每条指令平均需要1.9 个时钟周期,处理速度为0.9MIPS/MHz。其中的ARM710,ARM720 和ARM740 为内带Cache 的ARM 核。ARM 7 的运算速度一般为150DMIPS。ARM7 是小型、快速、低能耗、集成式RISC 内核,广泛应用于手持式计算、数据通信和消费类多媒体。

2.ARM9

ARM9 采用ARMV4T 结构,采用五级流水处理以及分离的Cache 结构,平均功耗为0.7mW/MHz。时钟速度为100MHz~233MHz,每条指令平均需要1.5 个时钟周期,处理速度为1.1MIPS/MHz。其中,ARM920、ARM940 和ARM9E 为含Cache 的CPU 核。性能为132MIPS(120MHz 时钟,3.3V 供)或220MIPS(200MHz 时钟)。ARM 9 的运算速度一般为300DMIPS。ARM9 是低价、低能耗、高性能系统微处理器,配有Cache、内存管理和写缓冲。多应用于高级引擎管理、保安系统、顶置盒、便携计算机和高档打印机。

ARM9E 应该属于ARM10 系列,它也采用了ARMV5TE 结构,其性能得到了大大提高。其中,ARM968E-S(tm)是ARM9E 系列的最新产品,它同时也是ARM9E 系列内核中最小的、最低功耗的产品,可以为网络、汽车、电子消费娱乐品、无线方案等提供理想的技术方案。ARM968E-S 内核含有低延迟的AMBA(tm) AHB-lite 总线接口,内核与DMA 时钟分离, 在闲置状态下的功耗更低。ARM968E-S 内核比ARM966E-S(tm)内核的面积小20%,功耗至少降低10%。延长了电池使用寿命。

3.ARM10

ARM10 采用ARMV5TE 结构,采用六级流水处理,指令与数据分离的Cache 结构。时钟速度为300MHz,每条指令平均需要1.2 个周期。其中ARM1020 为带Cache 的版本。ARM 10 的运算速度一般为500DMIPS。ARM10 速度快,能够支持多种商用操作系统,适用于高性能手持式因特网设备及数字式消费类产品。

3.ARM11

ARM11 采用ARMV6 结构,采用8 级流水处理,动态分支预测与返回堆栈。ARM11 的时钟速度达到550MHz,采用了0.13 微米的工艺技术,支持IEM技术,可以大大减少功耗。ARM 11 的运算速度一般为1000DMIPS。ARM还发布了四个新的ARM11 系列微处理器内核(ARM1156T2-S 内核、ARM1156T2F-S 内核、ARM1176JZ-S 内核和ARM11JZF-S 内核)、应用ARM1176JZ-S 和ARM11JZF-S 内核系列的PrimeXsys 平台、相关的CoreSight技术。

ARM1156T2-S 和ARM1156T2F-S 是首批含有ARM Thumb-2 内核技术的产品,主要用于多种深嵌入式存储器、汽车网络和成像应用产品,提供了更高的CPU 性能和吞吐量,并增加了许多特殊功能,可解决新一代装置的设计难题。它们采用AMBA 3.0 AXI 总线标准,可满足高性能系统的大量数据存取需求。Thumb-2 内核技术结合了16 位、32 位指令集体系结构,提供更低的功耗、更高的性能、更短的编码,该技术提供的软件技术方案较现用的ARM 技术方案减少使用26%的存储空间、较现用的Thumb 技术方案增速25%。ARM1176JZ-S 和ARM1176JZF-S 内核是首批以ARM TrustZone 技术实现手持装置和费电子装置中公开操作系统的超强安全性的产品,同时也是首次对可节约高达75%处理器功耗的ARM 智能能量管理(ARM Intelligent Energy Manager)进行一体化支持。主要为服务供应商和运营商所提供的新一代消费电子装置的电子商务和安全的网络下载提供支持。

4.StrongARM

StrongARM 处理器采用ARMV4T 的五级流水结构,性能较高。它最初是与DEC 联合研制的,后来授权给Intel,Intel 公司用SA110 命名该通用嵌入式标准处理器。该系列还包括SA1100 PDA 系统芯片和SA1500 多媒体处理器芯片。ARM 芯片的选择要根据实际需求而定。例如,如果希望使用WinCE 或Linux 等操作系统以减少软件开发时间,就需要选择ARM720T 以上带有MMU(memory management unit)功能的ARM 芯片,ARM720T、StrongARM、ARM920T、ARM922T、ARM946T 都带有MMU 功能。而ARM7TDMI 没有MMU,不支持Windows CE 和大部分的Linux,但目前有uCLinux 等少数几种Linux 不需要MMU 的支持。

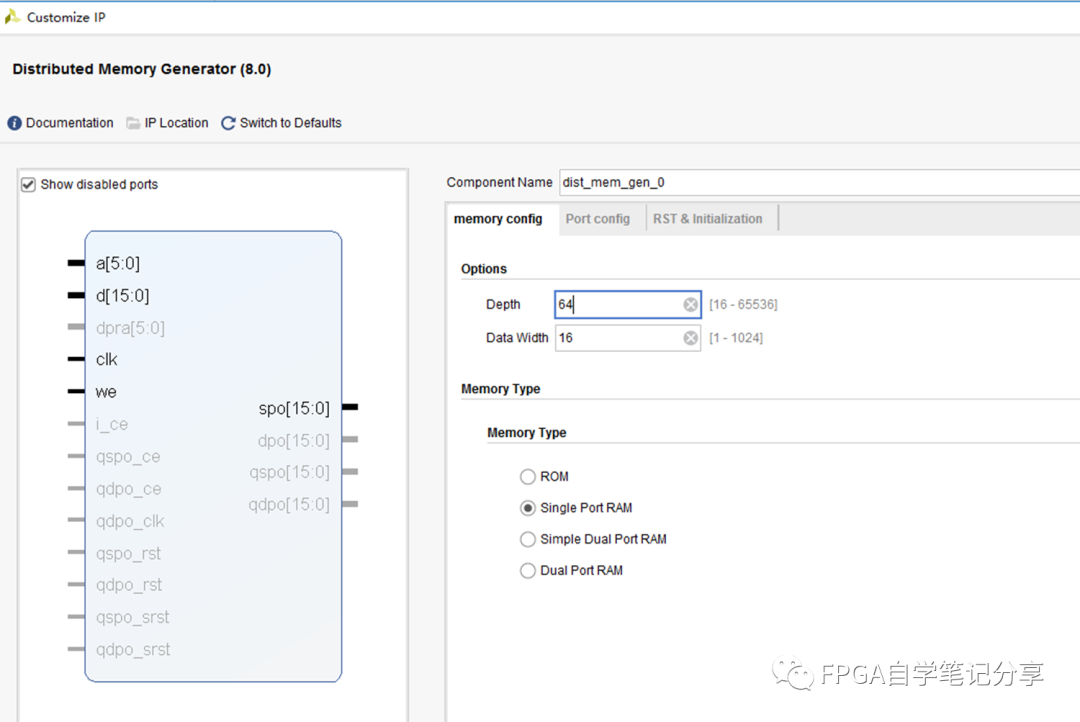

Distributed Memory Generator IP核简介

Distributed Memory Generator IP 核采用 LUT RAM 资源创建各种不同的存储器结构。IP可用来创建只读存储器 (ROM...

LogiCORE JTAG至AXI Master IP核简介

LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI总...

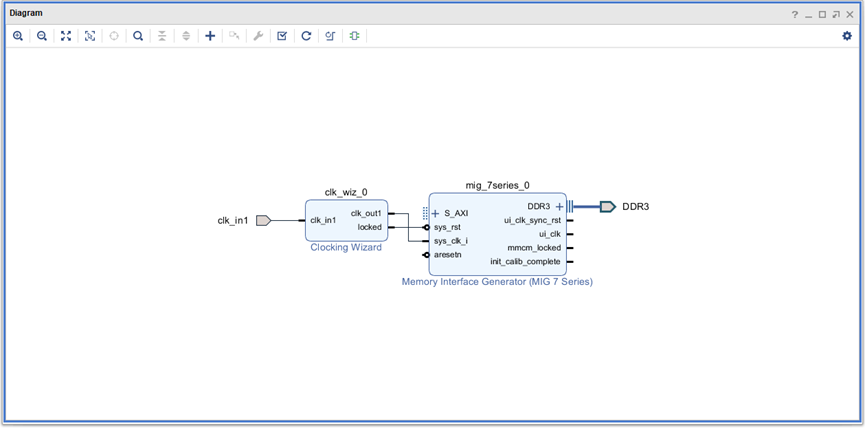

本文介绍一个FPGA 开源项目:Micro Blaze最小系统。MicroBlaze是Xilinx提供的一个软核IP,该软核是由FPGA片内逻辑资源组成...

2023-09-01 标签:fpgaXilinxMicroBlaze 905 0

microblaze IP核使用说明资料合集免费下载立即下载

类别:嵌入式开发 2018-07-20 标签:嵌入式设计microblazeIP核

测试与验证复杂的FPGA设计(2)——如何在虹科的IP核中执行面向全局的仿真

仿真和验证是开发任何高质量的基于FPGA的RTL编码过程的基础。在上一篇文章中,我们介绍了面向实体/块的仿真,即通过在每个输入信号上生成激励并验证RTL...

虹科方案 | 确定性HSR交换机IP核,基于硬件的专用解决方案

IP核(IntellectualPropertycore)是一段具有特定电路功能的硬件描述语言程序,常常被用于数字电路中。该程序与集成电路工艺无关,可以...

虹科方案 | 虹科UES IP核——用最少的资源,解决最大的吞吐量!

IP核(IntellectualPropertycore)是一段具有特定电路功能的硬件描述语言程序,常常被用于数字电路中。该程序与集成电路的工艺无关,可...

2022-04-14 标签:IP核 505 0

近日,成都市新经济发展委员会公示了《2022年度成都市新经济梯度培育企业名单》,锐成芯微获评新经济示范企业,并以领先的“核芯”能力和经济效应位列前30强。

深圳发布激励政策 突破CPU/GPU/FPGA等高端芯片可奖励1000万

近日,深圳发布了《深圳市关于促进半导体与集成电路产业高质量发展的若干措施(征求意见稿)》,传递了怎样的中国芯片打法? 美国芯片法案连番限制之...

IP核的开发过程中,面临着许多关键技术,比如IP核的规格定义、基于接口的设计、IP核测试存取结构标准、IP核的验证与打包等。对于IP核的验证,主要是建立...

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |