资料介绍

本文档的主要内容详细介绍的是三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料主要内容包括了:1 ModelSimSE的使用流程,2 一个Verilog计数器仿真详细流程附源代码,3 一个VHDL计数器仿真详细流程附源代码,4 Force和run两个cmd指令详细解释,5 Do文件的使用和编写例子,6 网上下载ModelSimXE调试Verilog TestBench的一个例子,HDL语言的INOUT端口仿真暨三态门仿真,VerilogHDL 的三态门实现与仿真,ARM 总线的三态门实现与仿真

三态门是FPGA 编程开发中经常遇到的一个问题。一个典型的应用就是TI 的DSP 的EMIF 总线。针对HDL 语言的三态门应用示例和仿真示例在网上很多,但是往往只讲述一种语言的,没有给予两种语言下三态门的一个综合评述,如讲述二者使用、仿真时的区别等。特别是VerilogHDL 语言下的三态门仿真,很多讲述都是语焉不详,包括使用Force 语句等,这些使用人手工干预的仿真方法明显违背了EDA 自动化的宗旨,是使用者对其仿真方法不明确的情况下的一种权益之计。

本文将使用一个DSP EMIF 接口逻辑的例子,详细讲述:

(0)什么叫做Z 态?三态的晶体管级实现是怎样的?

(1)VHDL 语言下同步、异步三态门的实现和仿真;

(2)VerilogHDL 语言下同步、异步三态门的实现和仿真;

(3)Verilog 下ARM 三态总线的仿真实例;

(4)综述两种语言下仿真的要点。

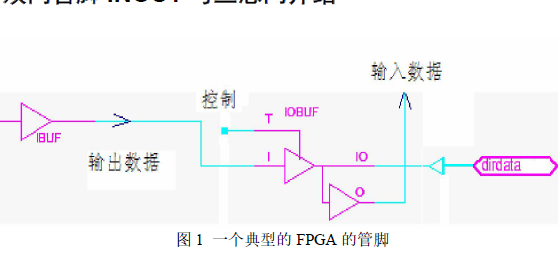

由图1 可以看出,一个FPGA 的管脚由一个输入缓冲器和一个三态输出缓冲器构成。三态输出缓冲器,即三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。高阻态相当于隔断状态(电阻很大,相当于开路)。 三态门都有一个EN 控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态。准确来讲,三态的高阻态(Z 态)指的就是门的输出脚的两个驱动TTL 或MOS 管都处于截止状态时的输出状态。参考图2、图3 和图4 有更详细的理解。

- 如何使用 ModelSim 进行设计仿真 0次下载

- Modelsim与MATLAB的联合仿真 33次下载

- C语言与VB语言联合在Proteus上的仿真资料合集 9次下载

- HDL仿真软件Modelsim的安装教程资料免费下载 7次下载

- ModelSim 10.1a版本经典教程资料免费下载 0次下载

- Modelsim仿真教程Modelsim的基础入门基础教程免费下载 23次下载

- modelsim仿真使用教程资料免费下载 6次下载

- MODELSIM仿真(适合xilinx ISE) 8次下载

- 三态门总线传输电路的Multisim仿真方案 48次下载

- Altera ModelSim 6.5仿真入门教程 255次下载

- 基于FPGA的SDX总线与Wishbone总线接口设计 25次下载

- 使用 ModelSim 进行设计仿真 132次下载

- 使用ModelSim进行设计仿真 151次下载

- Verilog HDL入门教程(华为绝密资料) 0次下载

- 基于ISE的modelsim的后仿真方法 112次下载

- 怎样单独使用modelsim仿真xilinx呢? 479次阅读

- modelsim自动化仿真实验 利用脚本实现modelsim自动化仿真 941次阅读

- 浅析Modelsim的仿真步骤 1284次阅读

- 通用HDL的技术特性 625次阅读

- 使用ModelSim软件进行时序仿真 896次阅读

- ModelSim手动仿真教程 4460次阅读

- 三态门总线传输电路的工作特性及仿真研究 6800次阅读

- ModelSim仿真器的主要特点以及用法解析 3529次阅读

- 仿真软件ModelSim及其应用,ModelSim的仿真流程 9228次阅读

- 一文详解ModelSim仿真具体流程 3126次阅读

- 关于quartus如何调用modelsim详细解说 3.4w次阅读

- modelsim仿真详细过程(功能仿真与时序仿真) 6.3w次阅读

- Xilinx ISE是如何调用ModelSim进行仿真的 1w次阅读

- 减少Xilinx Ise与Modelsim联合仿真的错误方法 1349次阅读

- 基于FPGA的ARM并行总线设计与仿真分析 7211次阅读

下载排行

本周

- 1电子电路原理第七版PDF电子教材免费下载

- 0.00 MB | 1491次下载 | 免费

- 2单片机典型实例介绍

- 18.19 MB | 95次下载 | 1 积分

- 3S7-200PLC编程实例详细资料

- 1.17 MB | 27次下载 | 1 积分

- 4笔记本电脑主板的元件识别和讲解说明

- 4.28 MB | 18次下载 | 4 积分

- 5开关电源原理及各功能电路详解

- 0.38 MB | 11次下载 | 免费

- 6100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 7基于单片机和 SG3525的程控开关电源设计

- 0.23 MB | 4次下载 | 免费

- 8基于AT89C2051/4051单片机编程器的实验

- 0.11 MB | 4次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 2PADS 9.0 2009最新版 -下载

- 0.00 MB | 66304次下载 | 免费

- 3protel99下载protel99软件下载(中文版)

- 0.00 MB | 51209次下载 | 免费

- 4LabView 8.0 专业版下载 (3CD完整版)

- 0.00 MB | 51043次下载 | 免费

- 5555集成电路应用800例(新编版)

- 0.00 MB | 33562次下载 | 免费

- 6接口电路图大全

- 未知 | 30320次下载 | 免费

- 7Multisim 10下载Multisim 10 中文版

- 0.00 MB | 28588次下载 | 免费

- 8开关电源设计实例指南

- 未知 | 21539次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935053次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537793次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191183次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183277次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138039次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论