器件中的高功耗虽然是可以容忍的,但是在设计过程中,我们往往都在追求低功耗实现。上篇文章中,小编对MCU的低功耗设计有所解读。为增进大家对功耗的了解程度,本文将对寄存器传输级低功耗设计方法予以介绍。

除了芯片的速度和面积等,人们对低功耗的期望也越来越高,因而在IC设计中加入低功耗设计非常必要。寄存器传输级的低功耗设计对降低整个芯片的功耗作用非常显著,本文讨论的三种寄存器传输级低功耗设计方法,经验证对动态功耗的降低很有效。

自集成电路问世以来,设计者在单个芯片上集成的晶体管的数量呈现出令人惊讶的增长速度。近30年,集成电路的发展一直遵循着“摩尔定律”:集成在芯片上的晶体管的数量每18个月就翻一番,芯片成本也相应下降。

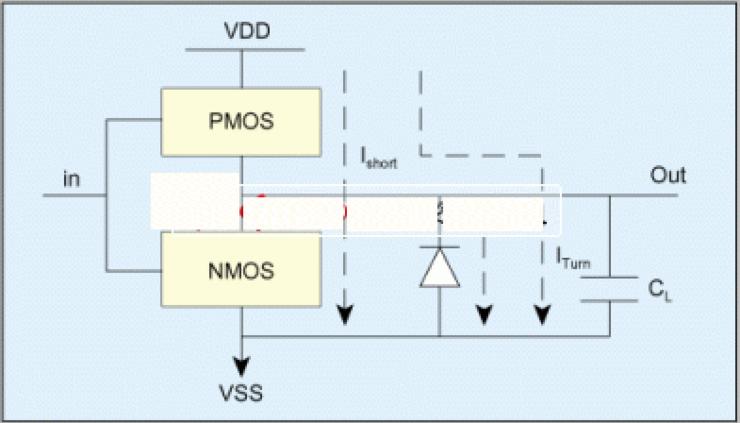

图1:CMOS电路功耗的主要来源是动态功耗,由开关电流和短路电流造成

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频

上传资料赚积分

上传资料赚积分

评论