资料介绍

STA分析是基于同步电路设计模型的,在数据输入端,假设外部也是同时钟的寄存器的输出并且经过若干组合逻辑进入本级,而输出也被认为是驱动后一级的同时钟的寄存器。在不设置约束的情况下,纯组合逻辑的输入-》输出不得超过一个T,否则也会被认为是Timing violation.

1. Timing path

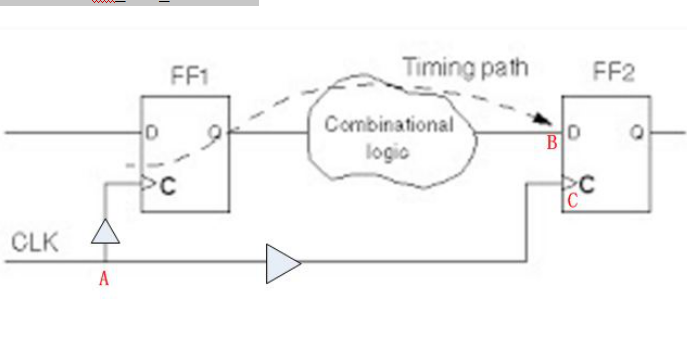

Timing path就是时间线。Timing就是从起始位置的时间点到终点位置的时间点之间的时间长度。Path是指跟位置相关,即时间起始或终点的位置。Timing path就是某位置的某一时间点到另一位置的某个时间点。对于DFF来说,上升沿类似于一瞬间的脉冲,只有在这短短的一瞬间,数据才允许通过。对于DFF来说,有两个输入点:数据D和时钟CK,有一个输出点:数据Q。由于是时间比较,所以对于D和CK一定要有一个共同的起始时间点,如下图中的A点出现clk上升沿的时刻。如下图,假设我们分析DFF2的数据和时钟到达的时间。二者共同的出发点是A的上升沿,因为A位于时钟通路上,FF1的时钟经过A点到达FF1-C点,在FF1-C上升沿打开FF1,然后数据才能从FF1-Q输出,进而传递到FF2-D。在A点, FF2的时钟沿经过clock tree,达到FF2-C点。所以数据走过的路程是:

Data path: A-》clk_tree_buf1-》FF1-C -》 FF1-Q -》 Comb_logic -》 B

而对于FF2来说只要满足下个周期的上升沿能够采样即可,所以时钟到达FF2-C的路径是:

Clk path: A -》 clk_tree_buf2-》 C.

- AN79-30纳秒精密宽带放大器建立时间测量 7次下载

- 宽带放大器的128-2纳秒、1%分辨率的建立时间测量 6次下载

- AN-359:运算放大器的建立时间 3次下载

- AN10-运算放大器建立时间的测量方法 2次下载

- AN-256:准确测试运算放大器建立时间 1次下载

- FPGA中毛刺的讨论和可靠性有关的几个概念详细说明 19次下载

- FPGA的经典面试题和解答 11次下载

- FPGA设计中有哪些基本问题学习课件详细说明 4次下载

- 如何计算多路复用器的建立时间和采样速率 0次下载

- 数字电路FPGA笔试大全 92次下载

- 最全的硬件工程师笔试试题集 5319次下载

- 精确测算ADC驱动电路建立时间 39次下载

- 如何处理建立保持(Setuphold)时间 31次下载

- 快速建立时间的自适应锁相环 20次下载

- 计算开关电容ADC的建立时间 24次下载

- 关于建立时间和保持时间的测量方法 701次阅读

- 浅析D触发器的建立时间和保持时间物理含义 353次阅读

- 建立时间和保持时间对数字电路的影响 332次阅读

- SOC设计中的建立时间和保持时间 391次阅读

- 为什么setup检查下一个沿而hold检查当前沿 2720次阅读

- 如何读懂时序分析报告 2698次阅读

- 放大器的建立时间介绍 5258次阅读

- FPGA的时钟设计:如何建立时间与保持时间 4551次阅读

- 一文详解时序的基本概念 3.5w次阅读

- FPGA建立时间和保持时间详解 5601次阅读

- 静态时序分析基础 3581次阅读

- 怎样利用FPGA设计一个跨时钟域的同步策略? 1682次阅读

- 动态参数:压摆率跟建立时间到底什么? 5294次阅读

- FPGA关键设计:时序设计 4150次阅读

- 使用采样保持技术实现运算放大器建立时间测定 1035次阅读

下载排行

本周

- 1TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 2开关电源基础知识

- 5.73 MB | 11次下载 | 免费

- 3嵌入式linux-聊天程序设计

- 0.60 MB | 3次下载 | 免费

- 4DIY动手组装LED电子显示屏

- 0.98 MB | 3次下载 | 免费

- 5基于FPGA的C8051F单片机开发板设计

- 0.70 MB | 2次下载 | 免费

- 651单片机窗帘控制器仿真程序

- 1.93 MB | 2次下载 | 免费

- 751单片机PM2.5检测系统程序

- 0.83 MB | 2次下载 | 免费

- 8基于51单片机的RGB调色灯程序仿真

- 0.86 MB | 2次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537798次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191186次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论