资料介绍

1. 产生一个高电平持续时间和低电平持续时间分别为3 ns和10 ns的时钟。

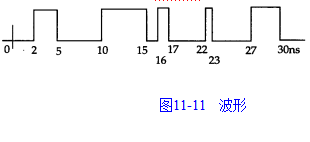

2. 编写一个产生图11 - 11所示波形的Verilog HDL模型。

3. 产生一个时钟C l o c k V,该时钟是模块G e n C l k D中描述的时钟C l k D(如图11 - 6所示)的相移时钟,相位延迟为15 ns 。[提示:用连续赋值语句可能会不合适。]

4. 编写测试时序检测器的测试验证程序。时序列检测器按模式1 0 0 1 0在每个时钟正沿检查输入数据流。如果找到该模式,将输出置为1;否则输出置为0。

5. 编写一个模块生成两个时钟, C l o c k A和C l o c k B。C l o c k A 延迟10 ns后有效,C l o c k B延迟4 0n s后有效。两个时钟有相同的高、低电平持续时间,高电平持续时间为1 ns,低电平持续时间为2 n s。C l o c k B与时钟C l o c k A边沿同步,但极性相反。

6. 描述4位加法/减法器的行为模型。用测试验证模块测试该模型。在测试验证模块内描述所有输入激励及其期望的输出值。将输入激励、期望的输出结果和监控输出结果转储到文本文件中。

7. 描述在两个4位操作数上执行所有关系操作(《, 《=, 》, 》=)的A L U。编写一个从文本文件中读取测试模式和期望结果的测试验证模块。

8. 编写一个对输入向量作算术移位操作的模块。指定输入长度用参数表示,缺省值为3 2。同时指定移位次数用参数表示,缺省值为1。编写一个模拟、测试模块以验证对1 2位向量进行8次移位算术操作的正确性。

9. 编写N倍时钟倍频器模型。输入是频率未知的参考时钟。输出时钟的倍数与参考时钟的每个正沿同步。[提示:确定参考时钟的时钟周期。

10. 编写一个模型,显示输入时钟每次由0转换到1的时间。

- Java编程思想练习题源码 0次下载

- Thinking In Java练习题源码 0次下载

- 复变函数与积分变换练习题及解答 4次下载

- Matlab神经网络的学习练习题合集免费下载 13次下载

- 高频电子线路的经典练习题库资料免费下载 8次下载

- Python的练习题实例免费下载 17次下载

- LabVIEW编程的定时练习题和答案免费下载 31次下载

- C语言程序设计上机考试练习题和答案免费下载 12次下载

- C语言编程的经典练习题资料免费下载 16次下载

- 维修电工科技信息检索练习题及课件 1次下载

- 子网划分练习题 0次下载

- 高频谐振练习题 1次下载

- labview论坛-labview经典基础练习题+解答 642次下载

- Verilog HDL练习题 193次下载

- 电容器练习题 50次下载

- 例说Verilog HDL和VHDL区别 473次阅读

- 浅谈Verilog HDL代码编写风格 265次阅读

- 二十进制编码器及Verilog HDL描述 Verilog HDL程序的基本结构及特点 1117次阅读

- Verilog的程序框架案例 1212次阅读

- 使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计 1170次阅读

- Verilog HDL指定用户定义原语UDP的能力 735次阅读

- Verilog HDL和VHDL的区别 1.2w次阅读

- verilog是什么_verilog的用途和特征是什么 4.3w次阅读

- vhdl和verilog的区别_vhdl和verilog哪个好? 12.1w次阅读

- verilog语言基本语句_verilog语言词汇大全 9.4w次阅读

- Verilog的语言要素 1714次阅读

- Verilog HDL简明教程(2) 1117次阅读

- Verilog HDL简明教程(part1) 1132次阅读

- 初学者学习Verilog HDL的步骤和经验技巧 3.5w次阅读

- Verilog HDL语言的文件调用问题:include使用方法介绍 6412次阅读

下载排行

本周

- 1TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 2开关电源基础知识

- 5.73 MB | 6次下载 | 免费

- 3100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 4嵌入式linux-聊天程序设计

- 0.60 MB | 3次下载 | 免费

- 5基于FPGA的光纤通信系统的设计与实现

- 0.61 MB | 2次下载 | 免费

- 6基于FPGA的C8051F单片机开发板设计

- 0.70 MB | 2次下载 | 免费

- 751单片机窗帘控制器仿真程序

- 1.93 MB | 2次下载 | 免费

- 8基于51单片机的RGB调色灯程序仿真

- 0.86 MB | 2次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33564次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21548次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6653次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537796次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191185次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183278次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论