资料介绍

Introduction

Each system has different requirements when it comes to interfacing to an audio codec ASI. The most common configurations are the master and slave modes. When the audio codec ASI is configured in master mode, its bit clock (BCLK) and word clock (WCLK) pins are output. In slave mode, BCLK and WCLK are inputs to the codec ASI. This relationship might seem straightforward. However, care must be taken when the ASI is configured in slave mode to ensure that the oversampled data that are decimated always fall within the correct target rate time slot.

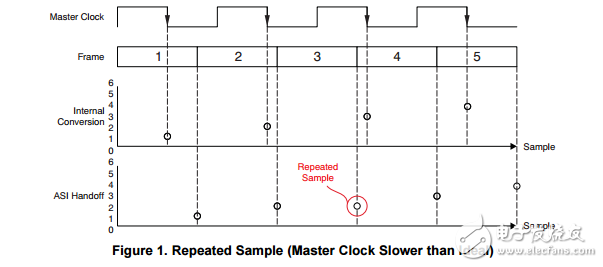

If a master clock is a free-running clock and it is fed to a converter, it will not be frequency-locked to the frame clock (WCLK) of an independent ASI. Any deviation from the ideal will eventually result in a skipped or repeated sample (assuming that the architecture repeats samples)。 For example, if a host processor provides an ideal 48-kHz WCLK with respect to absolute time, its respective ideal master clock could be exactly (128 ● WCLK) = 6.144 MHz. If a master clock from a non-ideal crystal is provided directly to the converter modulator with a 0.001% error, this clock could result in 6.14393856 MHz. Eventually this slower clock will result in a repeated sample out of the ASI bus. Of course, there is no such thing as an ideal master or ASI clocks.

Figure 1 illustrates a simplified case in which a hypothetical analog-to-digital converter (ADC) operating at Nyquist frequency (for simplification purposes) results in a duplicated sample on the ASI bus. In this example, the hypothetical converter ideally hands over its data on the middle of a frame on the falling edge of the master clock. These data should then be ready to be transferred in the beginning of the next frame. As shown in Figure 1, the master clock is actually slower than the ideal. This configuration will eventually drift the clock enough (with respect to the ASI frame) such that there will be a frame that will not receive new data (as shown at the end of frame #3

- EVAL-BUDO-EXXT Blackfin Audio扩展板是一款用于EZ-Board的低成本、插入式扩展板。 该扩展板与多达三个音频编解码器相连,包括两个模拟音频编解码器和一个采用数字索尼飞利浦数字接口(SPDIF)音频接口的双通道模拟/数字音频编解码器,从而扩展Black 5次下载

- 将音频编解码器整合进SoC的设计方案 16次下载

- EVAL-SSM2602:音频编解码器评估板 8次下载

- AN-1323:高性能数字MEMS麦克风与SigmaDSP音频编解码器的简单接口 4次下载

- AD1882A高保真音频MAX编解码器 2次下载

- SSM2602: 低功耗音频编解码器 0次下载

- AC97音频编解码器的规格标准免费下载 1次下载

- 音频编解码器的音频串行接口配置 9次下载

- TI语音频带编解码器的比较电话应用 7次下载

- 音频串行接口配置音频编解码器 15次下载

- 用于音频编解码器的带外噪声测量问题 9次下载

- 音频编解码器串行接口配置 5次下载

- NEON音频编解码器优化技术 26次下载

- AD1847串行端口音频编解码器如何与并行总线接口的实例 27次下载

- AD1847串行端口音频编解码器如何与并行总线接口的实例 25次下载

- MAXQ3120在编解码应用中的应用 439次阅读

- 音频编解码器的作用、选择要点及使用技巧 7177次阅读

- 新唐科技NAU8820解码器简介 1448次阅读

- 新唐科技NAU8822L解码器简介 3960次阅读

- 新唐科技立体声编解码器系列介绍 1274次阅读

- 新唐科技音频编解码器简介 1370次阅读

- 新唐科技语音频段编解码器简介 2029次阅读

- 微雪电子树莓派音频编解码扩展板|WM8960 Audio HAT介绍 4314次阅读

- 关于音频编解码器EVS及用好要做的准备工作详解 5560次阅读

- 分析了各主流编解码器的优势与不足,并对编解码器的选择给出建议 1.3w次阅读

- 宋利:解读了编解码器的现状与未来趋势 8656次阅读

- 音频放大电路图锦集 4.7w次阅读

- MAX98090超低功耗音频编解码器 2148次阅读

- Skype TV和远端扬声器的音频电路配置 2214次阅读

- 音频编解码器技术 4774次阅读

下载排行

本周

- 1TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 2开关电源基础知识

- 5.73 MB | 11次下载 | 免费

- 3100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 4嵌入式linux-聊天程序设计

- 0.60 MB | 3次下载 | 免费

- 5DIY动手组装LED电子显示屏

- 0.98 MB | 3次下载 | 免费

- 651单片机大棚环境控制器仿真程序

- 1.10 MB | 2次下载 | 免费

- 751单片机PM2.5检测系统程序

- 0.83 MB | 2次下载 | 免费

- 8TP4055-500mA线性锂离子电池充电器数据手册

- 0.27 MB | 2次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537797次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191186次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论