资料介绍

一、有限状态机

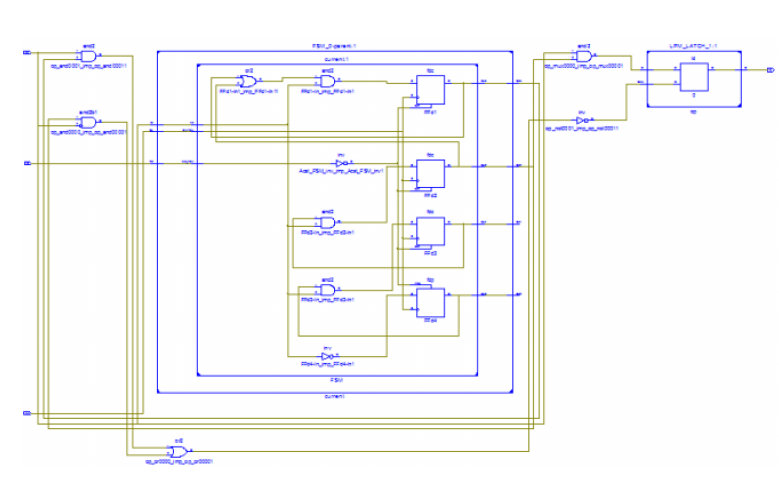

有限状态机是绝大部分控制电路的核心结构, 是表示有限个状态以及在这些状态之间转移和动作等行为的数学模型。有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。一般来说, 除了输入部分和输出部分外, 有限状态机还含有一组具有“记忆”功能的寄存器, 这些寄存器的功能是记忆有限状态机的内部状态, 它们常被称为状态寄存器。在有限状态机中, 状态寄存器的的下一个状态不仅与输入信号有关, 而且还与该寄存器的当前状态有关, 因此有限状态机又可以认为是组合逻辑和寄存器逻辑的一种组合。

在实际的应用中, 根据有限状态机是否使用输入信号, 可将其分为Moore 型有限状态机和Mealy 型有限状态机两种类型。Moore 型有限状态机其输出信号仅与当前状态有关,即可以把Moore 型有限状态的输出看成是当前状态的函数。Mealy 型有限状态机其输出信号不仅与当前状态有关,而且还与所有的输入信号有关,即可以把Mealy 型有限状态机的输出看成是当前状态和所有输入信号的函数。

- 基于有限状态机的车身防盗报警的实现 0次下载

- 如何以面向对象的思想设计有限状态机 4次下载

- STM32实现按键有限状态机(超详细,易移植) 25次下载

- 有限状态机设计是HDL Designer Series的关键应用 3次下载

- 基于有限状态机的Linux多点触摸屏驱动设计刘斌 0次下载

- 基于有限状态机的五桥臂逆变器改进调制策略_梅杨 0次下载

- 有限状态机在嵌入式软件中的应用 27次下载

- VHDL有限状态机设计-ST 3次下载

- 有限状态机_FSM_的实现 0次下载

- 有限状态机FSM在PLD中的实现分析 3次下载

- 有限状态机在嵌入式系统中的实现及应用 1次下载

- 有限状态机的建模与优化设计 1次下载

- 基于VHDL的MTM总线主模块有限状态机设计 20次下载

- 一种改进的遗传算法进化有限状态机 18次下载

- fsm有限状态机pdf 75次下载

- 什么是有限状态机?如何解决传统有限状态机「状态爆炸」问题? 648次阅读

- SaberRD状态机建模工具介绍(一)什么是状态机建模 431次阅读

- 什么是状态机?状态机的种类与实现 3491次阅读

- 一个基于事件驱动的有限状态机 450次阅读

- 基于事件驱动的有限状态机介绍 712次阅读

- 如何构建基于状态机的软件系统 1246次阅读

- 如何在Verilog中创建有限状态机 2865次阅读

- 摩尔型状态机与米利型状态机的区别是什么 1.2w次阅读

- 基于有限状态机的FlexRay时钟同步机制 2911次阅读

- 状态机常见的3种类型 状态机案例设计 7845次阅读

- 使用层次型有限状态机对售货机控制器实现改造设计 2403次阅读

- 状态机和组合逻辑的冒险竞争浅析 3639次阅读

- 利用74LS161实现复杂状态机 8305次阅读

- 初学者对有限状态机(FSM)的设计的认识 3882次阅读

- FPGA工程师:如何在FPGA中实现状态机? 1.2w次阅读

下载排行

本周

- 1电子电路原理第七版PDF电子教材免费下载

- 0.00 MB | 1491次下载 | 免费

- 2单片机典型实例介绍

- 18.19 MB | 95次下载 | 1 积分

- 3S7-200PLC编程实例详细资料

- 1.17 MB | 27次下载 | 1 积分

- 4笔记本电脑主板的元件识别和讲解说明

- 4.28 MB | 18次下载 | 4 积分

- 5开关电源原理及各功能电路详解

- 0.38 MB | 11次下载 | 免费

- 6100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 7基于单片机和 SG3525的程控开关电源设计

- 0.23 MB | 4次下载 | 免费

- 8基于AT89C2051/4051单片机编程器的实验

- 0.11 MB | 4次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 2PADS 9.0 2009最新版 -下载

- 0.00 MB | 66304次下载 | 免费

- 3protel99下载protel99软件下载(中文版)

- 0.00 MB | 51209次下载 | 免费

- 4LabView 8.0 专业版下载 (3CD完整版)

- 0.00 MB | 51043次下载 | 免费

- 5555集成电路应用800例(新编版)

- 0.00 MB | 33562次下载 | 免费

- 6接口电路图大全

- 未知 | 30320次下载 | 免费

- 7Multisim 10下载Multisim 10 中文版

- 0.00 MB | 28588次下载 | 免费

- 8开关电源设计实例指南

- 未知 | 21539次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935053次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537793次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191183次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183277次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138039次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论