资料介绍

Altium Designer 6以强大的设计输入功能为特点,在FPGA和板级设计中,同时支持原理图输入和HDL硬件描述输入模式;同时支持基于VHDL的设计仿真,混合信号电路仿真、布局前/后信号完整性分析。 Altium Designer 6的布局布线采用完全规则驱动模式,并且在PCB布线中采用了无网格的SitusTM拓扑逻辑自动布线功能;同时,将完整的CAM输出功能的编辑结合在-起。Altium Designer 6是两年之内的第六次更新,极大地增强了对高密板设计的支持,可用于高速数字信号设计,提供大量新功能和改进,改善了对复杂多层板卡的管理和导航,可将器件放置在PCB板的正反两面,处理高密度封装技术,如高密度引脚数量的球型网格阵列(BGAs)。

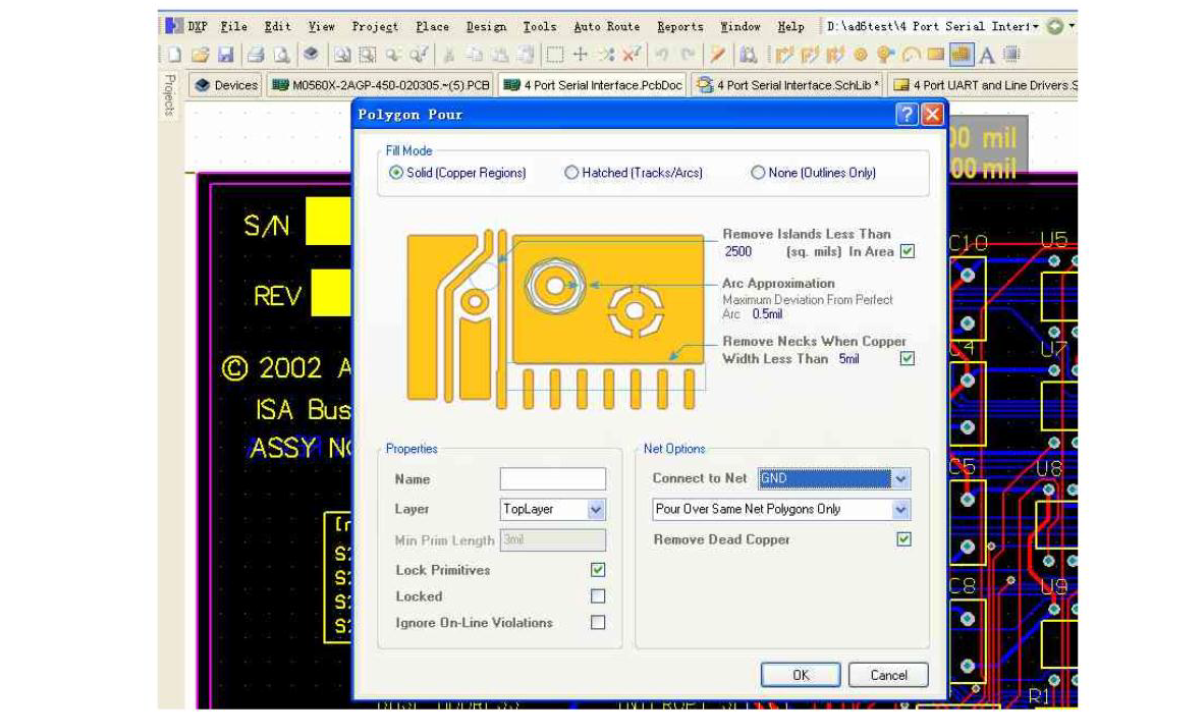

在PCB设计完成后,为了加强抗干扰性,我们会经常进行-些铺铜操作,并且有时要求设定铺铜区域的安全间距与PCB布线的安全间距不一样,我们可以通过以下两种方式来实现:

一,通过铺铜管理器来实现

我们通过菜单上的快捷键来进行铺铜操作,可以选择实心铺铜或网格铺铜的模式,然后在Netoptions下的ConnecttoNet选择连接到合适的网络,一般连接到GND网络,同时般可以选中下面的移除死铜菜单,然后在合适的区域内进行铺铜的操作

- 板对板连接器0.8间距公母座 1次下载

- PCB设计中都有哪些间距需要考虑资料下载 8次下载

- PCB设计安全间距的两类问题资料下载 21次下载

- 结构化区域全卷积神经网络的深度学习模型 3次下载

- PCB设计中的安全间距问题资料下载 30次下载

- PCB小间距QFN封装引入串扰的抑制方法资料下载 11次下载

- PCB设计中的安全距离相关要求 0次下载

- 如何才能在IAR中打包文件详细方法说明 15次下载

- 如何才能在Linux系统下搭建51单片机的开发烧写环境 0次下载

- PCB设计的常见技巧详细资料说明 3次下载

- Allegro PCB设计完后要处理哪些方面的问题? 0次下载

- 如何在PCB下设定不同的铺铜区域安全间距及切铜 0次下载

- PCB走线之安全间距到底是多少 0次下载

- 如何在PCB下设定不同的铺铜区域安全间距及切铜 0次下载

- PCB安全距离详解 0次下载

- 汽车线束防水区域划分及防水等级设定 477次阅读

- PCB设计孔间距的DFM可靠性,你知道吗? 716次阅读

- 从焊接角度谈下设计PCB的5个建议 603次阅读

- 如何才能怎样做一块好的PCB板 2366次阅读

- 做才能让数据更安全?数据库的安全策略 3429次阅读

- SMT贴片元器件最小间距的要求与设计 3.5w次阅读

- 波峰焊其热作用的过程区域作用有哪些 4038次阅读

- PCB设计中由小间距QFN封装引入串扰的抑制方法分析 1044次阅读

- pcb不同的安全间距设置 6538次阅读

- PCB拼板的10个秘密 2629次阅读

- AD17的PCB文件怎么才能在pads中比较完整的打开? 1.4w次阅读

- PCB规则之AD高级间距规则 5.2w次阅读

- AD如何在PCB中设定铺铜区域的安全间距及切铜? 3.9w次阅读

- PCB设计后期检查的六个重点 616次阅读

- 怎样才能做出一块好的PCB板? 2036次阅读

下载排行

本周

- 1电子电路原理第七版PDF电子教材免费下载

- 0.00 MB | 1497次下载 | 免费

- 2TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 3单片机典型实例介绍

- 18.19 MB | 103次下载 | 1 积分

- 4S7-200PLC编程实例详细资料

- 1.17 MB | 28次下载 | 1 积分

- 5笔记本电脑主板的元件识别和讲解说明

- 4.28 MB | 18次下载 | 4 积分

- 6开关电源原理及各功能电路详解

- 0.38 MB | 15次下载 | 免费

- 79天练会电子电路识图

- 5.91 MB | 6次下载 | 免费

- 8100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234314次下载 | 免费

- 2PADS 9.0 2009最新版 -下载

- 0.00 MB | 66304次下载 | 免费

- 3protel99下载protel99软件下载(中文版)

- 0.00 MB | 51209次下载 | 免费

- 4LabView 8.0 专业版下载 (3CD完整版)

- 0.00 MB | 51043次下载 | 免费

- 5555集成电路应用800例(新编版)

- 0.00 MB | 33564次下载 | 免费

- 6接口电路图大全

- 未知 | 30321次下载 | 免费

- 7Multisim 10下载Multisim 10 中文版

- 0.00 MB | 28588次下载 | 免费

- 8开关电源设计实例指南

- 未知 | 21540次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537794次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234314次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191183次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183278次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138039次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论