CAN是事件触发的通信协议,它用标识符(ID)的无损仲裁方法调度不同消息的传送。仲裁依靠的是位值,因此位值采样准确性很重要。为在所有节点得到相同的准确的采样,位时间的同步就是关键。正常传送中也要克服节点间时钟差造成的采样点变动,减少读出时的错误。但是位时间能否实现同步,取决于时钟的偏差。为此CAN标准规定了时钟容差的计算方法。现在发现,标准规定的计算公式不够用,它会影响应用的可靠性。特别是汽车工业常用的标准儿939是基于CAN 2.0B的,时钟容差对CAN 2.OB的影响较大,因此对此加以修正非常重要。对于标准的完整理解不仅与应用有直接关系,对进一步提高CAN性能也会有新的启示。

1 ISO 1 1898-1:2003关于时钟容差的规定

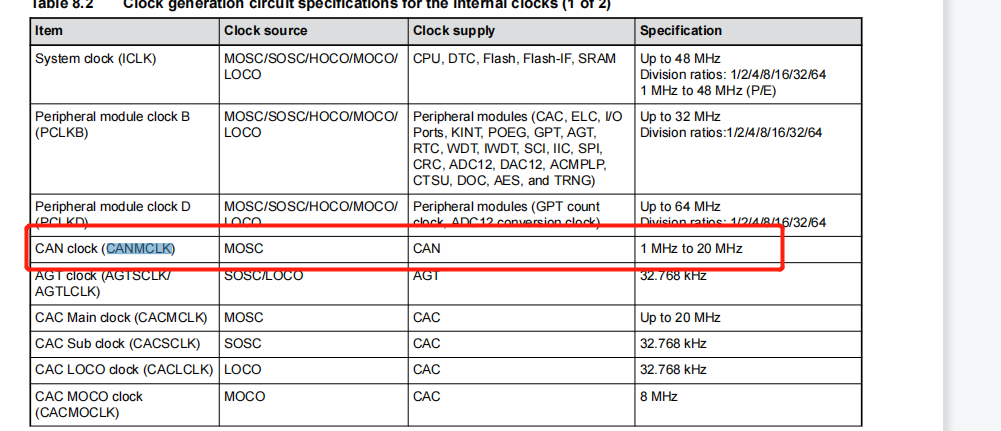

ISO 11898-1:2003第12.4.1.2款规定位时间单位为Tq,它是可组态的参数。1位共有NTQ(8~25)个Tq,Tq由振荡器分频而得,受硬件的振荡器与分频器资源所限,其选择有限。每1位分成4段:同步段S(Tq)、传输段Pr(Tq~8Tq)、缓冲1段P1(Tq~8Tq)和缓冲2段 P2(Tq~8 Tq),它们都是可组态的参数。位值的采样在P1与P2的分界处。CAN将同步分为2种:硬同步和重同步。总线空闲时开始新帧SOF的隐位到显位的跳变沿 (R/D跳变沿)引起硬同步,立即复位本地位时间到S段。在帧传送中的R/D跳变沿引起重同步,跳变沿落在上一位采样后的P2段时将该P2缩短,跳变沿落在S后时加长本位P1的长度,此时本地位时间修正的最大绝对量不超过SJW(重同步跳转宽度)的值。SJW是1个组态参数,在Tq~4 Tq之间。关于CAN位时间与同步的一些较为深入的探讨可参见参考文献。

在CAN标准中,采用振荡器容差这一术语来代表时钟容差。实际实现时,有的实现方案用振荡器加锁相环构成时钟,此时CAN的时钟偏差就由2部分构成。为了与标准文字一致,本文不把时钟容差与振荡器容差严格区分。将振荡器的频率相对误差表示为△,时,按ISO11898-1的12.4.2.5款规定,它的约束有2条。

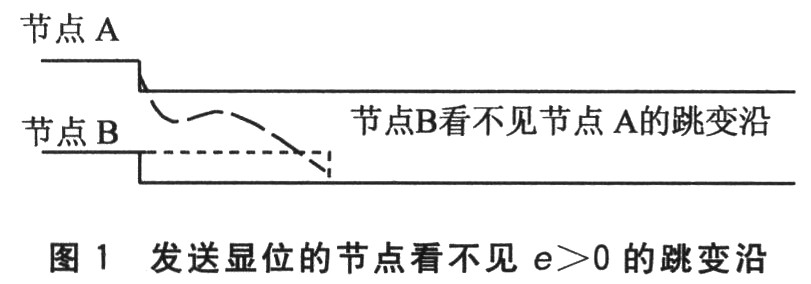

①正常传送时由于CAN填充位规则,重同步的距离最多为10位。为同步正确,有:

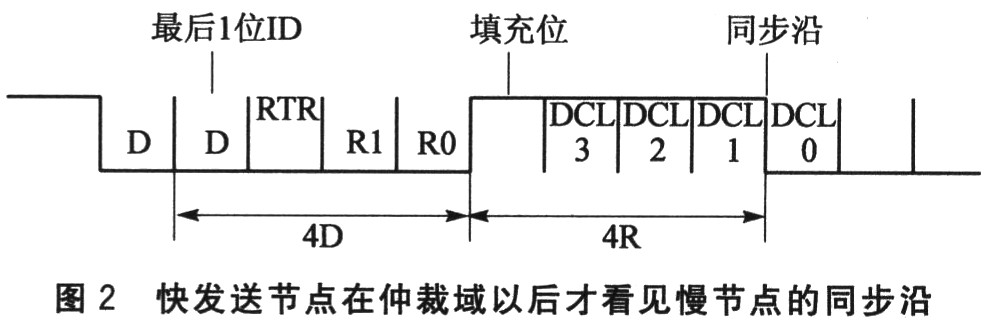

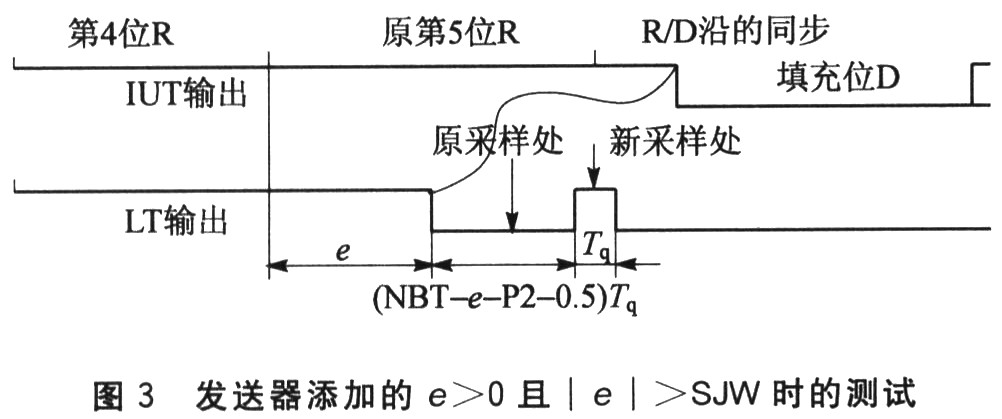

(2×△f)×10×NBT 其中,NBT为标称位时间。 ②出错时,有错的节点要发报错帧。为了区分是本地错还是全局错,要考察发出主动报错标志后的第7位是否还是显位。由于出错前可能有6位显位,所以2个同步段S相隔13位。容许的差小于缓冲段长: (2×△f)×(13×NBT-P2) 在2个不等式中选最小者为本应用的时钟容差。例如Tbit=1 000 ns,总线长20 m,收发器的延迟为150 ns时,整个传输延迟为Tprop=500 ns,取Tq=125 ns,算出Pr=4,P1=1,P2=2,SJW=1,NBT=8。由上述二式算出的△f分别为0.006 25和0.004 90,取其中小者0.004 90,即接近0.5%。 2 发送器时钟同步中产生的问题 CAN总线具有显位优先于隐位的特性,即当总线上有多个节点同时发送时,只要有1个节点发的是显位,总线上最终的结果就是显位。所以当2个相距有一定距离的节点同时发送显位时,由于传输需要时间,在一个节点处看不到另一个节点的R/D跳变沿(如图1所示,e为同步的相位差),因为总线的电平早已被该节点置为显位。 在这种情况下,节点A、B即使时钟有差别,也无法建立同步。设A比B快,仅当节点A的同步段S比节点B的同步段S越来越超前,且其超前量大于传输时间时,节点B才能看见A的R/D跳变沿,B才会开始进行同步。 现在分析2个发送器在仲裁区的同步问题。假定它们看到总线空闲并同时开始发送,它们的ID只是最后1位不同。有文献介绍发送节点同步过程时,假定总线空闲时有1个发送器领先于其他发送器,且超过Pr/2段发送的情况。由于事件发生的随机性,这只是特例。对于定时消息,它们由本节点的时钟触发。但本地时钟问并无同步,它们之间又存在频率差异,所以定时消息规定应发出的时间的相位差会周期性地变化。1个发送器领先所有其他发送器的情况也只是特例。在本文假设下,由于在ID前各位出现的R/D跳变沿均未被对方看见,它们之间没有同步关系。到最后1位,假定时钟慢的节点有显位而时钟快的节点有隐位,并假定ID前 1位是隐位,那么慢节点的R/D跳变沿将可能被快的节点看到。但是,它将有很大的相位差,可能已经超过了重同步跳转宽度SJW,从而无法使该快节点正确同步,便会导致采样在慢节点送来的电平尚未稳定的地方产生位值读错。 在CAN 2.0B的29位ID的最后1位,即仲裁域的第31位,由于可能还有7个填充位,即已有37位未进行同步。为了采样正确,未同步时快慢发送节点同步段的差应小于重同步跳转宽度SJW: (2×△f)×37×NBT≤SJW (3) 以前述例子的数据,NBT=8,SJW=1,得△f≤0.001 68,减小了很多。 由于接近快节点的接收器均能见到快节点的R/D跳变沿,它们已按快节点进行了同步。最后,它们要按未曾同步的慢节点进行同步,同样会遇到相位差很大时的同步问题。如果ID最后第2位已是显位,那么快节点将见不到慢节点的跳变沿,因为此时并不存在可供同步的R/D跳变沿,在仲裁域内快节点以及附近已与它同步的接收器将完全无法与慢节点同步。它们将按自己原来的相位及位时间进行采样。最坏的情况下,要再经过7位可以见到慢节点的下一个R/D跳变沿,如图2所示。 在仲裁域内未能见到跳变沿的发送器此时已变为接受器,虽然如此,若在后面的跳变沿能保证正确同步的话,那么在仲裁域中采样点的偏移就更小,应该能保证采样的正确,即仲裁的正确。此时仲裁域内未同步最多为40位(含可能的8位填充位),随后最近的跳变沿在6位后,于是为了能正确采样,应该有: (2×△f)×46×NBT≤SJW (4) 仍以第一部分中例子的数据,NBT=8,SJW=1,可得△f≤0.001 35,又小了一些。如果在某系统中有NBT=25,SJW=1,可得△f≤0.00043。这是相当小的值。 根据上述分析,最坏的情况是(4)式。对于CAN2.0 A,对应可以导出最坏情况为: (2×△f)×21×NBT≤SJW (5) 如果传输时间比较短,慢节点已按快节点延迟Pr/2后进行了同步,那么在慢节点最后胜出的那一位,快节点将见到e=Pr的来自慢节点的同步沿。为能保证同步,至少应有: Pr≤SJW (6) 如果(6)式满足,就可以发生同步。例如在传输延迟占位时间份额小的系统,用原ISO11898-1的算式。使用中,读取ACK位时,最坏的同步沿将相隔 11位(CRC分界符不在填充位规则内),(1)式还应该修改。如不满足(6)式,例如高速系统,就应考虑(4)或(5)式。ISO11898-1应添加上述内容。一般地说,(4)、(5)式比(1)、(2)式要求严格,如需要简化,用它们就足够了。例如对于CAN2.0A,用前面例子的数据,NBT=8,SJW=1,由(5)式可得△f≤0.002 97,也优于原来的0.004 90。 3 ISO 16845:2004应添加的条款 ISO16845关于发送器时间同步相关功能的一致性测试条款共9项(8.7.1~8.7.9),其中用于有相位差的重同步仅2项:8.7.4款,当 e<0且|e|≤SJW时的同步;8.7.5款,当P<0且e>SJW时的同步。由第2部分的分析可知,发送器在仲裁中退出的最后一位是需要进行同步的,此时它还是发送器状态。只有同步以后,才能正确采样,决定是否退出并保证退出以后能正确跟踪胜出的发送器。因此,需要添加 e>O,且| e |≤SJW,以及e>0,且| e |>SJW时的测试条款。这些条款可以参考接收器的相应条款(7.7.3和7.7.4)。 ISO 16845中的低层测试设备LT是专用设备,它与被测的CAN(称为被测试的实现IUT)的Tx、Rx相连,LT产生必要的输入条件到Rx,然后从Tx测取IUT的反应是否合格。非测试输入时LT不应影响IUT。以e>O且|e|>SJW时的测试为例,安排IUT发1帧在ID域带填充位为显位的帧。当发到第5个隐位时,LT延迟e将Rx变为显位,然后在延迟后的新采样点(原P1+SJW)处为Rx建1个隐位值,此时IUT的输出Tx将在LT提供的R/D跳变沿后一位按同步规则提供显位,如图3所示。上述测试设计基于如下原理:如果IUT动作正常,它将同步于LT提供的R/D跳变沿,并采到LT 提供的隐位,这时发出它的下一个填充位,填充位的R/D跳变沿已被IUT先前的同步所移动。如果同步不正常,或者跳转的量不对,IUT将采到显位,它会仲裁失败而退出,不会再发送。测试的P的范围是(SJW+1)~(NBT-P2-1)。这个设计不同于标准的7.7.4款。笔者认为7.7.4款的方法是不能达到目的的,该问题的详细讨论超出了本文的范围,不再赘述。 需要指出的是,8.7.2款中的正在发送显位的发送器,将不对e>0的R/D跳变沿作同步。这个要求与本文所述e>0时的同步问题是不同的。本文讲的是发送器发隐位,它见到了其他发送器的R/D跳变沿;而8.7.2款只是描述CAN芯片的Tx、Rx分开作输出、输入测试时的特性,实际应用时是分不开的,不会遇到这种情形。 4 小 结 CAN的一般技术资料均提到,高速时的可靠性要比低速时的差,应用中能用低速就用低速。从上述位同步时钟容差的分析可知,高速时时钟容差小,所以一旦时钟有问题就会影响同步与采样。CAN标准ISO11898-1:2003仅考虑了部分场合的要求,对发送器仲裁阶段未能同步的情况未作考虑,从而给出的容差结果偏宽,设计者有可能依此选用不合适的振荡源,造成电子控制器(ECU)可靠性不够。例如,现在已经有一些精度接近0.3%~2%的可修正的RC或 CMOS振荡器,它们价格低,接近原CAN标准设计的容差,有可能被不适当地选用。所以对标准加以补充是十分必要的。随着CAN应用的扩展,提高CAN工作频率的努力也在继续。一方面,有些应用可缩短传送距离以使传输时间缩短,例如机器人、武器等;另一方面,CAN的性价比高,对这类应用有吸引力,在传输时间接近临界情况的场合,更要注意时钟容差的问题。

从另一个角度考虑解决问题的可能性是:将仲裁域中及仲裁后的第1个同步沿发送器与接收器的同步均设为硬同步。这种做法可以改善同步以后的采样,但对同步以前的采样没有改善,它们仍然要求较高精度的时钟来保证采样点在缓冲段P1、P2之内。而且,过多的硬同步增加了对干扰进行不必要同步的机会,反而不是好事。因此这种方案是无价值的。 从分析可知,当重同步跳转宽度SJW可选得较大时,容许的时钟偏差就较大。不受限制的SJW相当于随时执行硬同步,小于P1、P2的SJW就使采样点的变动较小。当总线上由于干扰出现假的R/D跳变沿,就会引起错误的重同步,小的SJW有助于降低读错概率。因此,兼顾减少出错率与降低时钟容错限的要求,关键是设计一种性价比好的滤除干扰的办法。

电子发烧友App

电子发烧友App

评论