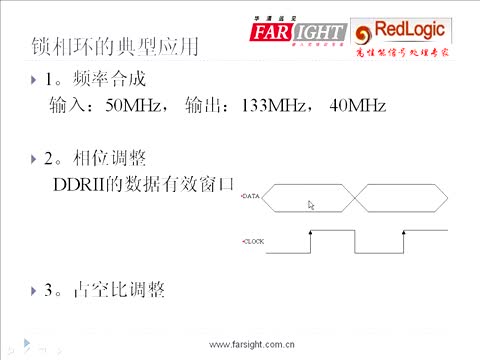

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源来形成一个RAM?如果我以ROM的形式调用该IP核,在

2013-01-10 17:19:11

的提升。同时也给运算增加了难度,对并行化运算、灵活化运算提出了更高的运算。三、FPGA H.265IP核简介1.性能摘要2.特点H.265帧速率:1fps-60fps支持双流输出支持投资回报率

2019-03-08 10:47:22

的基础上,给出了一种仿真调试方 案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。1 OC8051结构分析OpenCores网站提供的OC8051 IP核

2012-08-11 11:41:47

FPGA嵌入8051单片机 IP核编程,编写的c语言矩阵键盘程序可以在stc89c54单片机上正常工作,但是下载到FPGA中8051单片机ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

的FPGA中都集成了专用乘法器;为了适用通信总线与接口标准,很多高端的FPGA内部都集成了串并收发器(SERDES),可以达到数十Gbps的收发速度。Xilinx公司的高端产品不仅集成了Power PC

2023-05-30 20:53:24

本帖最后由 jf_25420317 于 2023-11-17 11:10 编辑

FPGA开发过程中,利用各种IP核,可以快速完成功能开发,不需要花费大量时间重复造轮子。

当我们面对使用新IP核

2023-11-17 11:09:22

有谁知道现在国内外有哪些公司卖FPGA的图像处理相关的IP核?

2015-04-28 21:34:24

是具有知识产权核的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。到了SOC 阶段,IP 核设计已成为ASIC 电路设计公司和FPGA

2018-09-03 11:03:27

求大神,FPGA内部的PCI的IP软核实现PCI接口设计?

2013-05-02 16:12:21

`Xilinx FPGA入门连载34:超声波测距终极结果显示之除法器IP解析特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1概述在本例

2015-12-09 12:22:00

Xilinx FPGA入门连载43:FPGA片内ROM实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述该工程

2016-01-06 12:22:53

实例内部系统功能框图如图所示。我们通过IP核例化一个RAM,定时遍历写入其所有地址的数据,然后再遍历读出所有地址的数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察FPGA片内RAM

2016-01-20 12:28:28

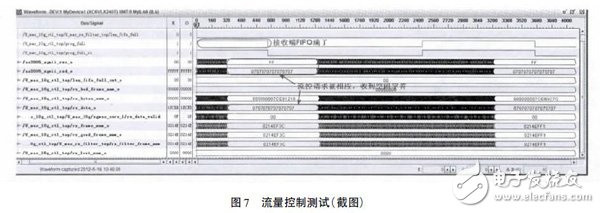

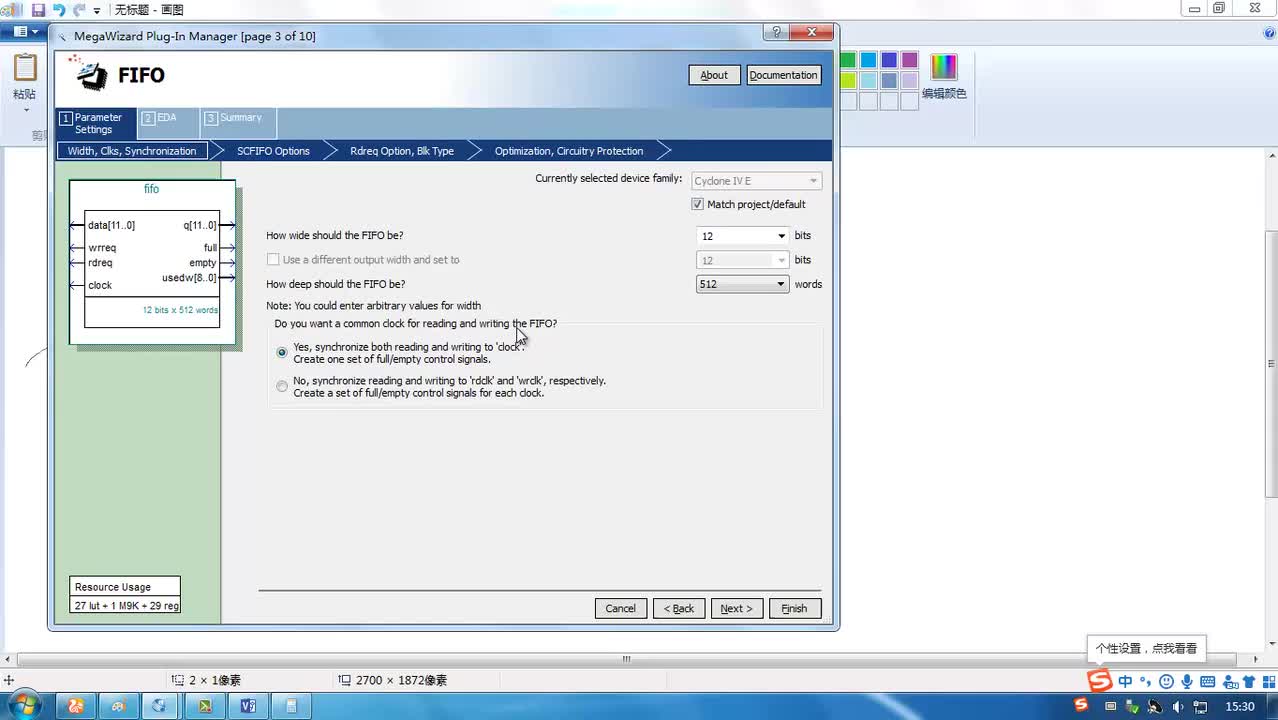

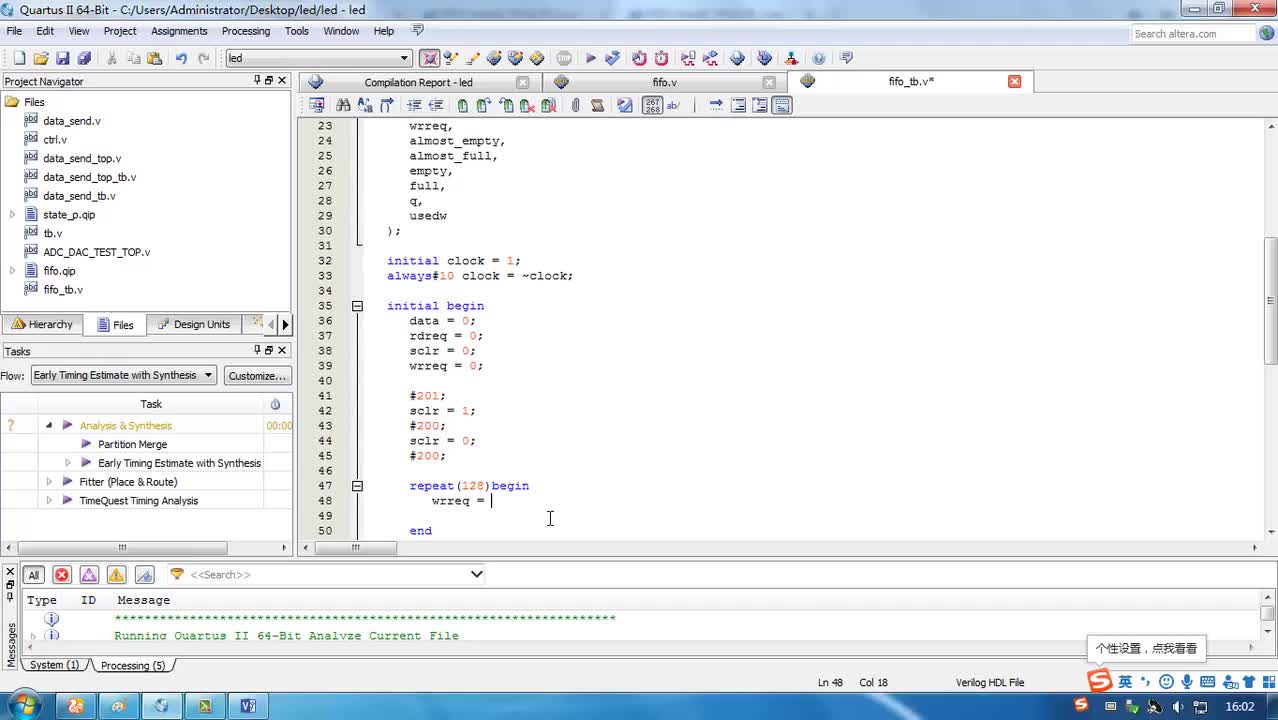

实例内部系统功能框图如图所示。我们通过IP核例化一个FIFO,定时写入数据,然后再读出所有数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察FPGA片内FIFO的读写时序。 2 模块

2016-02-26 10:26:05

`Xilinx FPGA入门连载55:FPGA 片内异步FIFO实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

`Xilinx FPGA入门连载59:FPGA 片内ROM FIFO RAM联合实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-16 12:43:36

`Xilinx系列FPGA芯片IP核详解(完整高清书签版)`

2017-06-06 13:15:16

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

利用FPGA自带的IP核实现双口RAM用于2片MCU进行数据交换时多次读数据后RAM中数据变为了0,是什么意思,打什么帮帮忙!!!!!!!!!!!!!!

2018-01-15 16:22:16

出现网络和数据存储协议处理的瓶颈或延迟。VCK190 评估套件和 Design Gateway 的网络和存储 IP 解决方案可在 Xilinx 的 Versal AI Core 器件上以尽可能低的 FPGA 资源使用量和极高的能效在 AI 应用中实现最佳性能。

2022-11-25 16:29:20

可以移植到不同的半导体工艺中去生产集成电路芯片。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个趋势。 本文研究了ATM流量控制的原理,并给出了一种IP核的实现方法,该IP核不仅可以用于独立芯片,还可以作为系统的一个子模块直接调用。

2011-09-27 11:54:25

Altera系列FPGA芯片IP核详解

2020-06-28 13:51:01

使用LabVIEW FPGA模块中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一个输入。我参考网上VHDL CORDIC IP核,说是将XY合并了,高位X低位Y。不知道在LabVIEW中如何将两个值X、Y合并成一个(X、Y均为定点数)。具体情况如下图:

2019-09-10 20:07:07

与FPGA架构相集成,可以实现更大的设计灵活性和更快的上市时间。美高森美为电机控制算法开发提供了具有多个多轴电机控制参考设计和IP的生态系统,使由多处理器解决方案转向单一器件解决方案(即SoC FPGA)更加容易。

2019-06-24 07:29:33

实现,于是2001年Altera第一次提出了可编程片上系统(SOPC)概念,并且推出了第一款嵌入式处理器软核Nios以及之后的第二代Nios II以及相应的开发环境,此后Xilinx也推出

2020-03-09 06:50:07

USB_OTG_IP核中AMBA接口的设计与FPGA实现

2012-08-06 11:40:55

`本视频是Combat FPGA开发板的配套视频课程,本章节课程主要介绍如何利用Gowin FPGA实现MAC协议开发。内容包括MAC协议概述,MAC帧结构,以及Gowin以太网Mac IP使用简介

2021-05-06 15:08:59

技术10.4.2 基于FPGA的千兆以太网MAC控制器实现方案10.4.3 Xilinx 千兆以太网MAC IP Core10.5 本章小结第11章时序分析原理以及时序分析器的使用11.1 时序分析的作用

2012-04-24 09:23:33

附件为使用FPGA实现两路CAN接口进行回环通信的工程文件。包含详细的工程使用说明文档。在小梅哥的Starter FPGA开发板上验证通过,CAN通信使用开源的OC_CAN IP和VP230收发器实现,上层应用使用NIOS II实现,使用非常方便。

2017-09-22 22:42:14

摘要针对FFT算法基于FPGA实现可配置的IP核。采用基于流水线结构和快速并行算法实现了蝶形运算和4k点FFT的输入点数、数据位宽、分解基自由配置。使用Verilog语言编写,利用ModelSim

2019-07-03 07:56:53

。FPGA具有并行运算、反复使用、大量可使用的软核的优势,是实现机器视觉理想构架的合理选择。FPGA是小批量系统提高集成度、可靠性的最佳选择之一。随着VLSI工艺的不断提高,单一芯片内部已可以容纳上百万个

2019-05-05 08:30:00

各位前辈好!我在用Xilinx Virtex5 FPGA做通过千兆网和上位机通信,有几个问题想请教:1、tri-mode ethernet mac 和 virtex-5 embedded

2016-05-31 22:41:53

基于FPGA的嵌入式系统的开发工具包。本文介绍基于SoPC的波形发生器在EDK工具包下的设计与实现。本设计采用嵌入式软处理器核 MicroBlaze以及自主编写的包括实现DDS在内的多种IP Core

2009-06-25 08:12:37

基于FPGA的IP核8051上实现TCPIP的设计

2012-08-06 12:18:28

我毕业设计要做一个基于FPGA的IP核的DDS信号发生器,但是我不会用DDS的IP核,有没有好人能发我一份资料如何用IP核的呀。我的浏览器下载不了网站上的资料,所以只能发帖求帮忙了。

2015-03-10 11:46:40

基于FPGA的FFT和IFFT IP核应用实例AT7_Xilinx开发板(USB3.0+LVDS)资料共享腾讯链接:https://share.weiyun.com/5GQyKKc百度网盘链接

2019-08-10 14:30:03

在通信、图像处理、模式识别等领域都有着广泛的应用。Vivado集成的FIR IP核可以实现如下公式所示的N级卷积运算。 FIR IP核可以根据配置实现复用的乘累加单元,以实现面积最优化的设计;当然了

2019-07-16 17:24:22

最小硬件系统设计原理图;2)10/100 Ethernet MAC IP源代码和驱动;3)集成10/100 Ethernet MAC在内的Nios处理器片上系统架构设计实例,以及该系统下经过严格测试

2014-06-19 12:04:25

最小硬件系统设计原理图;2)10/100 Ethernet MAC IP源代码和驱动;3)集成10/100 Ethernet MAC在内的Nios处理器片上系统架构设计实例,以及该系统下经过严格测试

2014-06-19 12:06:43

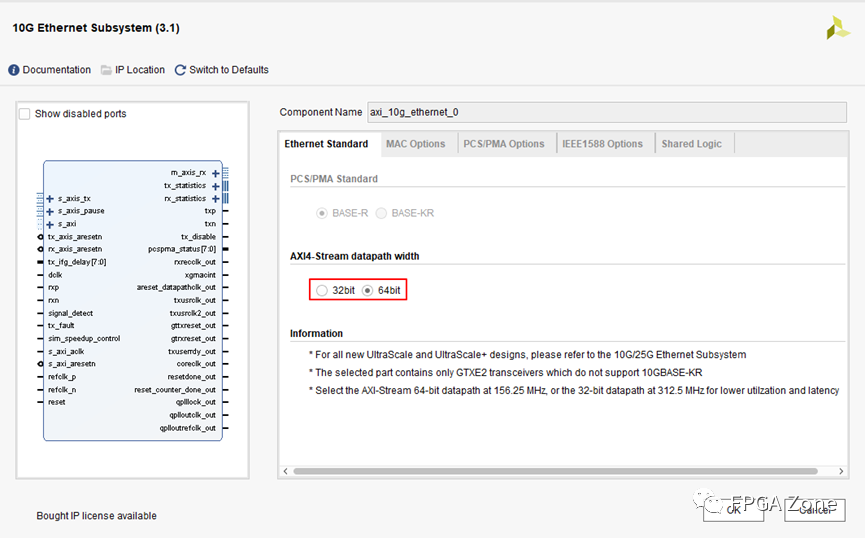

Ethernet PCS/PMA IP核本案例使用10G Ethernet PCS/PMA IP核实现物理层(PCS与PMA)功能。10G Ethernet PCS/PMA IP核开发文档为产品资料“6-开发

2021-01-21 19:24:54

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

此提供了新的解决方案。IP核(IP Core)是具有特定电路功能的硬件描述语言程序,可较方便地进行修改和定制,以提高设计效率[3]。本文研究了基于FPGA的数据采集控制器IP 核的设计方案和实现方法,该IP核既可以应用在独立IC芯片上,还可作为合成系统的子模块直接调用,实现IP核的复用。

2019-07-09 07:23:09

。FPGA具有并行运算、反复使用、大量可使用的软核的优势,是实现机器视觉理想构架的合理选择。 FPGA是小批量系统提高集成度、可靠性的最佳选择之一。随着VLSI工艺的不断提高,单一芯片内部已可以容纳

2013-09-04 12:14:55

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

实现的RTL级设计,与具体实现工艺无关,相比于固核和硬核具有较大的灵活性,在FPGA中定制PCI接口软核实现PCI接口控制具有明显的优势:可以在单片FPGA中同时完成PCI接口和用户逻辑的设计,缩减成

2018-12-04 10:35:21

引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口标准

2019-06-11 05:00:07

【摘要】:Viterbi译码器在通信系统中应用非常普遍,针对采用DSP只能进行相对较低速率的Vit-erbi译码的问题,人们开始采用FPGA实现高速率Viterbi译码。本文首先简单描述了

2010-04-26 16:08:39

内容简介本书基于XILINX的嵌入式开发平台,讲解了嵌入式系统的基本概念、FPGA和MicroBlaze处理器以及最新的多端口内存控制器(MPMC)的原理。[1]通过不同的总线和接口实验,详细讲述了

2017-12-08 14:27:35

入RAM。本实验将为大家介绍如何使用FPGA内部的ROM以及程序对该ROM的数据读操作。1.实验原理Xilinx在VIVADO里为我们已经提供了ROM的IP核, 我们只需通过IP核例化一个ROM,根据

2021-01-07 15:48:39

on Chip)是以嵌入式系统为核心,以IP复用技术为基础,集软、硬件于一体的设计方法。使用IP复用技术,将UART集成到FPGA器件上,可增加系统的可靠性,缩小PCB板面积;其次由于IP核的特点

2019-08-20 07:53:46

(IntellectualProperty)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短设计周期,提高设计质量。现场

2019-09-03 07:44:22

本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2021-05-08 06:22:32

怎么才能在嵌入FPGA的IP核8051上实现TCP/IP的设计?

2021-04-29 06:51:27

深圳明德扬科技教育有限公司,是一家高科技民营公司,主营业务为IC/FPGA设计、开发、培训。旗下包括广州健飞集成电路设计有限公司(办公设在广州市南沙自贸区)、龙核集成电路IP核交易平台。明德扬

2018-06-02 17:35:40

在学校做毕业设计,被老板要求在Xilinx的FPGA上完成SATA的操作,急需SATA的HOST与DEVICE的IP核。由于可以使用部分项目经费,所以重金求购SATA IP核。在网上查了一下,有

2014-02-07 10:34:53

Xilinx系列FPGA芯片IP核详解 ,altera系列FPGA芯片IP核详解 , 相关资料 谢谢!!万分感谢!!!!!

2015-06-03 15:03:34

采用xilinx EDK的GPIO IP核实现中断的功能(里面很详细的)

2012-08-17 10:02:52

(Intellectual Property)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短

2019-07-29 08:33:45

通过将第三方IP集成到NI LABVIEW软件中,您可以使用许多为XILINX现场可编程门阵列(FPGA)精调过的算法实现高性能,并且提高代码重用度。LABVIEW FPGA模块为导入外部IP提供了两个方法:组件级知识产权(CLIP)节点和结合XILINX核心生成器的IP集成节点。本技

2011-03-15 13:25:58 90

90 利用FPGA的IP核设计和实现FFT算法

2016-05-24 14:14:47 36

36 Xilinx FPGA工程例子源码:Xilinx TCP_IP协议实现

2016-06-07 14:54:57 31

31 研究了TCP/IP通信协议栈在Xilinx 公司现场可编程门阵列FPGA上的实现,介绍了其软硬件的系统组成

和原理,提出一种不需操作系统的TCP/IP协议栈的高效工作模式,并在

2017-09-04 09:24:59 9

9 研究了嵌入式TCP/IP通信协议栈在Xilinx FPGA上的实现,介绍了其软硬件的系统组成和原理,提出一种实时操作系统上TCP/IP协议栈的高效工作模式,并在Virtex5 FPGA上移植成功。通过建立测试平台进行数据传输测试,证明其具有稳定、高效的通信性能,为嵌入式设备开发提供了新的思路。

2017-11-17 17:05:01 7251

7251

。 使用Xilinx内核生成器IP函数实现FPGA VI中不同的Xilinx内核生成器IP。LabVIEW使用IP集成节点实现上述函数。函数名称和说明来自于Xilinx数据表。单击Xilinx内核生成器配置对话框的数据表按钮,了解IP内核的详细信息。 选板随终端变化且仅显示FPGA设备系列支持的IP。

2017-11-18 05:54:05 1286

1286 本页包含通过LabVIEW FPGA模块可用的Xilinx CORE生成器IP的列表。LabVIEW通过Xilinx IP节点实现该IP。 下列IP名称和说明来自于Xilinx数据表。LabVIEW

2017-11-18 05:55:51 4465

4465 LabVIEW使用IP集成节点方便的整合Xilinx内核生成IP至FPGA VI。按照下列步骤添加Xilinx内核生成器IP至FPGA VI。 1、在支持的FPGA终端下新建一个空白VI,并显示VI

2017-11-18 05:56:22 1746

1746 资源。为简化设计,降低硬件资源开销,可以在FPGA中利用IP核实现的嵌入式微处理器来对串口数据进行处理。

2019-08-02 08:08:00 3816

3816 Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

9496 本文接续上一篇《FPGA杂记基础篇》,继续为大家分享IP例化和几个基于FPGA芯片实现的Demo工程。IP例化IP即是一个封装好的模块,集成在相应的开发环境里面,以安路的TD软件为例,不同系列的芯片集成了不同的IP模块,可以通过软件例化调用

2020-12-24 12:58:51 1048

1048 基于FPGA的TCP/IP协议的实现说明。

2021-04-28 11:19:47 49

49 ARTIX-xlinx 版本FPGA 串口通信模块(含IP核)

2022-06-20 11:07:28 12

12 笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109。

2023-07-10 10:43:18 632

632

外部存储器接口( EMIF )通信常用于FPGA和DSP之间的数据传输,即将FPGA作为DSP的外部SRAM、或者协同处理器等。Xilinx提供了AXI-EMC IP核,将其挂载到AXI总线用于

2023-08-31 11:25:41 2357

2357

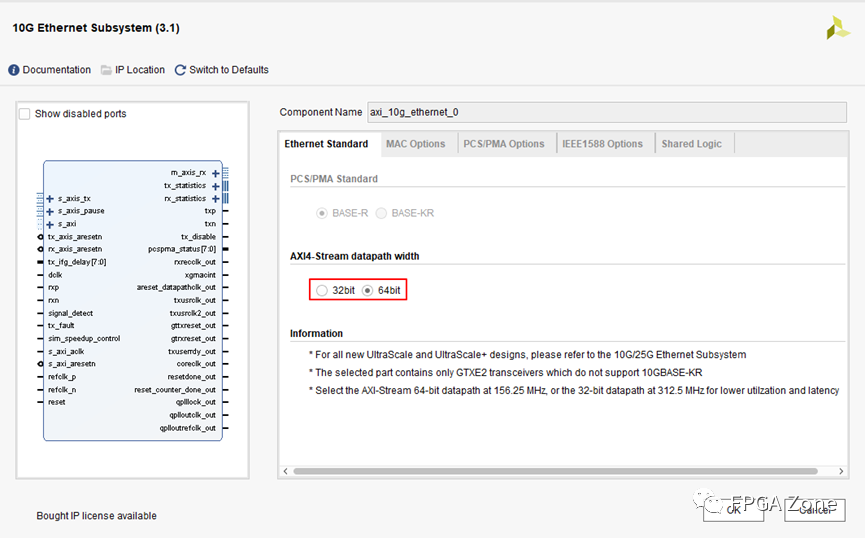

本文开源一个FPGA项目:UDP万兆光通信。该项目实现了万兆光纤以太网数据回环传输功能。Vivado工程代码结构和之前开源的《UDP RGMII千兆以太网》类似,只不过万兆以太网是调用了Xilinx

2023-09-01 16:25:13 742

742

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317

电子发烧友App

电子发烧友App

评论