讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。 软件

2020-12-16 15:47:59 1692

1692

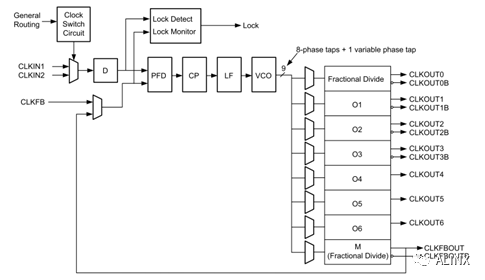

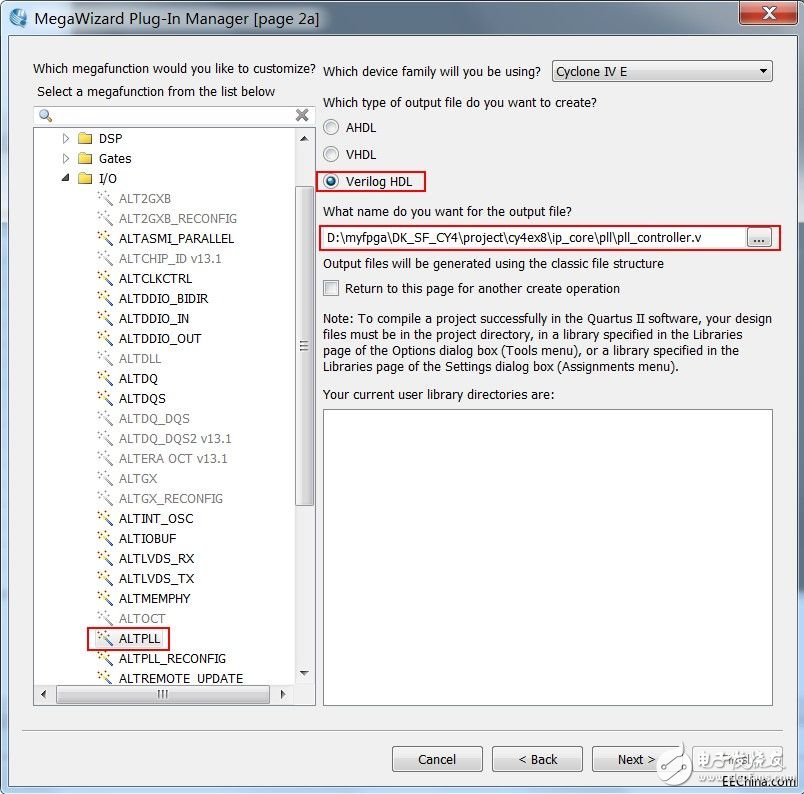

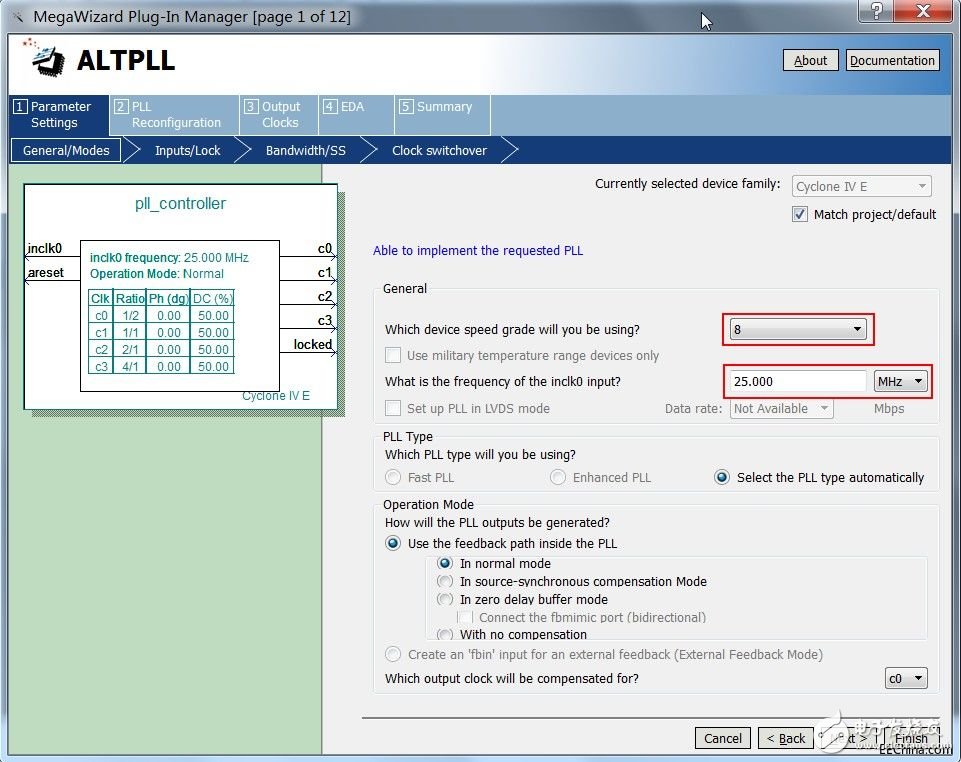

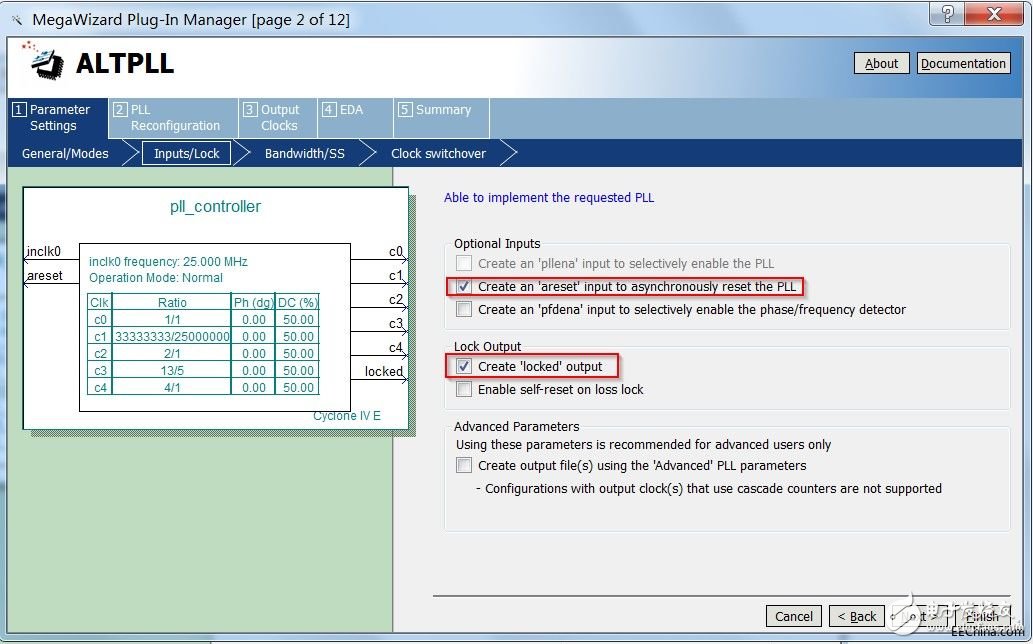

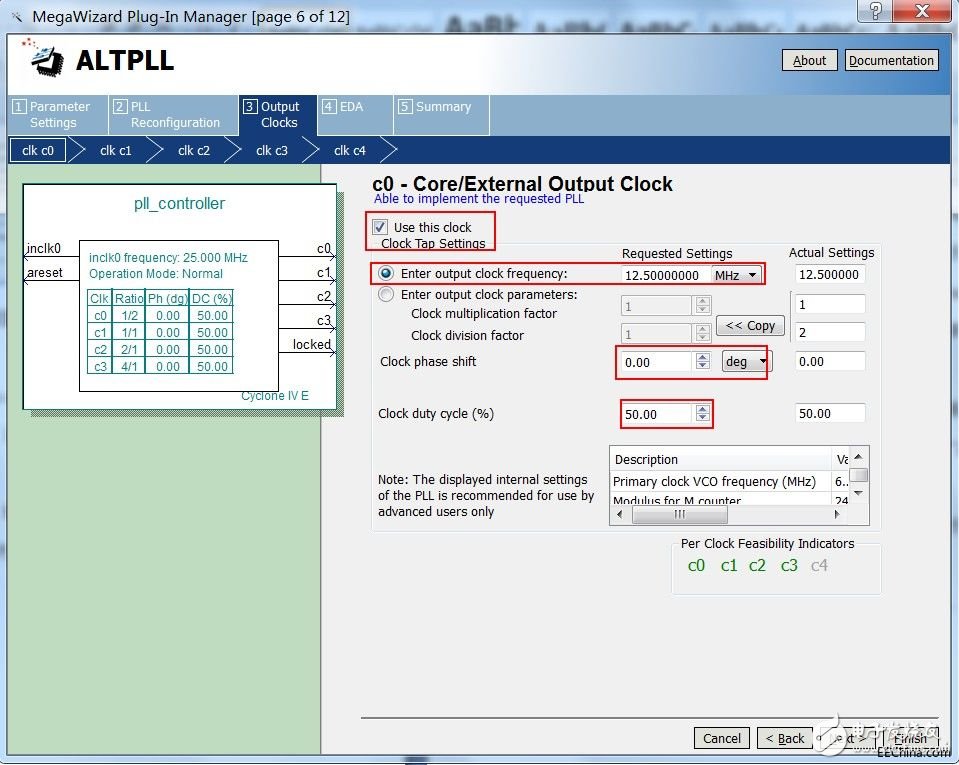

也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL ip core来学习PLL的使用方法。

2021-02-04 13:22:00 6661

6661

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

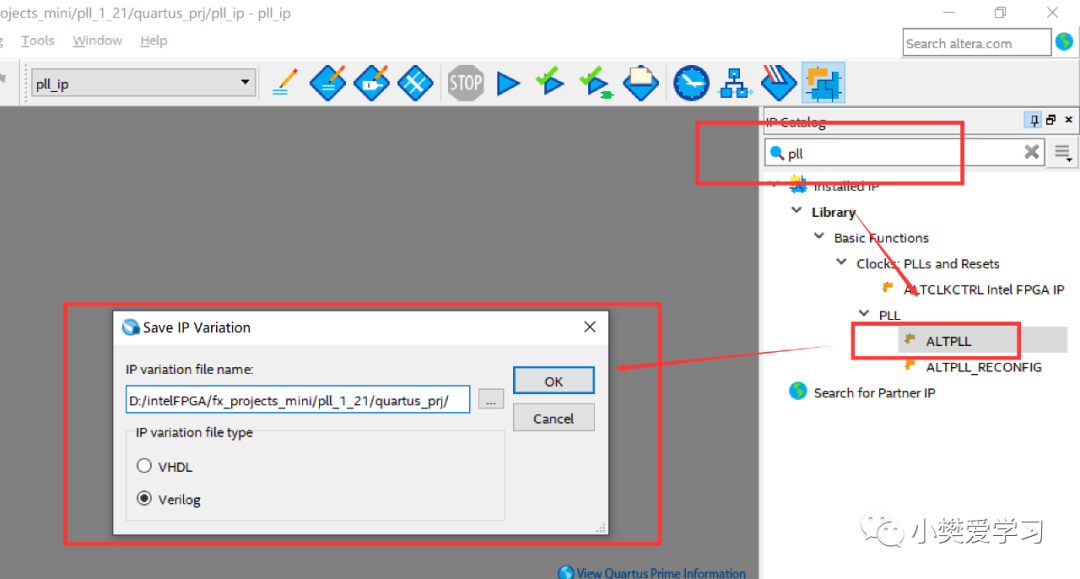

在我们设计工程中我们会用到100M,500M等时钟,如果我们的晶振达不到我们就需要倍频,再上一个文档中我们了解到了分频,可是倍频我们改怎么做了,这里我们就用了altera的IP核锁相环。今天我们将去学习

2019-06-17 08:30:00

FPGA硬核与软核处理器有什么区别和联系?

2023-05-30 20:36:48

在配置PLL过程中,打开了megawizard plug-in manager后,下拉菜单中没有IO这个选项,更别说选ATLPLL了,求问这是什么情况!PLL配置教程原帖http

2017-03-22 09:58:41

,Lattice公司的新型芯片上同时集成了PLL和DLL。PLL 和DLL可以通过IP核生成的工具方便地进行管理和配置。DLL的结构如图1-5所示。7. 内嵌专用硬核 内嵌专用硬核是相对底层嵌入的软核

2017-05-09 15:10:02

如果要学习关于FPGA的pll搭建和让工程在有源码的情况下一步一步变为例程中那样有序的工程,该做那些准备呢?

2016-12-28 00:46:41

,Lattice公司的新型芯片上同时集成了PLL和DLL。PLL 和DLL可以通过IP核生成的工具方便地进行管理和配置。DLL的结构如图1-5所示。图1-5 典型的DLL模块示意图7. 内嵌专用硬核内嵌专用硬核

2023-05-30 20:53:24

的情况时,总会遇到一些以前未曾接触过的新内容,这些新内容会让我们感到陌生和恐惧,不知道该如何下手。

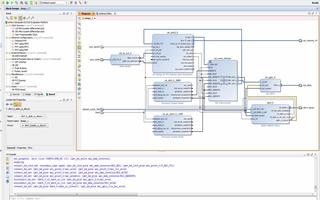

那么今天以xilinx vivado 为例分享学习FPGA 新IP核的正确打开方式。

一、常规

2023-11-17 11:09:22

文档创建既然是ROM,那么我们就必须实现给它准备好数据,然后在FPGA实际运行时,我们直接使用这些预存储好的数据就行。Xilinx FPGA的片内ROM支持初始化数据配置。如图所示,我们可以创建一个名为

2019-04-08 09:34:43

寄存器和查找表的组合模式也不同。 学习底层配置单元的LUT和Register比率的一个重要意义在于器件选型和规模估算。由于FPGA内部除了基本可编程逻辑单元外,还有嵌入式的RAM、PLL或者是DLL

2019-09-24 11:54:53

寄存器和查找表的组合模式也不同。 学习底层配置单元的LUT和Register比率的一个重要意义在于器件选型和规模估算。由于FPGA内部除了基本可编程逻辑单元外,还有嵌入式的RAM、PLL或者是DLL

2016-07-16 15:32:39

寄存器和查找表的组合模式也不同。 学习底层配置单元的LUT和Register比率的一个重要意义在于器件选型和规模估算。由于FPGA内部除了基本可编程逻辑单元外,还有嵌入式的RAM、PLL或者是DLL

2016-08-23 10:33:54

寄存器和查找表的组合模式也不同。 学习底层配置单元的LUT和Register比率的一个重要意义在于器件选型和规模估算。由于FPGA内部除了基本可编程逻辑单元外,还有嵌入式的RAM、PLL或者是DLL

2016-09-18 11:15:11

寄存器和查找表的组合模式也不同。 学习底层配置单元的LUT和Register比率的一个重要意义在于器件选型和规模估算。由于FPGA内部除了基本可编程逻辑单元外,还有嵌入式的RAM、PLL或者是DLL

2016-10-08 14:43:50

的主流形式之一。 硬核 (Hard IP Core) :硬核在EDA 设计领域指经过验证的设计版图;具体在FPGA 设计中指布局和工艺固定、经过前端和后端验证的设计,设计人员不能对其修改。不能修改的原因

2018-09-03 11:03:27

如何根据成本、功耗和性能来选择微处理器?FPGA结构中硬核和软核的特点是什么?处理器IP有什么重要性?

2021-04-08 06:16:37

不多说,上货。IP CORE 之 PLL- ISE 操作工具本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频。Xilinx

2023-04-06 16:04:21

在我的一个FPGA类中,我被要求使用coregen创建一个blcok ram(8dx16w),单端口ram IP。我在Windows XP,Service Pack 3上使用Xilinx ISE

2019-06-05 13:39:14

。图像识别是一项相当复杂的机器学习任务,通常

需要比关键字识别更高的性能。

该指南也适用于想要为高端智能设备创建SoC的系统设计人员设备,比如智能手机。

具体来说,该指南解释道:

•为什么要为这个

2023-08-02 11:02:42

。通过写寄存器将AD9364状态置为FDD状态时(reg[0x017]=0x1A),发现FPGA内部PLL不能保持锁定状态了。 请教大家哪个寄存器的配置有问题会造成上述现象?附件1.png17.2 KB

2018-08-20 07:20:29

zynq是xilinx的新一代的嵌入ARM硬核的SOC,请问1、这种FPGA器件相对以往传统FPGA有哪些优势和劣势?2、针对图像和视频处理的,这两类哪一种器件更适合?3、相同价格的情况下,ARM硬核的引入相比传统FPGA是否会降低zynq的性价比和灵活度?

2022-07-25 14:35:16

)放置flash 偏移地址0x50000处,关闭看门狗,重新配置后,发现fpga只更新了硬核,软核没有运行。通过测试,发现更新完硬核后,软核还是找到的第一个程序软核入口。没有找到要更新程序软核入口地址。不知道如何设置,使重新配置后,能够找到更新程序软核地址?希望大神帮助。。感激

2017-07-30 10:21:09

Altera可重配置PLL使用手册在实际应用中,FPGA的工作时钟频率可能在几个时间段内变动,对于与之相关的锁相环(PLL),若PLL的输入时钟在初始设定的时钟频率的基础上变化不太大时,PLL一般

2009-12-22 11:27:13

拥有成本,从而带来可持续的长期盈利能力。美高森美公司(Microsemi)提供具有硬核ARM Cortex-M3微控制器和IP集成的SmartFusion2 SoC FPGA器件,它采用成本优化的封装

2019-06-24 07:29:33

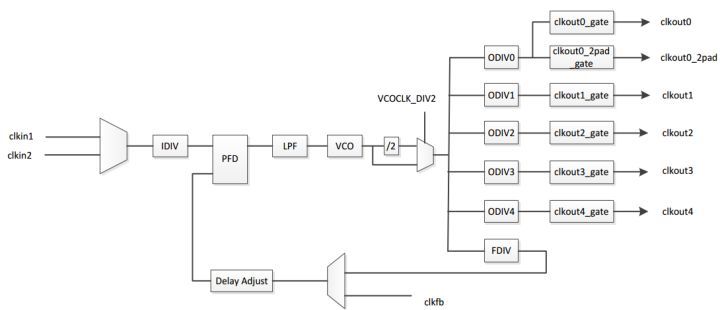

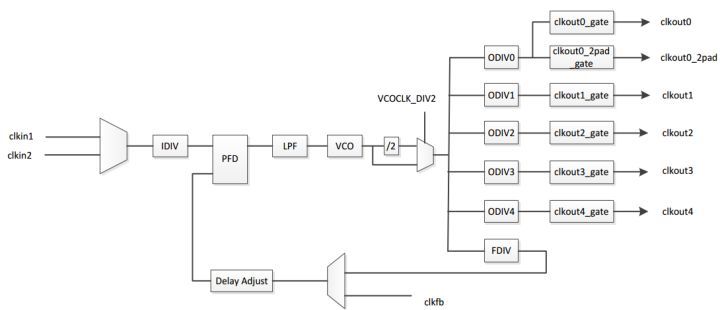

EG_PHY_PLL 是 FPGA 内部的时钟锁相环硬核 IP 模块,Eagle 系列 FPGA 内嵌 4 个多功能锁相环(PLL0~PLL3),分布在器件四角,可实现高性能时钟管理功能。每个

2022-10-27 07:45:54

嗨! Ultrascale + 100G以太网硬核IP是否支持RS_FEC?如果是,我们如何访问RS_FEC?

2020-05-22 15:18:57

Xilinx FPGA入门连载24:PLL实例之基本配置 1 工程移植可以复制上一个实例sp6ex7的整个工程文件夹,更名为sp6ex8。然后在ISE中打开这个新的工程。 2 新建IP核文件

2019-01-21 21:33:40

`Xilinx FPGA入门连载24:PLL实例之基本配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植可以复制上一个实例

2015-11-16 12:09:56

本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2021-03-02 07:22:13

我用xilinx spartan-6fpga 它硬核的管脚是固定的还是可配置的我在xilinx提供的文档里找不到关于硬核管脚的分配求指导

2012-08-11 09:28:44

`PLL锁相环介绍与简单应用实验目的:1.学会配置Altera提供的PLL IP核并进行仿真了解其接口时序2.利用参数化设计一个简易的系统进行验证已配置好的PLL实验平台:芯航线FPGA学习套件主板

2017-01-05 00:00:52

,Altera 公司的芯片集成了PLL。7. 内嵌专用硬核内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA 处理能力强大的硬核(Hard Core),等效于ASIC 电路。为了提高FPGA 性能,芯片生产商在芯片内

2012-03-08 11:03:49

本帖最后由 蛙蛙蛙 于 2021-4-12 17:51 编辑

本视频是Runber FPGA开发板的配套视频课程,主要通过PLL的工程实例讲解高云IP core的使用,课程主要介绍什么是IP

2021-04-12 16:45:11

基于Lattice MXO2 LPC的小脚丫FPGA核心板 - Type C接口

开发板的硬件规格如下:

核心器件:Lattice LCMXO2-4000HC-4MG132

132脚BGA封装

2024-01-31 21:01:32

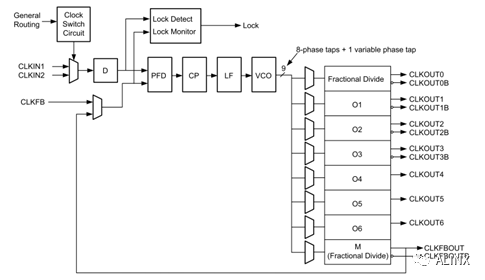

/PLL IP核的使用方法是我们学习FPGA的一个重要内容。本章我们将通过一个简单的例程来向大家介绍一下MMCM/PLL IP核的使用方法。本章包括以下几个部分:1111.1MMCM/PLL IP核简介

2020-09-22 16:48:59

,以PLL为例。 过程创建工程创建空的工程pll IP核配置Tools->IP Compiler 看到又如下IP 选择PLL下的PLL(1.5),设置实例名Instance Name,点击

2023-02-09 23:21:59

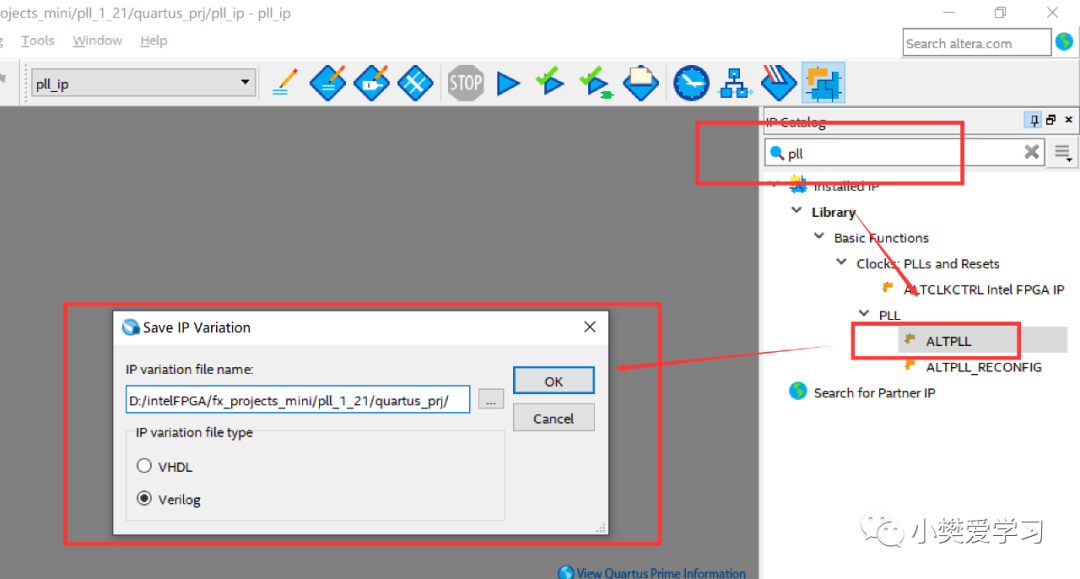

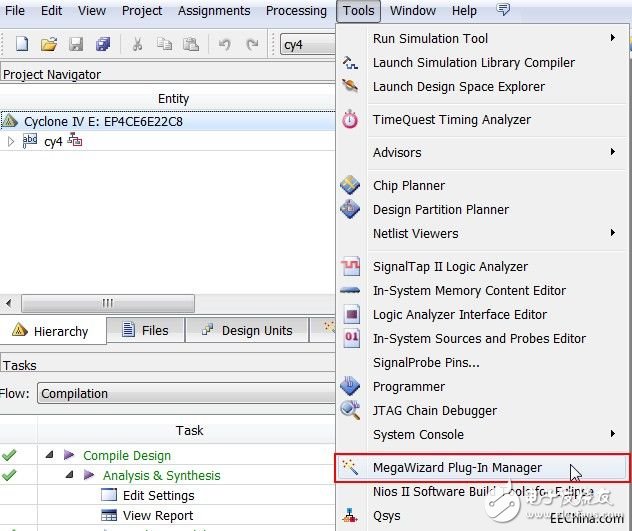

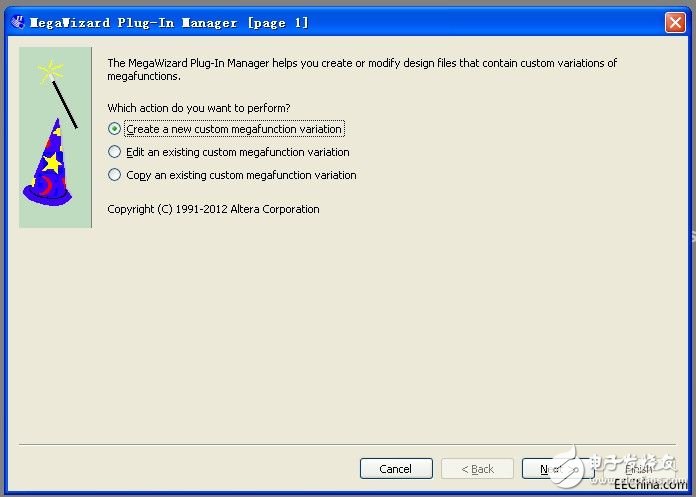

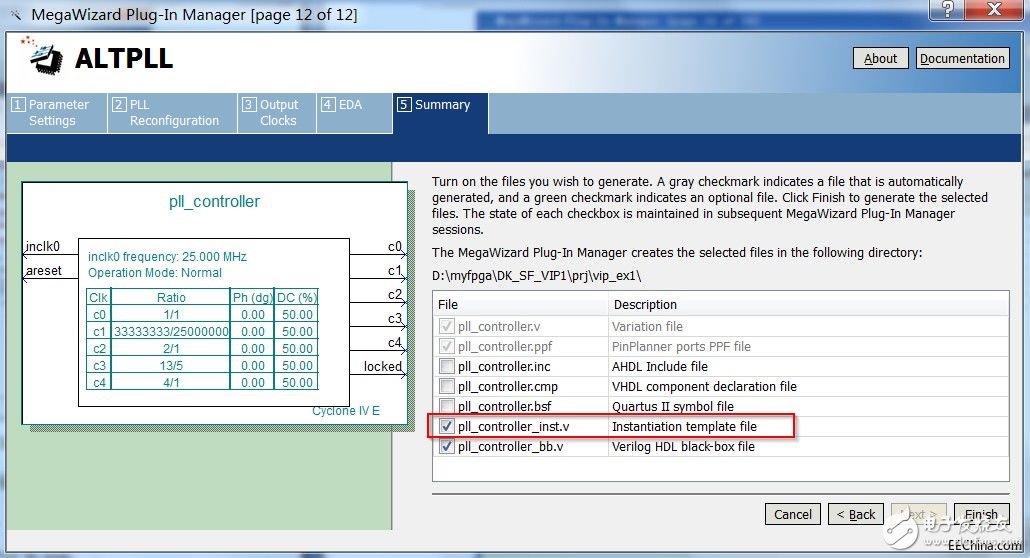

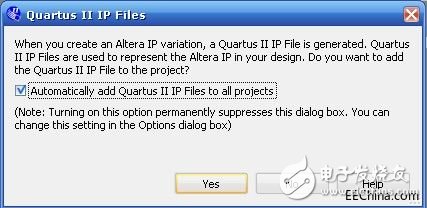

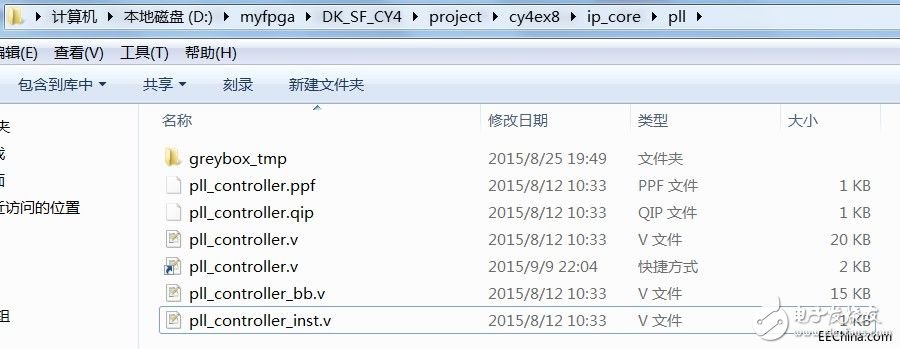

通过Quartus II 软件创建PLL IP核。首先,要新建一个工程,这个方法在之前的帖子中已经发过,不会的可以查看前面的相关帖子。创建好自己的工程:打开如下的菜单

2016-09-23 21:44:10

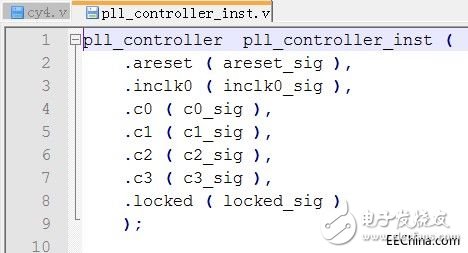

的时钟。首先建立一个文件在ip核目录里搜索ALTPLL然后在工程文件的par文件里建立一个文件夹ipcore将刚刚的变化保存到文件里命名为pll_clk然后点击ok就会出现配置过程界面FPGA系统晶振为

2020-01-13 18:13:48

`例说FPGA连载30:PLL例化配置与LED之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 本实例使用Quartus II

2016-09-09 18:29:24

`例说FPGA连载31:PLL例化配置与LED之PLL的IP核配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 本实例使用了一个

2016-09-12 17:31:43

。比如:怎么创建工程,怎么添加文件,怎么跑一系列编译的流程,怎么加入时序约束,怎么分配管脚,然后怎么把生成的FPGA映像加载到开发板上运行。

第二,就是熟悉一些常用的IP的用法

。在FPGA项目中,我们

2024-01-02 23:03:31

FPGA的硬核和软核有什么区别呢,有没有使用硬核的开发板,想学习关于FPGA硬核的知识,各位大神有什么建议呢?真心求教

2013-03-05 11:51:54

本人想问下,FPGA的介绍中有些事说带有PCIe硬核的,那么这个FPGA直接购买后就可以使用这个硬核完成PCIE功能了吗?不再需要购买其他什么许可文件之类的东西了吗? 这点不是很清楚,顺便问一下带有这中硬核的FPGA大概要多少钱呢?

2012-12-12 17:52:08

`勇敢的芯伴你玩转Altera FPGA连载63:PLL IP核创建于配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 可以复制上一个

2018-04-20 21:45:06

如何使用部分PLL创建调制波形

2021-04-06 06:19:42

和硬核都必需的一些可交付使用的提供物。1.文档创建清晰和简练的文档是大多数技术产品的先决条件。然而,需要参考IP核文档的人差异非常大,这使IP核技术文档创建面临非常大的挑战。在图1中,每一个开发活动都有

2021-07-03 08:30:00

[]()使用SF1的硬核使用IP Generator生成RISC-V硬核和PLL核创建工程并选择器件为SF160CG121I。点击Tools->IP Generator,选择

2023-04-16 17:34:01

大家好我正在使用Zynq ZC702板。如何创建自己的PLL时钟?例如,我的IP需要25MHz时钟我尝试了以下方法1. XPS中的时钟向导2.AXI时钟发生器但我仍然无法获得25MHz的时钟。谁能帮我?谢谢

2019-09-03 10:43:07

在线求助是否有带DA或者AD硬核的fpga 还是只能由外置的da ad

2012-06-01 14:49:26

往往需要使用多个时钟和时钟相位的偏移,且通过编写代码输出的时钟无法实现时钟的倍频,因此学习Altera PLL IP核的使用方法是我们学习FPGA的一个重要内容。本章我们将通过一个简单的例程来向大家

2020-07-30 14:58:52

LED,而是IP核的应用,当然,仅以PLL IP核为例。2 模块化设计参考文档《玩转Zynq-基础篇:基于FPGA的模块化设计.pdf》。3 PLL IP核添加配置 3.1Vivado标准IP核概述我们

2019-09-06 08:13:18

本文档主要是以Altera公司的Stratix II系列的FPGA器件为例,介绍了其内嵌的增强型可重配置PLL在不同的输入时钟频率之间的动态适应,其目的是通过提供PLL的重配置功能,使得不需要对

2010-11-02 15:17:24 27

27 在开始查找PLL的最佳配置之前,需要考虑的是如何才能为PLL找到配置。具体而言,我们应找到PLL针对给定参考振荡器和所需输出频率所使用的所有可行配置。只有在确保获得能够满足需

2012-11-22 10:34:32 3472

3472 FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 JAVA教程之创建和配置数据源,很好的JAVA的资料,快来学习吧。

2016-04-12 17:41:43 6

6 单片机是基于FLASH结构的,所以单片机上电直接从本地FLASH中运行。但SRAM 架构的FPGA是基于SRAM结构的,掉电数据就没了,所以需要借助外部电路来配置运行的数据,其实我们可以借助Vivado来学习FPGA的各种配置模式。

2018-11-05 15:12:57 7298

7298 了解如何在IP Integrator中创建简单的MicroBlaze设计,并创建一个在KC705目标板上运行的简单软件应用程序。

2018-11-20 06:13:00 2836

2836

本视频介绍了使用IP Integrator(IPI)创建简单硬件设计的过程。

使用IPI可以无缝,快速地实现DDR4和PCIe等块

连接在一起,在几分钟内创建硬件设计。

2018-11-22 06:13:00 4157

4157

该篇不仅讲解了如何使用Quartus II软件、ModelSim和SignalTap II软件,还讲解了PLL、ROM、RAM和FIFO IP核的使用。从第一个新工程建立,管脚分配,程序下载及工程

2019-12-06 07:03:00 2931

2931 先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19:00 2456

2456

,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2022-02-08 15:13:17 3306

3306

,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2021-01-29 09:30:52 7

7 本文档的主要内容详细介绍的是在FPGA上编写通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序免费下载。

2021-03-10 15:50:00 50

50 在FPGA中配置PLL的步骤及使用方法

2021-05-28 10:01:17 20

20 设计的带嵌入式收发器的Gen1×1硬核IP的 PCI Express IP编译器(基于嵌入式开发游戏项目)-在Cyclone IV GX收发器入门套件上,设计带嵌入式收发器的Gen1×1硬核IP的 PCI Express IP编译器。.rar

2021-07-30 16:48:41 9

9 在FPGA上编写的通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序(开关电源技术与设计潘永雄.pdf)-在FPGA上编写的通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序,适合感兴趣的人学习参考

2021-09-16 11:37:05 61

61 内嵌处理器硬核的FPGA,即SoC FPGA,是在芯片设计之初,就在内部的硬件电路上添加了硬核处理器,是纯硬件实现的,不会消耗FPGA的逻辑资...

2022-01-26 19:23:29 2

2 在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之后的设计中继续使用此IP。因此本次详细介绍使用VIvado来封装自己的IP,并使用IP创建工程。

2022-04-21 08:58:05 4579

4579 电子发烧友网站提供《EF3 PLL动态配置.pdf》资料免费下载

2022-09-27 10:26:04 0

0 电子发烧友网站提供《ELF2 FPGA PLL动态配置.pdf》资料免费下载

2022-09-26 15:13:06 0

0 定时决定一切:如何使用部分 PLL 创建调制波形

2022-11-04 09:52:13 0

0 IP_数据表(A-3):Analog-PLL For Frequency Multiplying

2023-03-16 19:27:15 0

0 IP_数据表(A-6):Analog-PLL For Skew adjust

2023-03-16 19:27:43 0

0 IP_数据表(A-9):Analog-PLL For Skew adjust

2023-03-16 19:28:21 0

0 IP_数据表(A-1):Analog-PLL For Frequency Multiplying

2023-03-16 19:30:25 0

0 IP_数据表(A-4):Analog-PLL For Frequency Multiplying

2023-03-16 19:30:43 0

0 IP_数据表(A-7): 用于小数乘法的模拟 PLL

2023-03-16 19:30:54 3

3 LiteX 框架为创建 FPGA 内核/SoC、探索各种数字设计架构和创建完整的基于 FPGA 的系统提供了方便高效的基础架构。

2023-06-28 09:08:05 425

425

IP_数据表(A-3):Analog-PLL For Frequency Multiplying

2023-07-06 20:13:27 0

0 IP_数据表(A-6):Analog-PLL For Skew adjust

2023-07-06 20:14:06 0

0 IP_数据表(A-9):Analog-PLL For Skew adjust

2023-07-06 20:14:39 0

0 IP_数据表(A-1):Analog-PLL For Frequency Multiplying

2023-07-06 20:16:34 0

0 IP_数据表(A-4):Analog-PLL For Frequency Multiplying

2023-07-06 20:16:44 0

0 IP_数据表(A-7): 用于小数乘法的模拟 PLL

2023-07-06 20:17:04 1

1 在ip目录里搜索pll,选择ALTPLL,点击打开后设置名称并自动保存在目录中。

2023-07-19 16:37:34 665

665

IP(Intellectual Property)是知识产权的意思,半导体行业的IP是“用于ASIC或FPGA中的预先设计好的电路功能模块”。一些常用的复杂的功能模块(如FIFO、RAM、FIR

2023-08-22 15:04:43 1523

1523

pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子技术中广泛应用的一种电路,它的作用是将一个特定频率的输入信号转换为固定频率的输出信号。PLL锁相环的三种配置模式分别为

2023-10-13 17:39:48 1102

1102

电子发烧友App

电子发烧友App

评论