赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

2013-07-23 09:25:53 19707

19707

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。

2019-09-10 15:12:31 6343

6343

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2020-11-21 11:13:01 3278

3278

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期

2020-11-23 13:08:24 3565

3565

时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易

2020-11-10 13:53:41 4795

4795

,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。赛灵思现有的FPGA中没有一款同时包含这四种资源(见表1)。 这四大类中的每一种都针对特定的应用。例如,数字时钟管理器(DCM)适用于实现延迟锁相环(DLL)、数字频率综合器、数字移相器或数字

2021-02-13 17:02:00 2014

2014

7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 当我刚开始我的FPGA设计生涯时,我对明显更小、更不灵活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常简单的时钟规则之一是尽可能只使用单个时钟。当然,这并不总是可能的,但即便如此,时钟的数量仍然有限。

2022-09-30 08:49:26 1326

1326 在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1230

1230 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 655

655

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2023-12-22 09:04:46 875

875

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功能的时钟缓冲器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 400

400

FPGA 在通信领域的应用可以说是无所不能,得益于 FPGA 内部结构的特点,它可以很容易地实现分布式的算法结构,这一点对于实现无线通信中的高速数字信号处理十分有利。

2024-01-24 13:46:33 463

463

(08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2022-02-23 07:26:05

)图3.5 心脏示意图了解了心脏之于人体内部循环系统的作用,反观时钟信号之于FPGA器件,其实也有着异曲同工之妙。伴随着每一次的心跳过程,都有血液的运转和流动;同样的,伴随着每一个时钟脉冲的产生,也都有数字

2019-04-12 01:15:50

嗨,我是FPGA的新手。我想知道我是否可以有一个设计,我的FPGA的外部时钟周期性地打开和关闭。我知道Xilinx FPGA使用数字时钟管理器(DCM)和相位锁(或使用触发器延迟锁定)。因此,我

2019-01-10 10:59:04

,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。赛灵思现有的FPGA中没有一款同时包含这四种资源(见表1)。 这四大类中的每一种都针对特定的应用。例如,数字时钟管理器

2020-04-25 07:00:00

请教一下LabVIEW的大神们,我现在希望用FPGA板卡(PXI-7852R)的多个DIO口输出不同的精确的数字时钟,我能用内置的40MHz衍生成最低2.5M的时钟,利用这个时钟可以通过单周期定时

2013-01-08 20:20:14

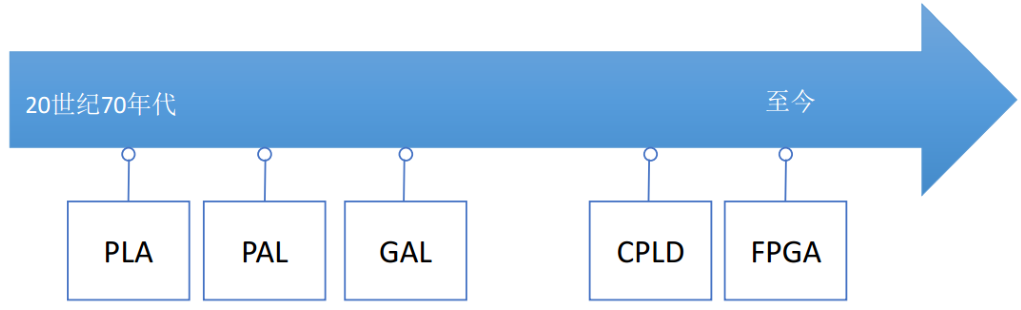

中从电子设计的外围器件逐渐演变为数字系统的核心。伴随着半导体工艺技术的进步,FPGA器件的设计技术取得了飞跃发展及突破。分频器通常用来对某个给定的时钟频率进行分频,以得到所需的时钟频率。在设计数字

2019-10-08 10:08:10

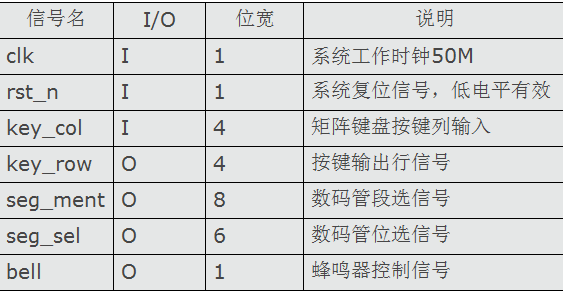

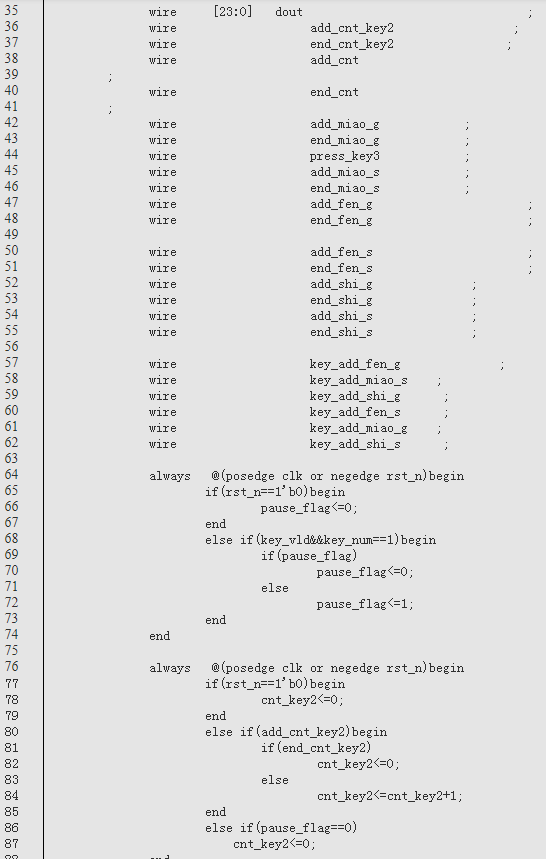

视频过大,打包成8个压缩包基于FPGA设计的数字时钟.part01.rar (20 MB )基于FPGA设计的数字时钟.part02.rar (20 MB )基于FPGA设计的数字时钟

2019-05-14 06:35:34

更多项目/毕设下载和技术交流请加FPGA交流群:97925396视频过大,打包成8个压缩包

2018-11-23 10:31:30

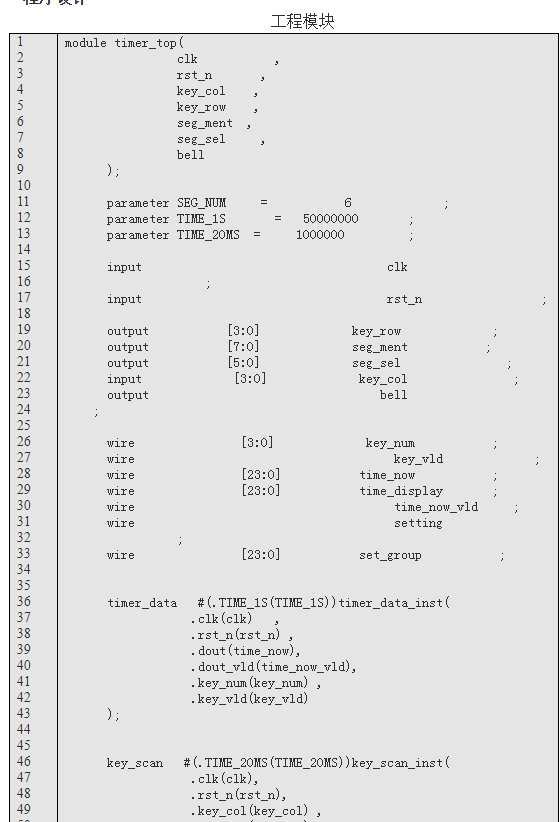

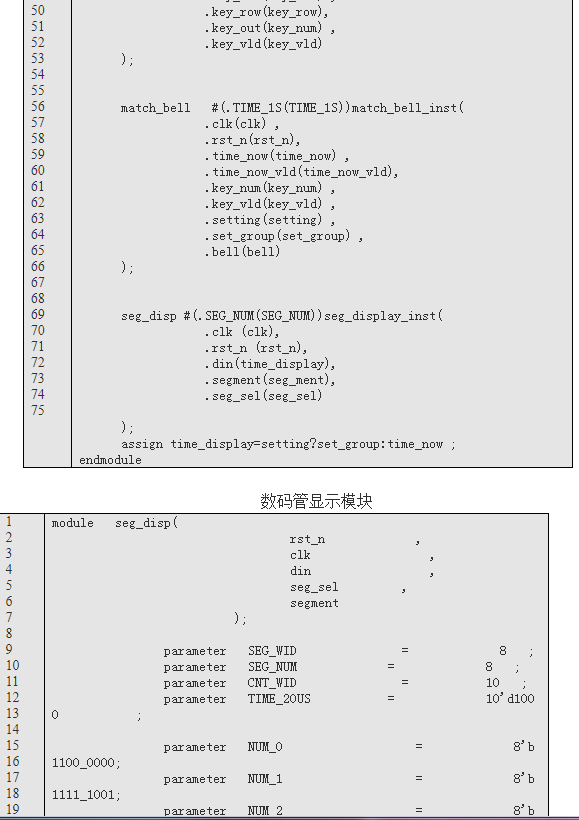

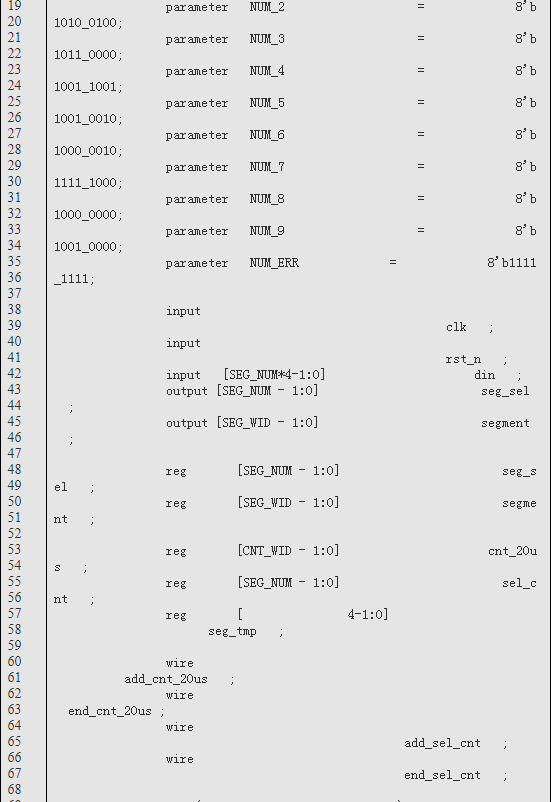

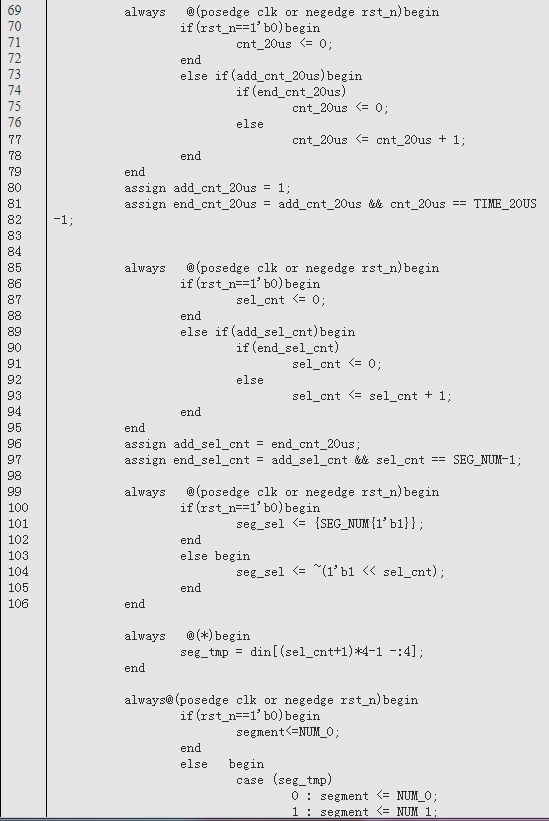

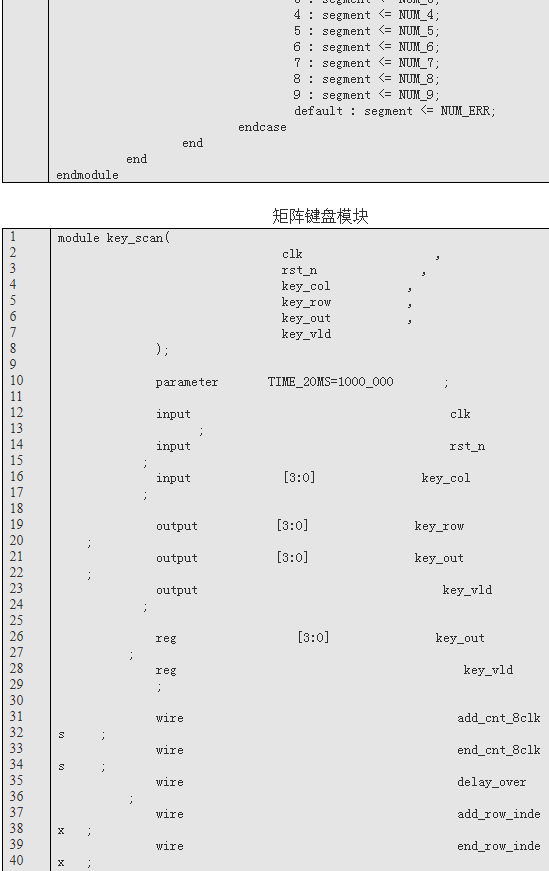

本文属于本人原创,和大家一起学习FPGA,交流FPGA,希望大家多多支持。今天内容为数字时钟设计,详细内容看以下文件,文档为设计文档,project为代码源程序。

2017-09-21 10:46:59

1.FPGA管脚是否具有电平判决功能将输入的模拟时钟信号判决为数字时钟信号?2.单载波输入,LVDS或者LVPECL差分输出方波时钟信号,应该选择什么器件?

2018-12-20 09:31:59

本文详细介绍了基于FPGA 的数字图像采集卡的设计,选用FPGA 和DSP 作为数字信号处理器;然后从单片容量,时钟,体积,控制复杂度几方面综合考虑,选用SDRAM 作为外围存储器;最后

2009-05-30 14:12:18 27

27 在介绍了GPS 同步时钟基本原理和FPGA 特点的基础上,提出了一种基于FPGA 的GPS同步时钟装置的设计方案,实现了高精度同步时间信号和同步脉冲的输出,以及GPS 失步后秒脉冲的平

2009-07-30 11:51:45 40

40 一种FPGA时钟网络中锁相环的实现方案:摘 要:本文阐述了用于FPGA 的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探

2009-08-08 09:07:22 25

25 影响FPGA设计中时钟因素的探讨:时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时

2009-11-01 14:58:33 26

26 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 提出了一种基于FPGA的时钟跟踪环路的设计方案,该方案简化了时钟跟踪环路的结构,降低了时钟调整电路的复杂度。实际电路测试结果表明,该方案能够使接收机时钟快速准确地跟踪发

2010-11-19 14:46:54 31

31 大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 645

645

基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 2890

2890

本文将探讨FPGA时钟分配控制方面的挑战,协助开发团队改变他们的设计方法,并针对正在考虑如何通过缩小其时钟分配网络的规模来拥有更多的FPGA I/O,或提高时钟网络性能的设计者们

2011-03-30 17:16:32 938

938

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 3472

3472

提出了一种基于数字示波器原理,以单片机和FPGA为控制核心的数字示波器实现方法。系统由信号调理、程控放大、比较整形和时钟产生、采样控制、测频模块和校准信号产生等模块组成

2011-10-08 15:31:53 277

277 在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进行了功能验证. 由于数字时钟的通用

2011-11-29 16:51:43 178

178 FPGA 异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA 异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的

2011-12-20 17:08:35 63

63 SERDES在数字系统中高效时钟设计方案,无论是在一个FPGA、SoC还是ASSP中,为任何基于SERDES的协议选择一个参考时钟源都是非常具有挑战性的。

2012-02-16 11:23:43 5384

5384

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1100

1100

2013-12-26 10:33:21 42

42 DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 数字时钟

2016-03-11 16:12:41 70

70 基于FPGA的数字时钟设计,可实现闹钟的功能,可校时。

2016-06-23 17:15:59 64

64 用Verilog写的数字钟,可调小时,分钟,秒,模块化设计,内部消抖,数码管扫描等小模块便于移植,已上板验证通过

2016-08-09 17:12:33 14

14 数字时钟C语音程序

2016-12-17 11:06:10 5

5 一种基于FPGA的时钟相移时间数字转换器_王巍

2017-01-07 22:23:13 2

2 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 业内大多数FPGA 均提供数字时钟管理( 赛灵思公司的全部FPGA 均具有这种特性)。赛灵思公司推出最先进的FPGA 提供数字时钟管理和相位环路锁定。相位环路锁定能够提供精确的时钟综合,且能够降低抖动,并实现过滤功能。

2017-02-11 17:01:11 1625

1625

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校的本科生,跨时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2017-11-15 20:08:11 13066

13066 介绍一种采用FPGA(现场可编程门阵列电路)实现SDH(同步数字体系)设备时钟芯片设计技术,硬件主要由1 个FPGA 和1 个高精度温补时钟组成.通过该技术,可以在FPGA 中实现需要专用芯片才能实现的时钟芯片各种功能,而且输入时钟数量对比专用芯片更加灵活,实现该功能的成本降低三分之一.

2017-11-21 09:59:00 1840

1840

无沦是用离散逻辑、可编程逻辑,还是用全定制硅器件实现的任何数字设计,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压或制造工艺的偏差情况下将导致错误的行为,并且调试困难、花销

2017-11-25 09:16:01 3907

3907

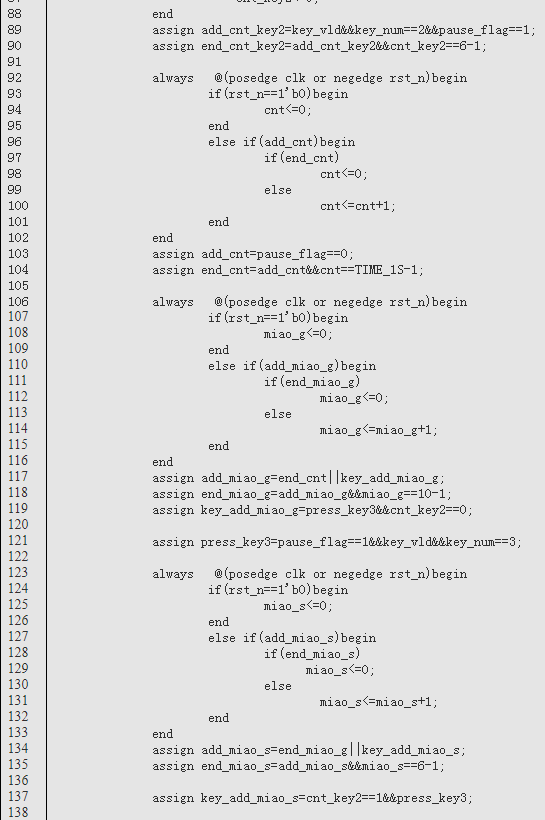

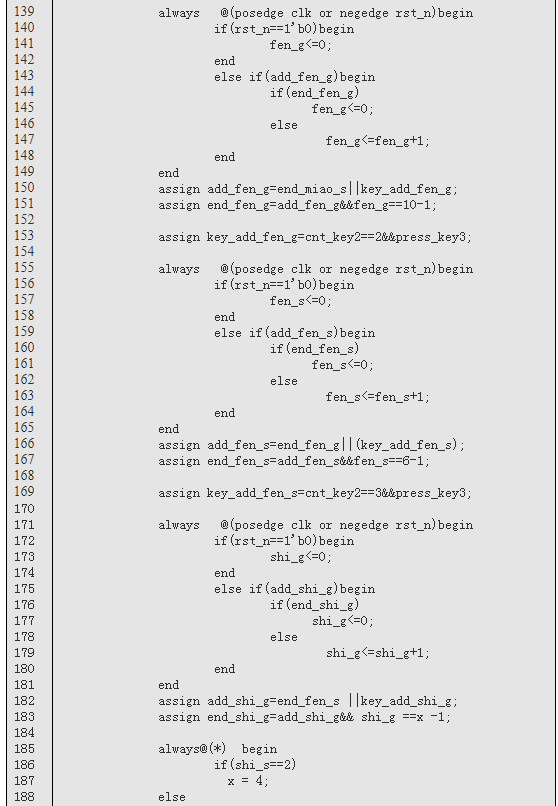

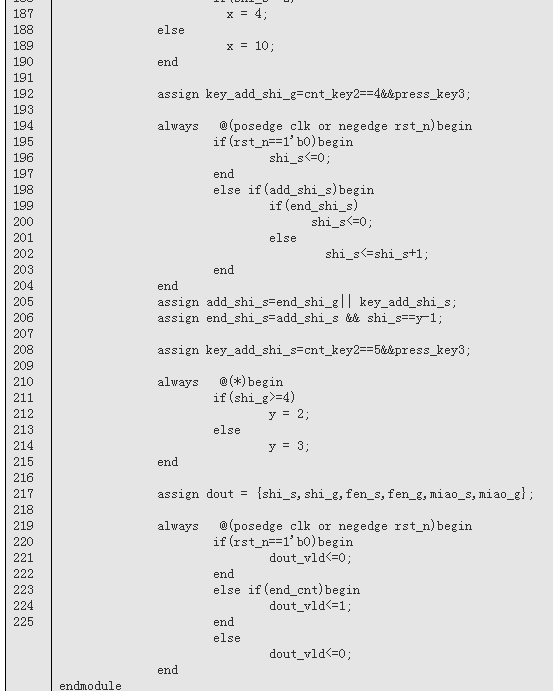

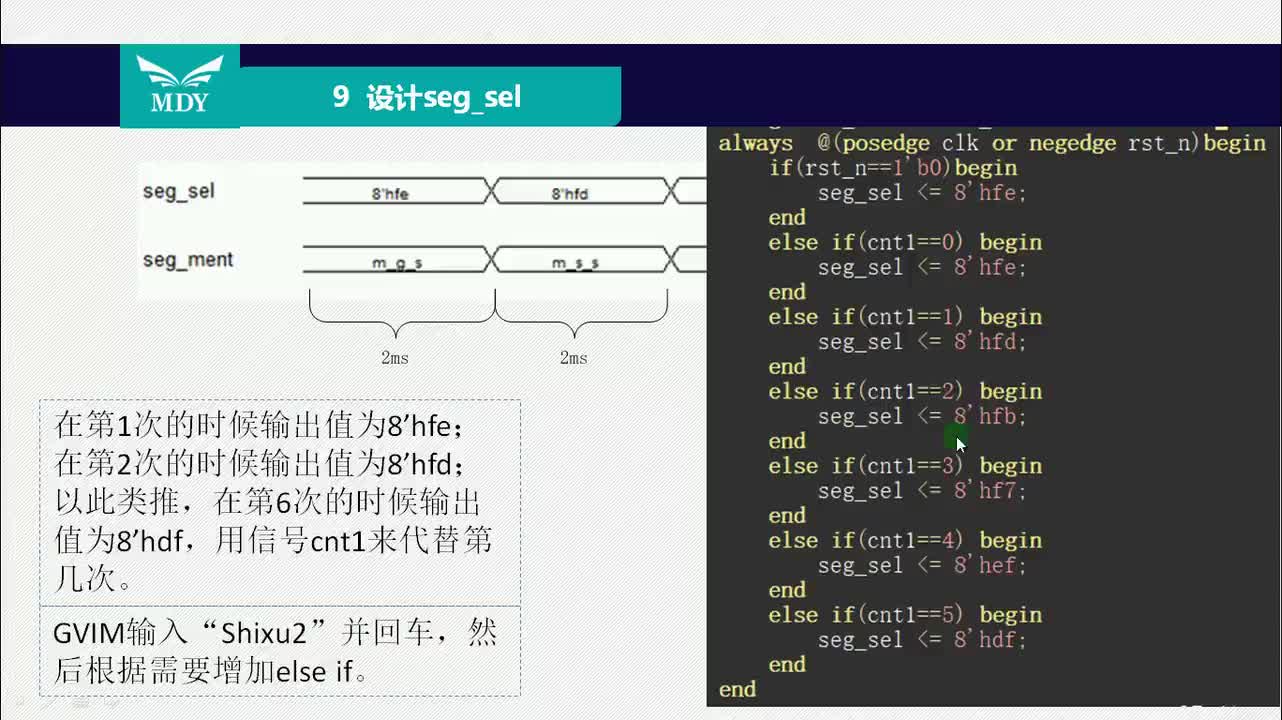

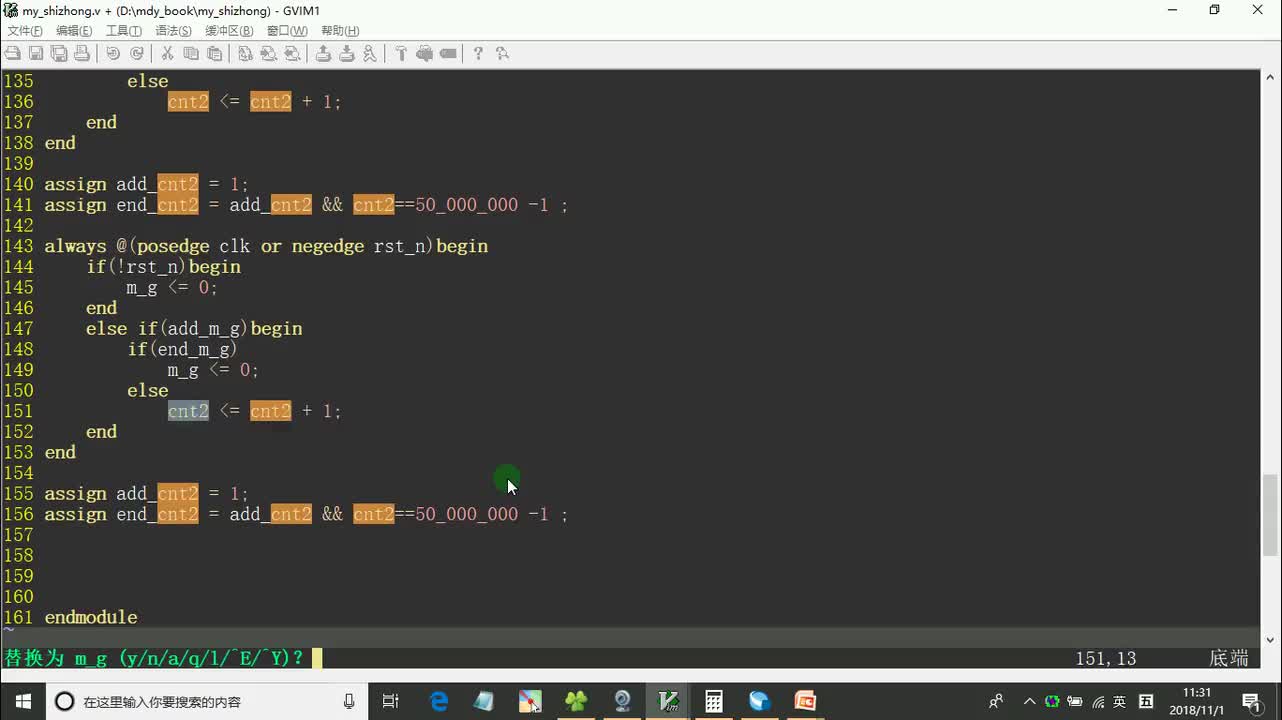

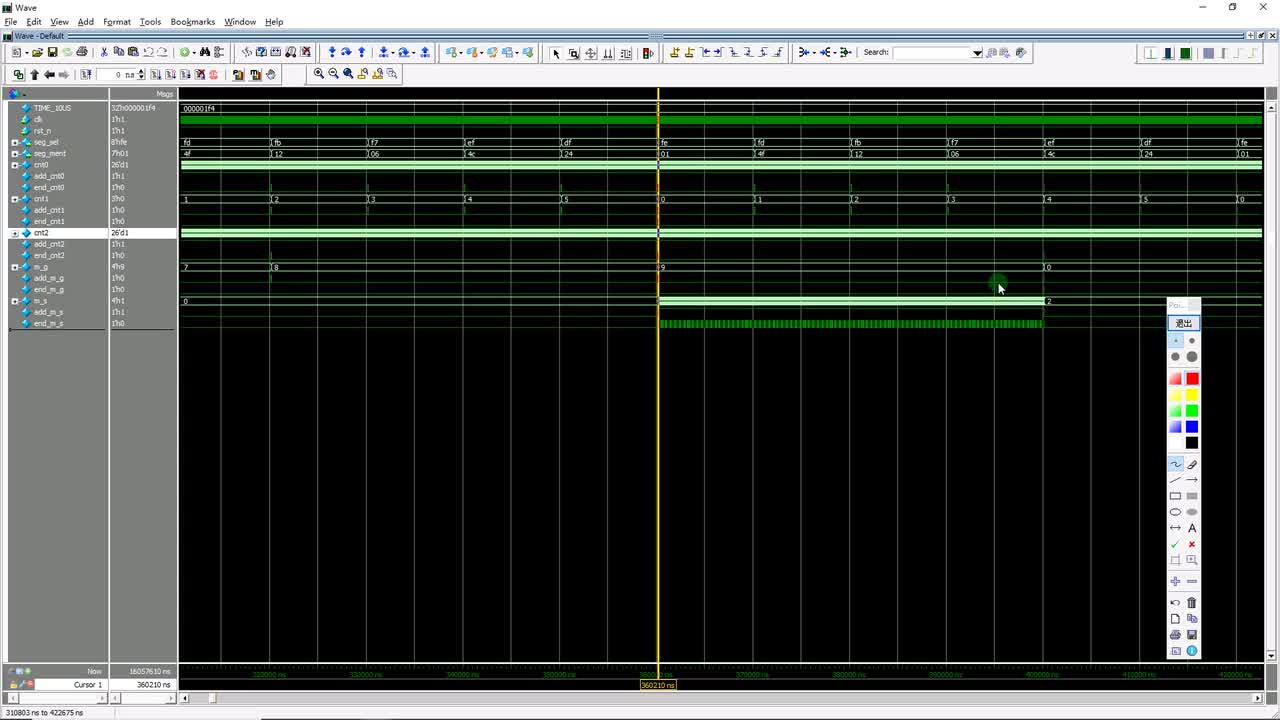

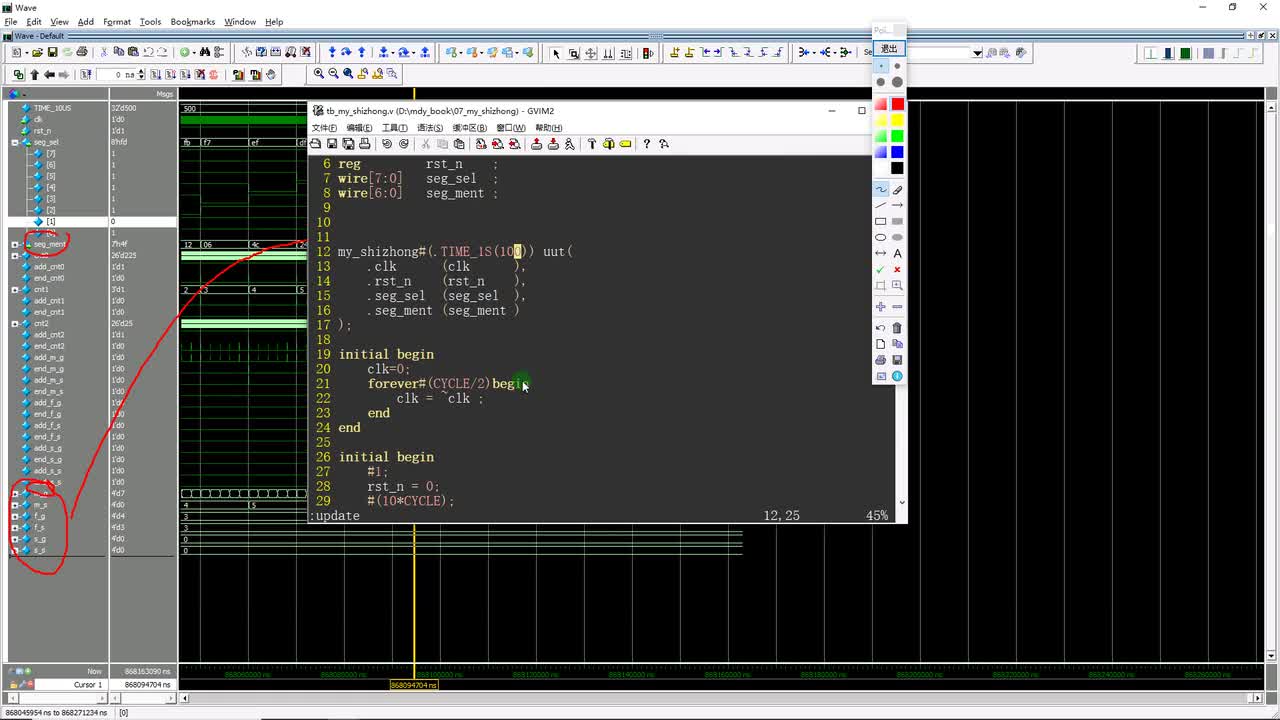

以秒个位这个计数器为例,这个计数器加1的条件是什么呢?到了1秒就加1。那我们怎么知道1秒钟时间到了呢?FPGA是通过数时钟周期数来确定时间的。例如下图,假设时钟频率是50MHz,即时钟周期是20ns

2018-05-24 10:45:00 4870

4870

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟

2018-09-01 08:29:21 5302

5302

跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 2854

2854 时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18 5065

5065

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2020-09-24 10:20:00 2487

2487

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 2550

2550 。 不要随意将内部信号作为时钟,如门控时钟和分频时钟,而要使用CLKDLL或者DCM产生的时钟,或者可以通过建立时钟使能或者DCM产生不同的时钟信号。 FPGA尽量采取同步设计,也就是所有时钟都是同一个源头,如果使用两个没有相位关系的异步时钟,必须

2020-12-11 10:26:44 1482

1482 跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。 这里主要介绍三种

2022-12-05 16:41:28 1324

1324 对于 FPGA 来说,要尽可能避免异步设计,尽可能采用同步设计。 同步设计的第一个关键,也是关键中的关键,就是时钟树。 一个糟糕的时钟树,对 FPGA 设计来说,是一场无法弥补的灾难,是一个没有打好地基的楼,崩溃是必然的。

2020-11-11 09:45:54 3656

3656 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 15

15 引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们

2021-03-22 10:09:58 11527

11527

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 EDA技术使得电子线路的设计人员能在计算机上完成电路的功能设计、逻辑设计、时序测试直至印刷电路板的自动设计。本文介绍了以 VHDL 语言和硬件电路为表达方式,以 Quartus II 软件为设计工具,最终通过 FPGA 器件实现数字时钟的设计过程。

2021-05-25 16:28:10 35

35 利用数字电子技术、EDA设计方法、FPGA等技术,设计、仿真并实现一个基于FPGA的数字电子时钟基本功能,其基本组成框图如图1所示,振荡器采用ALTERA的DE2-70实验板的50MHz输出,分频器

2021-05-28 10:47:50 42

42 基于FPGA的数字时钟设计毕业设计论文免费下载。

2021-05-28 10:49:19 56

56 有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2021-09-23 16:39:54 2763

2763 (10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 (08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA时钟设计原则1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟设计原则5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 (29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:48 10

10 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 电子发烧友网站提供《使用FPGA的数字时钟(计时表).zip》资料免费下载

2022-11-23 10:38:36 5

5 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 686

686

跨时钟域是FPGA设计中最容易出错的设计模块,而且一旦跨时钟域出现问题,定位排查会非常困难,因为跨时钟域问题一般是偶现的,而且除非是构造特殊用例一般的仿真是发现不了这类问题的。

2023-05-25 15:06:00 1150

1150

FPGA多bit跨时钟域适合将计数器信号转换为格雷码。

2023-05-25 15:21:31 1953

1953

时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构、没有 CDC 问题并正确进行约束设计,就可以减少与工具斗争的时间。

2023-07-12 11:17:42 794

794

景下的时序要求。尤其对于需要高速数据传输、信号采集处理等场景的数字信号处理系统而言,FPGA PLL的应用更是至关重要。本文将介绍FPGA锁相环PLL的基本原理、设计流程、常见问题及解决方法,以及该技术在外围芯片时钟提供方面的应用实例。 一、FPGA锁相环PLL基本原理 1.时钟频率的调

2023-09-02 15:12:34 1319

1319 fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据? 在FPGA设计中,通常需要跨时钟域进行数据通信。跨时钟域通信就是在不同的时钟域之间传输数据。 当从一个时钟域传输数据到另一个时钟

2023-10-18 15:23:51 578

578 FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢? FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据不同需要编程,实现不同的功能。在FPGA

2023-10-25 15:14:20 1045

1045 FPGA(可编程逻辑门阵列)是一种集成电路芯片,具有可编程的数字逻辑功能。多功能数字钟系统利用FPGA技术实现了时钟的显示、计时、报时等功能。本文将详细介绍FPGA多功能数字钟系统

2024-01-02 16:50:57 252

252 FPGA输入的时钟信号必须是方波么?正弦波会有影响么? FPGA是一种可编程逻辑器件,通常用于实现数字电路。输入时钟信号是FPGA中非常重要的时序信号,对整个系统的稳定性和性能都有很大

2024-01-31 11:31:42 1244

1244

电子发烧友App

电子发烧友App

评论