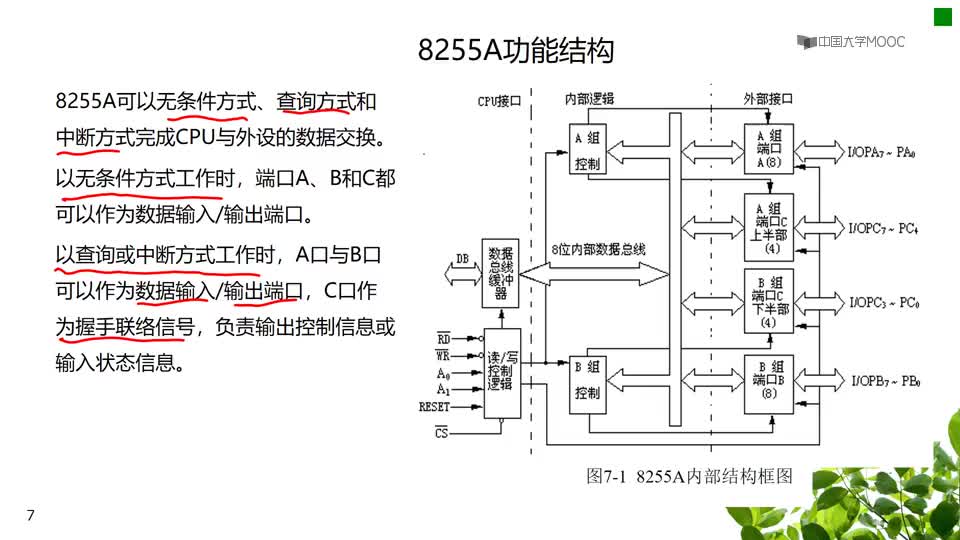

针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2013-11-28 18:49:00 12149

12149

DCM一般和BUFG配合使用,要加上BUFG,应该是为了增强时钟的驱动能力。DCM的一般使用方法是,将其输出clk_1x接在BUFG的输入引脚上,BUFG的输出引脚反馈回来接在DCM的反馈时钟

2018-05-11 03:53:00 1566

1566 随着FPGA设计越来越复杂,芯片内部的时钟域也越来越多,使全局复位已不能够适应FPGA设计的需求,更多的设计趋向于使用局部的复位。本节将会从FPGA内部复位“树”的结构来分析复位的结构。 我们的复位

2019-02-20 10:40:44 1068

1068

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。

2019-09-10 15:12:31 6343

6343

线将会是一个和时钟一样多扇出的网络,如此多的扇出,时钟信号是采用全局时钟网络的,那么复位如何处理?有人提出用全局时钟网络来传递复位信号,但是在FPGA设计中,这种方法还是有其弊端。一是无法解决复位结束

2019-05-17 08:00:00

FPGA的任意一个管脚都可以作为时钟输入端口,但是FPGA专门设计了全局时钟,全局时钟总线是一条专用总线,到达片内各部分触发器的时间最短,所以用全局时钟芯片工作最可靠,但是如果你设计的时候时钟太多

2012-02-29 09:46:00

)复位电路的设计也很有讲究,一般的设计是期望系统的复位状态能够在上电进入稳定工作状态后多保持一点时间。因此,阻容复位电路可以胜任一般的应用;而需要得到更稳定可靠的复位信号,则可以选择一些专用的复位芯片

2019-04-12 06:35:31

现了,将时钟的布线成树形结构,使得到达每一个逻辑单元的时钟信号同相,这样就可以实现同步,这就是全局时钟网络,GC_CLK。也就是说GC_CLK在FPGA内部是固定的位置,与其对应的引脚也就固定了,这样

2019-07-09 08:00:00

FPGA的全局时钟是什么?什么是第二全局时钟?在FPGA的主配置模式中,CCLK信号是如何产生的?

2021-11-01 07:26:34

的时钟信号源一般来自外部,我们通常使用晶体振荡器(简称晶振)产生时钟信号。当然了,一些规模较大的FPGA器件内部都会有可以对时钟信号进行倍频或分频的专用时钟管理模块,如PLL或DLL。由于FPGA器件内部

2019-04-12 01:15:50

的时钟和复位通常是需要走全局时钟网络的。如图3.17所示,这是Cyclone III器件的内部全局时钟网络的布局示意图。如果说一个城市当中的各种羊肠小道、普通马路是FPGA器件内部的一般布线资源,那么

2015-04-24 08:17:00

的时钟源是来自于FPGA的PLL。为什么PLL输出的时钟一定要有专门的这样一对引脚呢?和前面的全局时钟网络存在的意义有异曲同工之妙。PLL到这对引脚上的延时相对是比较受控的,目的就是为了得到更低延时、更稳

2015-05-04 11:45:05

和说明,其实这也是FPGA的I/O引脚灵活的体现,对于一般的信号,FPGA的I/O可以随意的连接。(特权同学,版权所有)图3.42 核心板引出的两个插座电路 `

2015-05-06 11:31:16

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面写FPGA的BANK1,3连接外部存储控制器(如下图,且只有四个BANK),所以要将DDR3连接在BANK3上。所以DDR3如何与FPGA芯片

2021-11-29 16:10:48

FPGA时钟问题 2010-06-11 15:55:39分类: 嵌入式1.FPGA的全局时钟是什么?FPGA的全局时钟应该是从晶振分出来的,最原始的频率。其他需要的各种频率都是在这个基础上利用PLL或者其他分频手段得到的。

2021-07-29 09:25:57

电路的设计中,毛刺的长度一般情况下>1个时钟周期,3.2 异步复位同步释放在有些应用中,复位信号需要在时钟尚未给出或不稳定的情况下传到后级,在时钟稳定之后,再撤去复位信号。此时需使用异步复位来实现

2021-06-30 07:00:00

一、FPGA配置引脚说明 1、CFGBVS 如果VCCO0连接至2.5V或3.3V,CFGBVS连接至VCCO0。 如果VCCO0连接至1.5V或1.8V,CFGBVS连接至GND

2021-01-15 16:43:43

本人测量dip8封装出来的vdmos的导通电阻,测出来的结果比仿真大了4倍左右,大概在80mΩ左右(仿真结果为18mΩ),用的还是四线法测试,所以我想问一下有大神知道dip8封装的引脚上大概有多大的电阻,是不是有几十mΩ?

2017-02-14 17:29:27

所谓亚稳态,是指“trecovery(recovery time)指的是原本有效的异步复位信号释放(对低电平有效的复位来说就是上跳沿)与紧跟其后的第一个时钟有效沿之间所必须的最小

2012-01-12 10:45:12

FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select

2019-10-22 06:01:34

。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。常见的复位方式有三种1、硬件开关:复位信号接一个拨码开关或按键,.

2021-11-11 06:06:08

引脚上产生耦合的情形是怎么样的?

2021-04-07 06:02:58

菜鸟一枚,刚刚学西FPGA,请教两个问题:1,为什么复位引脚需要接到时钟引脚E15上,这不是一直在复位吗? 2 我将时钟引脚从E1换成了E16,跑马灯就不亮了,为什么

2015-09-06 12:41:50

,并且能够维持各输出时钟之间的相位关系,即零时钟偏差。DCM一般和BUFG配合使用,要加上BUFG,应该是为了增强时钟的驱动能力。DCM的一般使用方法是,将其输出clk_1x接在BUFG的输入引脚上

2018-08-31 09:08:22

我是这里的新手。我购买了一块 STM32G071 Nucleo-64 开发板。我希望将它连接到 5 伏信号。预期的接口引脚是 PB1、PB3 和 PB4。绝对最大额定值 VIN 状态:-1

2023-01-06 06:21:32

的上升时间缓慢或外部驱动处于低电平),系统将继续保持复位状态。一旦检测到 RESET_B 引脚为高电平,内核时钟将启用,系统从复位状态释放。因此,如果发生缓慢的上升时间(可能是由复位线上的大值上拉电阻

2023-04-07 07:13:53

以下(前30个)非时钟加载引脚。这不是Spartan-6中推荐的设计实践,因为全局布线的限制可能导致过度延迟,歪斜或不可路由的情况。建议仅使用BUFG资源来驱动时钟负载。如果您希望覆盖此建议,可以

2020-05-20 08:56:06

专用的全局时钟输入引脚驱动单个主时钟去控制设计项目中的每一个触发器。同步设计时, 全局时钟输入一般都接在器件的时钟端,否则会使其性能受到影响。 对于需要多时钟的时序电路, 最好选用一个频率是它们

2012-03-05 14:29:00

上以太网PHY芯片的GMII_GTX中信号并没有连接到该引脚,这样改,警告是没了,但是功能怕也是没咯)。要两者都能保证,只能改硬件板卡了耶。不过根据Intel官网上一些工程师的说法,这个警告其实一般

2020-02-20 14:41:06

第一次先进行软件复位,第二次正常运行,不知道怎么设置标志位 系统复位将复位除时钟控制寄存器CSR中的复位标志和备份区域中的寄存器以外的所有寄存器 @1、备份区域中的寄存器if(BKP->

2015-03-02 14:09:33

AD9280三态引脚是否只是控制数据输出端的,和转换过程没有关系?现在问题是FPGA引脚不够用了,能否将两片AD9280数据D0-D7接在一起,时钟是共用的,两片AD同步输出,在数据开始输出后用三态引脚控制取数?

2019-01-09 09:30:29

到额外的时钟脉冲)时,我们在FPGA引脚的GPMC_CLK信号上添加了一个510欧姆的下拉电阻。大大减少了问题但没有消除它。小电阻应该消除任何串扰。然后,我们在该FPGA引脚处添加了一个220pF电容

2019-08-08 06:49:12

大家好,我有一个旧的电路板运行在+5 V,并有PIC18F46K22上,它的X2 UART端口使用。我看到两个电阻值470欧姆每个串联连接在RXD和TXD引脚之前,这些引脚出来的连接器。我想知道

2018-11-02 15:05:31

与PA1短接。(用户也可另外连接一个时钟信号到PA1引脚上。)代码见下:int main(void){unsigned char i_Loop;unsigned char n_Counter;#ifdef DEBUGdebug();#endi...

2021-08-18 07:53:57

引脚输入的时钟信号,在FPGA内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是非常实用。FPGA的时钟和复位

2016-08-08 17:31:40

输入都有专用引脚,通过这些专用引脚输入的时钟信号,在FPGA内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是

2017-10-23 20:37:22

PlanAead引脚分配这个例程的顶层源码里有3个接口,即:input ext_clk_25m, //外部输入25MHz时钟信号input ext_rst_n,//外部输入复位信号,低电平有效output reg

2018-02-27 21:50:07

我想知道是否有可能使用SCK1在另一个引脚上创建新的SPI时钟信号,而第一个时钟周期丢失?我用的是MHC和SPI外围设备。

2020-04-29 06:25:31

FPGA:xc7v585tffg1761就像时钟一样,有很多GCLK引脚。我不知道它是否有全局复位引脚。谢谢

2020-06-17 08:07:03

,CMPCLK_2,CMPMOSI_2,MOSI_CSI_B_MISO,CSO,GCLK_TRDY等。一些Pin描述说您可以将引脚用作常规用户I / O,但有些则不然。例如: GCLK:这些时钟引脚连接到全局时钟

2019-04-23 06:55:23

在我们的设计中,BPI-up模式用于Virtex 5配置。在这种情况下,并行闪存的复位通过外部上拉电阻直接连接到FPGA的program_b引脚。此连接应足以进行正确配置。但是在prog_b引脚

2019-01-23 06:10:35

数字电路中,时钟是整个电路最重要、最特殊的信号:因此, 在FPGA设计中最好的时钟方案是:由专用的全局时钟输入引脚驱动单个主时钟去控制设计项目中的每一个触发器。同步设计时,全局时钟输入一般都接在器件的时钟端, 否则会使其性能受到影响。

2012-05-23 19:51:48

需要20个。任何人都可以建议如何在不使用BUFG的情况下从全局时钟引脚转换到FPGA逻辑?我已经咨询过UG382第30页的一些想法,但仍然无法弄清楚如何避免BUFG。谢谢拉克兰。Lachlan

2019-07-01 10:20:35

个全局时钟引脚(引脚号30,32和38)。如果我使用一个说30引脚,我可以为整个IC提供时钟(我只需要一个工作频率)。如果是这样,我应该怎么处理PCB中的其他引脚 - 让它们保持未连接状态?我不想在我

2019-08-06 06:29:01

)和Virtex-5 FPGA封装和引脚规范(ug195)。在in347文件中定义了许多全局时钟引脚,但是如何在板上找到这些引脚的物理位置。 你们可以向我推荐一些文件或链接,其中包含更多关于引脚物理位置的详细信息。非常感谢你

2019-08-23 12:48:42

我在 arduino IDE 中使用 ESP 12-e 模块。我想在我的引脚上生成时钟和数据以与自定义设备通信。是这样的:

这是我的相关代码:

代码:全选pinMode(CLK , OUTPUT

2023-05-30 07:29:44

根据一些WP文档,最佳编码实践不是尽可能使用全局重置?这里有一个问题,如果没有复位引脚,如何复位FPGA,每次想要复位时都要关闭FPGA!以上来自于谷歌翻译以下为原文According

2019-04-18 14:19:27

嗨,大家好, 我是FPGA的新手,有一个简单的问题可能需要你的帮助。我有一个Virtex 5 ML506 XC5VLX50T板,我想找到一些golbal时钟IO引脚。我检查了用户指南文件(ug347

2020-06-08 14:18:44

个使用芯片输入--电路补偿功能),PLL级联使用(FPGA只有一个时钟引脚输入即可--无电路补偿功能) h、时钟网路:全局时钟网络(时钟输入引脚--不同引脚上不同Pll进行时钟补偿)---局部时钟网路(也有专用的时钟输入引脚-可当作IO使用-一般不用此功能)

2018-08-24 09:31:16

一.舵机的接线如果是两白一黑,则黑为GND,中间也是VCC,旁边是信号线。(信号线连接在stm32上能够输出PWM的引脚上----)二.使用原理舵机的控制一般需要一个20ms的脉冲,角度对应如下:t

2021-08-12 07:12:59

我正在用PIC18F45 K20工作。我有一个板与外部振荡器连接到RA2。这并不打算是一个校准引脚,但我被要求一些如何计数这个引脚上的振荡。我可以将外部振荡器配置为时钟RA2,但我很困惑如何在RA2

2019-11-04 10:51:45

以下是关于AN5439关于外部晶体振荡器的摘录:如果没有使用MHz或KHz ECO,ECO引脚上的外部时钟信号可以使用KHz或MHz的晶体输入引脚将外部时钟信号路由到ECO时钟网络上。这允许使用这些

2019-07-17 14:14:54

大家好,如果两个FPGA连接在单个JTAG链中。那么DONE和INIT引脚的推荐连接是什么。两个FPGA的INIT引脚(也是DONE引脚)是应该连接在一起还是应该分开?Xilinx是否为此推荐了任何

2019-01-10 11:00:55

任务的特殊网络 - 全局设置/重置。配置完成后,该线路被置低,以允许FPGA开始其新编程的功能。假设这是正确的,那么我理解。在我的VHDL中,如果我有一个简单的顶级模型,其中一个进程对时钟和复位信号很

2019-05-17 11:24:19

gpio引脚n_LED1,(在芯片引脚连接中,同名网络(net)表示连接在一起),n表示低电平有效,低电平时灯亮。n_LED1连接GPF4,对于引脚的设置一般分为两步首先设置为输出或者输入引脚,其次...

2021-11-05 07:28:24

我知道当你有一个单端时钟作为输入时,你需要将它连接到全局时钟的P引脚。当你有一个单端输出时钟时,你能把它放在N引脚上吗?谢谢

2020-06-02 09:00:58

将这个时钟放在FPGA引脚上,然后使用单个DCM,我可以产生一个40 MHz的时钟。然后,我将这个时钟从FPGA发送到我必须测试的ASIC芯片。问题是输出clk(clk_40)看起来像一个正弦波,而我

2019-05-22 14:43:40

我想在LCD引脚上移动数据,它连接在PIN号12、13和15端口上,将为PORTB提供逻辑工作,引脚0到7,然后12到15引脚。我使用的是P24FJ64 GC010控制器 以上来自于百度翻译 以下

2019-03-20 08:56:36

引脚上面出现了如图的绿叉,网上查了说设置最小间距,但是我改了0也没用,甚至两个电阻电容之间的互联也有这种问题另外再问一个相关的,我用的芯片引脚间距可能阻焊层比较近,一开始都是绿的,经测试要7mil间距一下这些引脚才能正常,但是我的连接线要10mil,会不会有什么问题

2019-08-05 01:25:33

怎样将FPGA时钟引脚作为普通输入引脚设置,在软件中怎样设置?求解答{:2:}

2013-05-21 20:11:34

数模转换芯片的参考电压引脚一般怎么接

2016-05-03 16:22:49

有一篇文章说fpga的时钟周期一般采用整偶数,这个有什么...

2014-03-16 19:34:02

fpga剩下7个引脚,全是clk,只能做输入,想接收16个移相器的16个状态,一般需要8个脚,有没有别的写法,用7脚就可以搞定的?一般的话,16个移相器要4位,16种状态要4位,8位就很舒服了,可是刚好少一位,请教论坛高人指点下!说下思路或者写法,我现在用verilog hdl!

2011-06-22 16:13:54

FPGAXCKU085FLVA1517-2-e的哪个引脚连接到系统时钟?我们正在使用这个FPGA -https://www.xilinx.com/products/boards-and-kits

2019-10-11 06:34:46

请问一般单片机芯片的AD脚的AREF引脚需不需要接一个5V电源?还是说它里面已经本身有基准电压了?比如单片机ATMEGA128,内部AD有自带基准电压吗?因为如果在AREF引脚上接一个5V电源作为基准电压的话万一5V电源有波动那就比较麻烦了。

2023-04-19 16:37:43

大家好, 我的项目只有一个来自FPGA外部的clk。我将它分配给GCLK引脚。该引脚是否自动连接到IBUFG?就我而言,当我将DCM与核心生成器一起使用时,它将生成一个IBUFG。那是: GCLK

2020-06-11 16:15:14

计算FPGA外部引脚的频率。我需要将其与内部FPGA时钟同步吗?内部参考时钟以60Mhz运行,外部频率在10khz到15khz之间变化,不同步的外部频率是否会导致错误或问题?以上来自于谷歌翻译以下

2019-06-18 09:37:29

PCB板子已经发给厂家了,改不回来了,真是怪自己还没优化好程序,就急急忙忙的把板子发出去了。 复位信号必须接到Libero soc支持的芯片的全局引脚,我接到了个普通IO,在开发环境中分配引脚

2018-01-07 22:31:39

你好,我是一个在PSoC上工作的新手。当我试着运行PSoC 4 BLE来控制一个传感器时,发生了一些奇怪的事情。复位引脚需要低到地面一般,并上下发送下降沿作为复位信号。我用数字输出引脚与强大的驱动

2019-09-26 12:12:30

使用13.单端SMA时钟输入和14.差分SMA全局时钟输入。但是,由于在第14个引脚中使用了j16和j17,因此不会出于任何原因给出数据。原始(AF 19,K18,AH15,AG15)4针用于与dac

2020-07-08 13:34:00

你好,我使用的是zc706评估板。我正在尝试将我的主板与RF卡连接,我有以下问题。我试图在一个引脚上驱动一个时钟,但它似乎没有工作。 Ι用示波器测量输出引脚。 Fyi,我将zynq处理系统的主时钟

2019-09-26 08:16:13

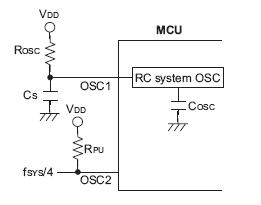

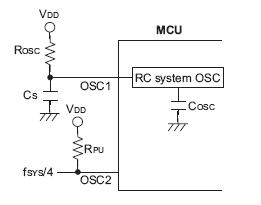

单引脚上拉电阻型RC振荡器

以下是外接上拉电阻的RC振荡器电路。

2008-10-24 16:03:11 1209

1209

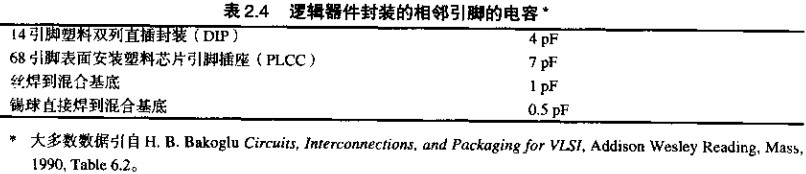

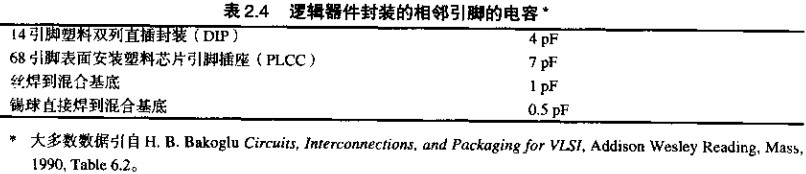

逻辑器件相邻引脚之间的寄生电容能够在敏感的输入法引脚上耦合出噪声电压。图2.21描述了一个互容CM使得逻辑器件中引脚1和引脚2产生耦合的情形。

2010-06-02 17:40:19 1291

1291

FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的

2010-09-10 17:25:27 2175

2175 目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-02-11 11:34:11 4223

4223 在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。

2017-02-11 11:46:19 876

876

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8891

8891

在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 5125

5125

引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们

2021-03-22 10:09:58 11527

11527

。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。常见的复位方式有三种1、硬件开关:复位信号接一个拨码开关或按键,.

2021-11-06 09:20:57 20

20 补偿 NCP1250 OPP 引脚上的负电压尖峰

2022-11-15 19:51:47 0

0 如何测量 SLA 引脚上的 Bemf

2022-11-15 20:21:59 0

0 建议采用一个PCB小板(单独做一个PCB进行转接)进行转接,再把PCB小板与连接器引脚进行焊接,再把线缆焊接在小板上面,PCB小板走线过流需要保证厚度,同时点AB胶固定线缆。

2023-08-22 10:21:16 659

659

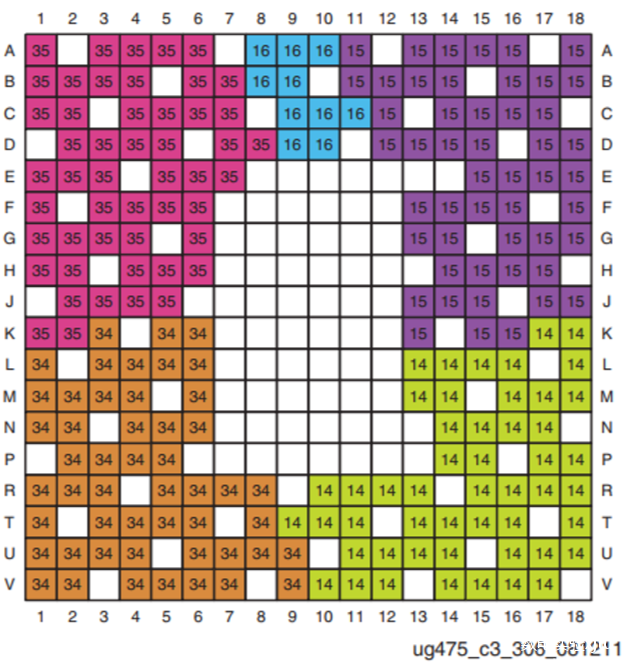

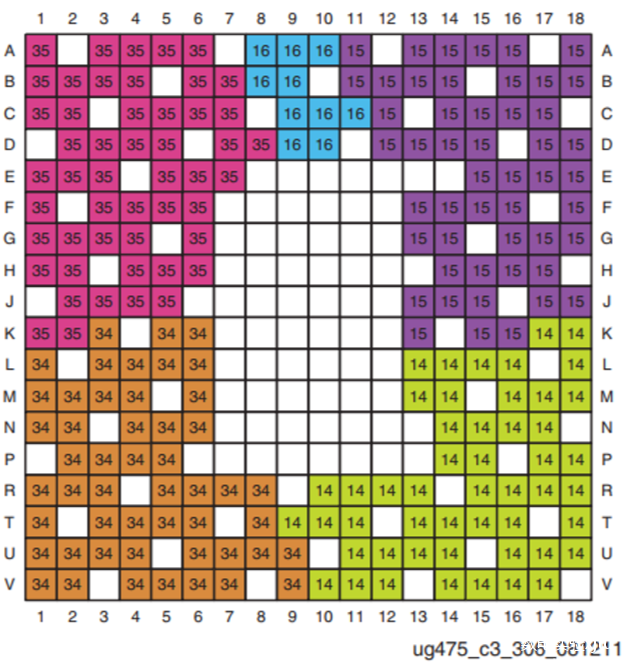

FPGA的引脚排布在芯片背面,以EGO1板载芯片XC7A35T-1CSG324C 为例,下图中每个小格代表一个引脚,共有18行18列,共324个引脚。

2023-09-17 15:09:15 1781

1781

不断变革创新,就会充满青春活力;否则,就可能会变得僵化。——歌德干货时间来了,关注小欣本期分享,我们一起来学习吧!连接器引脚上锡不良主要表现为引脚下表面与焊点相接不良或不相接,那么导致失效的原因究竟

2023-12-16 08:03:06 494

494

电子发烧友App

电子发烧友App

评论