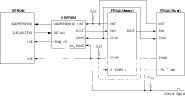

现场可编程门阵列(FPGA)作为专用集成电路(ASIC)领域的一种半定制电路,可以根据设计的需要灵活实现各种接口或者总线的输出,在设备端的通信产品中已得到越来越广泛的使用。##在设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示。

2015-01-30 16:54:39 2847

2847 本文描述了复位的定义,分类及不同复位设计的影响,并讨论了针对FPGA和CPLD的内部自复位方案。

2016-07-11 14:33:49 6228

6228

的面阵CCD驱动时序发生器设计,基于CPLD的面阵CCD驱动时序发生器设计及其硬件实现,基于CPLD的线阵CCD驱动电路的设计,基于CPLD的线阵CCD驱动电路设计与实现,基于CPLD的线阵CCD驱动

2019-06-03 16:45:25

。同样,CPLD XC9500是否有任何序列?我所理解的是.jed文件是在SHIFT-DR状态下而不是.bit文件传输的。它是否正确?传输.jed文件后,XC9500是否还需要JSTART指令并切换

2019-01-15 09:47:43

它们的基本设计方法是借助于 EDA 设计软件,用原理图、状态机和硬件描述语言等方法,生成相应的目标文件,最后用编程器或下载电缆,由 CPLD/FPGA 目标器件实现。 生产 CPLD/FPGA

2019-03-04 14:10:13

words:FPGA/CPLD;Synchronous design;Clock;Metastable state利用FPGA/CPLD实现数字系统电路设计时,如何设计出可读性强、重复利用率高、工作稳定可靠

2009-04-21 16:42:01

FPGA与CPLD的辨别和分类主要是根据其结构特点和工作原理。通常的分类方法是:将以乘积项结构方式构成逻辑行为的器件称为CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列

2019-07-01 07:36:55

CPLD的电路规模、功能、性能等方面强化之后的产物。(特权同学版权所有)一般而言, FPGA与CPLD之间的区别如表1.1所示。(特权同学版权所有)表1.1 FPGA和CPLD的比较总而言之,FPGA

2019-02-21 06:19:27

可以很快进入市场。许多设计人员已经感受到CPLD容易使用、时序可预测和速度高等优点,然而,在过去由于受到CPLD密度的限制,他们只好转向FPGA和ASIC。现在,设计人员可以体会到密度高达数十万门

2012-10-26 08:10:36

地说,FPGA就是将CPLD的电路规模,功能,性能等方面强化之后的产物。

一般而言,CPLD与FPGA之间的区别的如下所示(当然也有例外)。

PLD : Programmable Logic

2011-09-27 09:49:48

规模的不断增大,工作 频率的不断提高,将会给电路引入许多分布参数的影响,而这些影响用软件模拟的方法较难反映出来,所以有必要做硬件仿真.FPGA就可以实现硬件仿真以做成模型机.将软件模拟后的线路经一定

2020-08-28 15:41:47

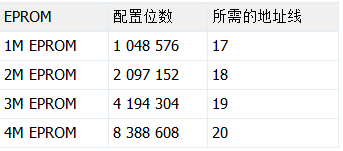

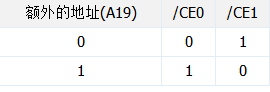

现场可编程门阵列(FPGA)作为专用集成电路(ASIC)领域的一种半定制电路,可以根据设计的需要灵活实现各种接口或者总线的输出,在设备端的通信产品中已得到越来越广泛的使用。1 FPGA 常用配置方式

2019-07-12 07:00:09

现场可编程门阵列(FPGA)作为专用集成电路(ASIC)领域的一种半定制电路,可以根据设计的需要灵活实现各种接口或者总线的输出,在设备端的通信产品中已得到越来越广泛的使用。FPGA

2019-06-14 06:00:00

求助FPGA和CPLD和单片机接口时能直接接口吗?(5v3.3v会不会烧掉啊)有的同学说行有的说不行很迷茫好像没问题但又不敢进行电平转换又似乎很麻烦 求大神给个解释哈。。。。。。。

2012-07-26 15:32:56

CPLD的电路规模、功能、性能等方面强化之后的产物。(特权同学版权所有)一般而言, FPGA与CPLD之间的区别如表1.1所示。(特权同学版权所有)表1.1 FPGA和CPLD的比较总而言之,FPGA

2015-03-12 13:54:42

推荐给我他的XC9500XL,我需要学习Verilog。在我开始之前,我遇到的一个问题是:我能够使用此CPLD创建收发器吗?我需要能够在两个方向上驱动总线以进行读/写。我也正在读Samir

2019-04-26 11:20:23

有没有人知道在任何XC9500XL系列CPLD上执行的辐射研究?我正在寻找暴露于高能中子的CPLD的时间故障(FIT)数据。以上来自于谷歌翻译以下为原文Does anyone know of a

2019-04-30 15:00:33

XC9500系列CPLD器件是由多个功能块(FB)和IO块(IOB)组成,可用开关矩阵Fast CONNECT完全互连的子系统,IOB提供输入和输出的缓冲,每个FB提供具有36个输入和18个输出

2019-09-30 06:02:08

,可是没有找到,只好自己写咯,若是只用cpld做51系统的地址译码,会用cpld的都能写出代码来,可是cpld与51的总线接口由于涉及到时序就没有那么容易了,我也是郁闷了近3天才把接口电路K掉的,它现在

2012-08-10 18:56:47

AG6310方案设计原理是什么?AG6310技术应用是什么?怎么实现DP转HDMI方案的设计?

2021-05-28 06:15:12

大家好,我正在研究旧卡的长期支持(10年),我想知道完成重新设计的最佳设备。我在工作中的大部分重新设计都是使用CPLD(XC9500)或Spartan 6.我想知道我是否为我的设计选择了CPLD

2020-05-14 08:11:31

可用ERROR:Map:258- 试图获得此架构的许可证时遇到问题。我检查了许可证文件,似乎没问题。我尝试过XC9500 CPLD,但它确实有效。问题是什么?以上来自于谷歌翻译以下为原文I

2018-12-03 15:48:19

立题简介:内容:MCU+CPLD/FPGA实现GPIO扩展与控制;来源:实际得出;作用:MCU+CPLD/FPGA实现GPIO扩展与控制;仿真环境:Quartus II 11.0;日期

2021-11-04 07:42:16

基于SDRAM控制器实现FPGA模块化和通用性的解决方案设计

2020-12-22 07:58:55

本帖最后由 Hi-board 于 2011-11-17 14:30 编辑

Hi-board Xilinx XC95144XL-10TQG100开发板是针对广大Xilinx CPLD/FPGA

2011-11-17 13:12:57

大家在用xilinx 的CPLD芯片有没有发现它的温度明显比单片机等芯片的温度高,我用的XC9500系列发现,有炀手的感觉,但是能正常使用。厂家技术沟通之后说这个是正常的发热。不知大家用其它厂家的CPLD有发现类化的现象。

2012-07-17 22:01:38

器件提供高运算速度,易于与 XC9500/XL/XV 系列 CPLD 联合使用。在单一 CPLD里,消耗极低的功率可实现 XPLA3TM系列多功能性。这一点意味着通过系统内可编程功能使得原来同一

2022-10-28 07:50:06

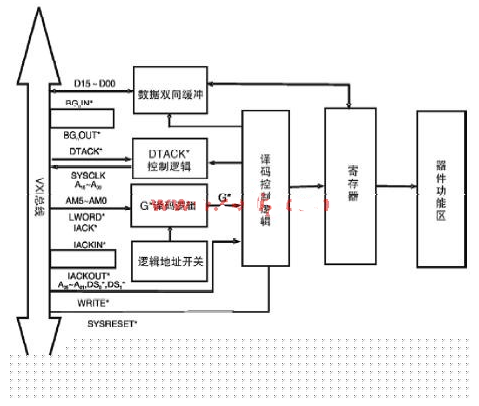

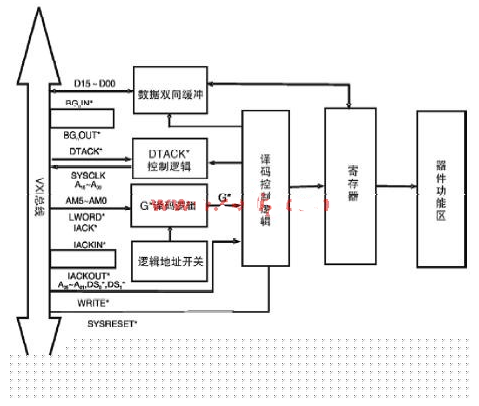

为了扩展VME总线和CAN总线的应用范围,充分利用两种总线的不同传输特点,采用了模块设计方法,提出一种基于FPGA和MCU的总线转换方案。该方案给出了FPGA与上位VME总线部分的VME总线接口

2019-06-28 08:24:19

描述XC9536 是 XC9500 CPLD 系列中最小的 CPLD。它带有 36 个宏单元和 800 个可用门。该器件还提供 44 针 PLCC 封装,可轻松插入插座。在 44 引脚封装内,有

2022-08-05 07:14:37

电平供电的,所以CPLD我们也选择3.3v电平供电的XL型号。XC95144XL是Xilinx公司XC9500系列的一种。它的性能指标为;IO口可配置为3.3v或5v操作。所有输出都提供24mA驱动

2019-05-21 05:00:16

使用方便性和编程的保密性均优于FPGA。 微机保护系统中的数字组合逻辑电路和时序逻辑电路规模均不大,宜采用CPLD芯片实现,有利于微机保护系统的微型化和智能化设计。 微机保护装置控制接口设计 微机保护

2019-04-25 07:00:04

喜我正在使用xc9572xl - CPLD开发板,它有一个用于编程的jtag端口。我该如何编程这个设备?我有vivado 2016。是否需要使用xilinx影响软件对器件进行编程。感谢致敬Gaonkar

2019-10-21 10:24:24

怎么实现基于MRF24J40的IEEE802154无线收发器电路方案设计?

2021-05-25 07:00:15

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

。--- 串行外设用到RS232-C异步串行接口,一般采用专用的集成电路即UART实现。如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO

2012-05-23 19:37:24

XC9500系列CPLD器件是什么?XC9500系列CPLD器件遥控编程的实现方法有哪些?如何实现CPLD遥控编程?

2021-04-27 07:15:42

我已经遍布Xilinx网站,但找不到有关XC9500系列工具的任何信息。对于当前项目,我需要一个小型,低成本的解决方案,这似乎是最好的部分。有人能告诉我哪些工具支持这个家庭的发展?我在Vivado或

2019-04-11 14:07:59

,数字控制信号经过 DA转换后输出模拟控制电压到后端控制电路,实现对七路温度的闭环控制。 4.FPGA与外围电路之间的通信接口 FPGA与外围电路之间的通信接口主要包括与温度传感器,DSP,232接口

2020-08-19 09:29:48

FPGA/CPLD下载方式 (ISP下载线接口电路)

SP功能提高设计和应用的灵活性未编程前先焊接安装系统内编

2009-03-08 10:47:02 129

129 介绍实现单片机与Xilinx公司XC9500系列可编程逻辑器件的读写逻辑功能模块的接口设计,以及Xilinx 公司的XC9500 系列可编程逻辑器件的开发流程。

2009-04-16 09:57:40 23

23 for the XC95108.These files along with others mentioned are obtainablefrom the CPLD Application Notes section of the XilinxWorld Wide

2009-05-13 11:44:56 21

21 高速XC9500XL

2009-05-13 11:53:39 34

34 supplies. XilinxXC9500 CPLDs are designed to operate in either mixed5V/3.3V systems or 5V only systems. To handle both conditio

2009-05-13 13:25:39 18

18 All XC9500 CPLDs have a uniform architecture and anidentical timing model, making them very easy

2009-05-13 13:33:25 13

13 XC9500 devices receive programming vectors and instructionsvia the JTAG Test Access Port. During

2009-05-13 13:50:08 20

20 To get the best performance from any CPLD, the designermust be aware of its internal architecture

2009-05-13 13:53:50 15

15 Charge pumps, the heart of the XC9500/XL ISP circuitryrequire a modest amount of care. The voltages

2009-05-13 14:10:30 29

29 IEEE Boundary-Scan Standard 1149.1, also known asJTAG, is a testing standard that uses software to reducecosts. The primary benefit of the standard is its ability totransform difficult printed circuit board testing problems int

2009-05-13 14:14:47 28

28 All XC9500XL CPLDs have a uniform architecture and anidentical timing model, making them very easy

2009-05-13 14:16:13 21

21 XC9500 devices use a standard 4-wire Test Access Port(TAP) for both In-System Programming (ISP

2009-05-13 14:46:15 6

6 In system field upgrades to an XC9500 CPLD are traditionallydone by field engineers using

2009-05-15 13:39:36 32

32 XC9500 devices receive programming vectors and instructionsvia the JTAG Test Access Port. During

2009-05-15 13:43:11 9

9 To get the best performance from any CPLD, the designermust be aware of its internal architecture

2009-05-15 13:45:07 20

20 Charge pumps, the heart of the XC9500/XL ISP circuitryrequire a modest amount of care. The voltages

2009-05-15 13:48:46 9

9 XC9500 devices use a standard 4-wire Test Access Port(TAP) for both In-System Programming (ISP

2009-05-15 13:54:25 27

27 介绍声波测井中地面系统与声波信号同步的实现方法; 用Xilinx 公司XC9500 系列CPLD 芯片,结合51 系列单片机实现声波测井中的采样门和逻辑信号,给出系统设计方法和程序源代码,

2009-05-15 13:59:26 26

26 介绍实现单片机与Xilinx公司XC9500系列可编程逻辑器件的读写逻辑功能模块的接口设计,以及Xilinx 公司的XC9500 系列可编程逻辑器件的开发流程。

2009-05-15 14:18:11 28

28 高速XC9500XL

2009-05-15 14:32:19 32

32 Using EZTag, the ISP download software from Xilinx, youcan easily program any XC9500 device while

2009-05-15 14:37:09 23

23 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。关键词 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 本文介绍了利用Xilinx公司的XC9500系列CPLD器件,以I2S接口方式对四路输入语音信号进行处理与传输,并用VHDL进行建模,通过ISE软件仿真得出了比较理想的结果,并在工程应用中使用良

2010-08-06 15:54:34 62

62 摘要:介绍实现单片机与Xilinx公司XC9500系列可编程逻辑器件的读写逻辑功能模块的接口设计,以及Xilinx公司的XC9500系列可编程逻辑器件的开发流程。

2009-06-20 13:22:06 1333

1333

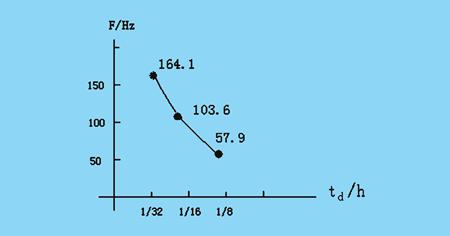

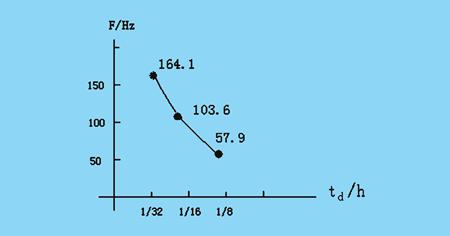

基于CPLD/FPGA的多功能分频器的设计与实现

引言

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求

2009-11-23 10:39:48 1139

1139

常用FPGA/CPLD四种设计技巧

FPGA/CPLD的设计思想与技巧是一个非常大的话题,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口

2010-05-12 11:10:43 766

766

基于FPGA和CPLD数字逻辑实现ADC技术

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现

2010-05-25 09:39:10 1309

1309

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的

2010-11-04 10:11:28 625

625

UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。

2011-12-17 00:15:00 57

57 This application note explains the XC9500/XL/XV Boundary Scan interface anddemonstrates

2012-02-17 15:12:08 61

61 NBP15 Xilinx XC9500XL XC9500XV PQ208 Rev1.01

2016-02-17 14:54:14 0

0 Digilent XC9500 DigiLab XC95,好东西,喜欢的朋友可以下载来学习。

2016-02-22 16:12:37 0

0 Memec XC9500XV Demo Board

2016-02-22 17:26:32 0

0 FPGA/CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。 FPGA/CPLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法

2017-10-09 09:52:20 14

14 是3.3v电平供电的,所以CPLD我们也选择3.3v电平供电的XL型号。XC95144XL是Xilinx公司XC9500系列的一种。它的性能指标为;IO口可配置为3.3v或

2017-10-25 16:17:13 1

1 是3.3v电平供电的,所以CPLD我们也选择3.3v电平供电的XL型号。XC95144XL是Xilinx公司XC9500系列的一种。它的性能指标为;IO口可配置为3.3v或5

2017-10-31 16:28:32 0

0 是3.3v电平供电的,所以CPLD我们也选择3.3v电平供电的XL型号。XC95144XL是Xilinx公司XC9500系列的一种。它的性能指标为;IO口可配置为3.3v或

2017-11-01 15:55:16 2

2 数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2018-04-26 11:53:00 1121

1121

XSVF格式的编程文件包含编程指令和数据,编程指令主要有三条,即XRUNTEST、XSIR和XSDR。微控制器读取指令后进行解释,并根据指令执行相应的操作。

2018-04-04 12:52:00 2649

2649

公司的 MAX系列,Xilinx的XC9500和Spartan系列,Lattice公司的ispLSI系列等。

2018-11-28 08:08:00 2391

2391

介绍了采用CPLD和Flash器件对FPGA 实现快速并行配置,并给出了具体的硬件电路设计和关键模块的内部编程思路。

2018-10-24 15:15:49 7

7 介绍了一种用CPLD(复杂可编程逻辑器件)作为核心控制电路的测试系统接口,通过时cPLD和竹L电路的比较及cPLD在系统中实现的强大功能,论述了CPLD在测试系统接口中应用的可行性和优越性,简单介绍

2019-01-01 16:18:00 1472

1472

对于CPLD/FPGA初学者而言,如何实现双向信号往往是个难题。duoduo 当年初接触CPLD/FPGA的时候也为这个问题头疼过。让我们透过下面这个简单的例子看看CPLD/FPGA设计中如何实现双向信号。

2019-06-11 16:13:51 15

15 FPGA/CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。

2020-01-20 09:29:00 3264

3264 采用;另一种是利用中、小规模电路基PAL、GAL、CPLD和FPGA实现。通过利用FPGA实现模块与VXI总线接口的设计过程中,总结出一些通用的设计思路。

2020-07-27 18:11:22 789

789

基于CPLD/FPGA的半整数分频器设计方案

2021-06-17 09:37:02 21

21 FPGA CPLD数字电路设计经验分享.(电源技术发展怎么样)-FPGA CPLD数字电路设计经验分享

2021-09-18 10:58:03 51

51 FPGA CPLD中的Verilog设计小技巧(肇庆理士电源技术有限)-FPGA CPLD中的Verilog设计小技巧

2021-09-18 16:49:18 35

35 电子发烧友网站提供《XC9572和XC95108 DIY CPLD实验板的PCB.zip》资料免费下载

2022-07-22 11:33:05 6

6 方案介绍XC9536是一款非常轻巧的CPLD,适用于学生和业余爱好者的实验和原型制作。XC9536是XC9500 CPLD系列的最低CPLD。它带有36个具有800个可用门的宏单元。该器件还提供44

2023-01-05 15:49:58 4

4 可编程逻辑包括 PAL、GAL、PLD 等。通过不断发展,它已经发展成为现在的CPLD/FPGA。CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)的功能基本相同,只是实现原理略有不同

2023-07-03 14:33:38 6041

6041

电子发烧友网站提供《基于CPLD/FPGA的多串口扩展设计方案.pdf》资料免费下载

2023-10-27 09:45:17 2

2

电子发烧友App

电子发烧友App

评论