电源时序控制是微控制器、FPGA、DSP、ADC和其他需要多个电压轨供电的器件所必需的一项功能。##使用电阻分压器简化电源时序控制

2014-08-14 10:57:25 2415

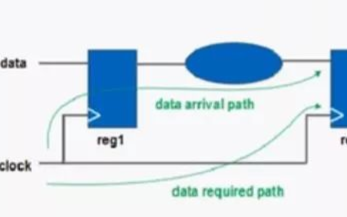

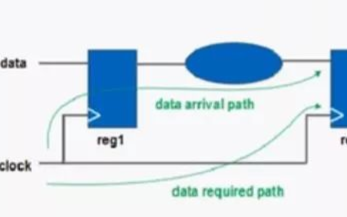

2415 表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 2768

2768

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 860

860

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

在输入信号到输出信号中,因为经过的传输路径、寄存器、门电路等器件的时间,这个时间就是时序。开发工具不知道我们路径上的要求,我们通过时序约束来告诉开发工具,根据要求,重新规划,从而实现我们的时序要求,达到时序的收敛。

2019-07-31 14:50:41 6185

6185

引言 现场可编程逻辑门阵列FPGA器件的出现是超大规模集成电路技术和计算机辅助设计技术发展的结果。FPGA器件集成度高、体积小,具有通过用户编程实现专门应用功能。它允许电路设计者利用基于计算机的开发

2018-12-18 09:51:38

从可编程器件发展看FPGA未来趋势 15第三章、FPGA主要供应商与产品 173.1.1 赛灵思主要产品介绍 17第四章、FPGA开发基本流程 294.1 典型FPGA开发流程与注意事项 294.2

2009-04-09 18:28:46

布线、时序验证,这一阶段是详细设计阶段;第三个阶段是FPGA器件实现,除了器件烧录和板级调试外,其实这个阶段也应该包括第二个阶段的布局布线和时序验证,因为这两个步骤都是和FPGA器件紧密相关的。我们

2019-01-28 04:24:37

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

经过两天的恶补,特别是学习了《第五章_FPGA时 序收敛》及其相关的视频后,我基本上明白了时序分析的概念和用法。之后的几天,我会根据一些官方的文件对时序分析进行更系统、深入的学习。先总结一下之前

2011-09-23 10:26:01

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可

2016-06-02 15:54:04

(InputDelay、OutputDelay)、上下拉电阻、驱动电流强度等。加入I/O约束后的时序约束,才是完整的时序约束。FPGA作为PCB上的一个器件,是整个PCB系统时序收敛的一部分。FPGA作为

2017-12-27 09:15:17

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

/1bndF0bt 在第一章中,已经给出了FPGA/CPLD的基本开发流程图。这里不妨回顾一下,如图5.15所示。这个流程图是一个相对比较高等级的FPGA/CPLD器件开发流程,从项目的提上议程开始,设计者需要

2015-02-09 20:14:21

在第一章中,已经给出了FPGA/CPLD的基本开发流程图。这里不妨回顾一下,如图5.15所示。这个流程图是一个相对比较高等级的FPGA/CPLD器件开发流程,从项目的提上议程开始,设计者需要进行

2015-03-03 14:31:44

使能这两个配置也能在一定程度上改善时序收敛。 FPGA工程师的工作不只是将电路功能实现,由于器件和工具不是理想的,所以还需要研究器件特性和工具的局限,尤其是在如今算法结构越来越成熟的背景下,不断被工具折磨,也许这也是FPGA工程师的悲哀吧。

2020-12-23 17:42:10

FPGA入门:基本开发流程概述 在第一章中,已经给出了FPGA/CPLD的基本开发流程图。这里不妨回顾一下,如图5.15所示。这个流程图是一个相对比较高等级的FPGA/CPLD器件开发流程,从项目

2019-01-28 02:29:05

FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。FPGA的开发流程一般包括功能定义、设计输入、功能仿真、综合优化、综合后仿真、实现与布局布线、时序仿真与验证、板级仿真

2023-12-31 21:15:31

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

、时序验证,这一阶段是详细设计阶段;第三个阶段是FPGA器件实现,除了器件烧录和板级调试外,其实这个阶段也应该包括第二个阶段的布局布线和时序验证,因为这两个步骤都是和FPGA器件紧密相关的。我们这么粗略

2015-03-31 09:27:38

模块,熟练verilog语言,熟练使用Altera FPGA的开发环境,熟练使用仿真、综合、时序分析工具,有1年以上工作经验者优先。简历接收邮箱:awejob@chnawe.com 。欢迎各位小伙伴们

2016-09-27 16:45:15

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

FPGA 设计优化主要分为编码风格、设计规划和时序收敛三大部分,这 些因素直接决定了 FPGA 设计的成败。 编码风格直接影响 FPGA 设计的实现并最终影响设计的性能。尽管综合 工具集成

2022-09-29 06:12:02

的相位偏移将有效地改变存储控制器接收寄存器的最小有效数据窗口,因此将形成平衡有效数据窗口。时钟偏移调整是FPGA装置中PLL器件的一个组成部分。要确定偏移的值,我们必须考虑到影响信号的布线延迟和任何外部

2017-09-01 10:28:10

和-LS的电气和时序特性。(特权同学,版权所有)图3.8 Cyclone III器件手册大纲限于篇幅,我们可以重点看看Volume 1的第一章,即概述部分的内容。希望借此大家能够对我们所选用的FPGA器件

2019-04-15 02:21:50

随着FPGA器件体积和复杂性的不断增加,设计工程师越来越需要有效的验证方。时序仿真可以是一种能发现最多问题的验证方法,但对许多设计来说,它常常是最困难和费时的方法之一。过去,采用标准台式计算机的时序

2019-07-16 08:10:25

实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。1.2FPGA整体概念 由于IO口时序约束分析是针对于电路板

2012-04-25 15:42:03

。Vivado工具支持专用的编辑器实现时序约束、I/O引脚约束和布局布线约束。设计仿真 在整个开发过程的任意时刻,设计者都可以使用仿真工具对FPGA工程进行功能验证,比如Vivado内置的仿真器或者第三方工具

2019-04-01 17:50:52

专用的全局时钟输入引脚驱动单个主时钟去控制设计项目中的每一个触发器。同步设计时, 全局时钟输入一般都接在器件的时钟端,否则会使其性能受到影响。 对于需要多时钟的时序电路, 最好选用一个频率是它们

2012-03-05 14:29:00

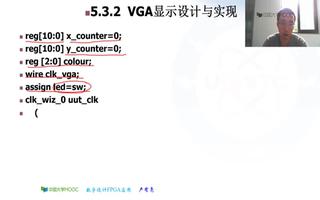

资源不足跑不起来,所以暂未实现,后续考虑实现一个俄罗斯方块或者贪吃蛇)。图5 FPGA端程序结构图PSRAM读写采用云源软件内的PSRAM控制器IP,并按照数据手册进行读写时序仿真和设计,在接收到特定

2021-05-11 09:16:10

本视频是MiniStar FPGA开发板的配套视频课程,主要通过工程实例介绍Gowin的物理约束和时序约束,课程内容包括gowin的管脚约束及其他物理约束和时序优化,以及常用的几种时序约束。 本

2021-05-06 15:40:44

Verilog;2.精通Altera/Xilinx/Lattice公司的FPGA以及开发环境,精通硬件时序分析基础知识;3.2年以上FPGA设计经验,能够熟练使用modelsim等仿真工具并编写激励文件

2017-07-19 14:21:56

,以及Windows CE、Windows Mobile和Linux环境的软件驱动程序。图2中所示的板卡配有硬盘驱动器、两个SD卡插槽、卡总线接口及用来连接FPGA器件I/O引脚的接头

2012-04-27 14:40:21

CVSD编译码时则需要很多专用芯片,具有局限性;而单片FPGA容易实现多路CVSD编译码功能。此外如果专用芯片停产或者买不到,已有的通信设备维修将会因器件缺乏导致后续工作无法开展。为了弥补专用CVSD芯片

2019-08-07 07:04:27

的划分;第二个阶段是设计实现阶段,这个阶段包括编写RTL代码、并对其进行初步的功能验证、逻辑综合和布局布线、时序验证,这一阶段是详细设计阶段;第三个阶段是FPGA器件实现,除了器件烧录和板级调试外

2016-07-13 17:25:34

求的定义和分析、各个设计模块的划分;第二个阶段是设计实现阶段,这个阶段包括编写RTL代码、并对其进行初步的功能验证、逻辑综合和布局布线、时序验证,这一阶段是详细设计阶段;第三个阶段是FPGA器件实现,除了

2017-10-12 21:02:44

1、在FPGA中实现串口协议的设计在FPGA中实现串口协议,通过Anlogic_FPGA开发板上的“UART2USB”口接收从计算机发来的数据。实验设计思路UART串口是一种类似于USB、VGA

2022-07-19 11:09:48

涉及时序逻辑电路的实例,希望能够帮助大家理解在FPGA中实现时序逻辑电路。与组合逻辑电路相比,时序逻辑电路需要时钟的参与,电路中会有存储器件的参与,时序逻辑电路的输出不仅取决于这一时刻的输入,也受此

2022-07-22 15:25:03

?以保证FPGA发送过去的数据能被外部芯片正确接收的。

FPGA通过某种通用接口(如SPI)和外部芯片通信时,FPGA如何实现才能满足芯片手册给出的时序要求呢?

2023-04-23 11:35:02

摘要:RS 232接口是现在最常用的一种通信接口。随着FPGA技术的高速发展,一些常见的接口电路的时序电路可以通过FPGA实现,通过这种设计可减少电路系统元件的数量,提高系统集成度和可靠性。详细阐述

2019-06-19 07:42:37

的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种

2019-07-29 07:03:50

时序分析是FPGA设计的必备技能之一,特别是对于高速逻辑设计更需要时序分析,经过基础的FPGA是基于时序的逻辑器件,每一个时钟周期对于FPGA内部的寄存器都有特殊的意义,不同的时钟周期执行不同的操作

2017-02-26 09:42:48

大家好,我想知道如何实现硬件(FPGA)中的时序报告给出的时序。我的意思是,如何测量FPGA和FPGA中输入信号的建立或保持时间与静态时间报告给出的值进行比较。FPGA怪胎以上来自于谷歌翻译以下

2019-01-15 11:07:15

如何搭建Qt for MCUs PC端开发环境?

2022-02-10 07:48:18

免各种温度变化和其他类似的设计影响,可能在时钟或数据方面会遇到一些影响,但不会很大,因此违背了接收存储器的建立或保持时序的要求。在理论上,对于大部分器件,中心对齐的时钟边缘将最大限度地建立和保持时序

2009-04-14 17:03:52

12.288 MHz 的外部时钟信号,以实现 48 KHz 的采样率。我如何计算从 CODEC 到 STM32F446 的每个样本的接收时间?

2022-12-19 07:59:50

SpaceWire Codec接收端是什么?怎样去设计SpaeeWire Codec接收端的时序?时钟域可划分为哪几个模块?如何实现多时钟域信号的同步?

2021-04-08 07:10:15

1. FPGA时序的基本概念FPGA器件的需求取决于系统和上下游(upstream and downstrem)设备。我们的设计需要和其他的devices进行数据的交互,其他的devices可能是

2019-07-09 09:14:48

对器件进行配置。这样有助于降低电源时序控制要求,但为了实现最小浪涌电流电平并遵循连接至 FPGA 的电路时序控制要求,供电轨应当按以下序列上电:VCC_INT a VCC_AUX a VCCO。请注意

2018-10-23 14:30:34

1.XILINX ISE传统FPGA设计流程利用XilinxISE软件开发FPGA的基本流程包括代码输入、功能仿真、综合、综合后仿真、实现、布线后仿真与验证和下班调试等步骤。如下图所示。1)电路设计

2021-06-24 08:00:01

USB数据与并行I/O口数据的交换缓冲区。FIFO实现与外界(微控制器、FPGA或其它器件)的接口,主要通过8根数据线D0~D7、读写控制线RD#和WR#以及FIFO发送缓冲区空标志TXE#和FIFO接收

2019-04-22 07:00:07

USB数据与并行I/O口数据的交换缓冲区。FIFO实现与外界(微控制器、FPGA或其它器件)的接口,主要通过8根数据线D0~D7、读写控制线RD#和WR#以及FIFO发送缓冲区空标志TXE#和FIFO接收

2019-04-26 07:00:12

本实验是基于EasyFPGA030 的串口接收设计。FPGA 除了需要控制外围器件完成特定的功能外,在很多的应用中还需要完成FPGA 和FPGA 之间、FPGA 和外围器件之间以及FPGA 和微机的数据交换和

2010-03-11 15:39:55 30

30 本文详细分析了ADSL系统中ATM层和物理层之间的UTOPIA LEVEL2接口时序,采用FPGA实现了UTOPIA接口设计,应用在ADSL系统中,数据收发正确,工作稳定;该方案的实现对解决现有专门通信芯

2010-07-28 16:54:10 19

19 系统(HPS)来评估SoC的特性及性能。Intel Agilex® F系列FPGA开发套件提供了一个完整的设计环境,其中包括采用PCI Express(PCIe)

2024-02-27 11:51:58

如何有效的管理FPGA设计中的时序问题

当FPGA设计面临到高级接口的设计问题时,EMA的TimingDesigner可以简化这些设计问题,并提供对几乎所有接口的预先精确控制。从简单

2009-04-15 14:19:31 659

659

CODEC,CODEC是什么意思

CODEC是“COder/DECoder”的缩写,CODEC芯片负责数字与模拟信号的转换。它可将电脑里的数字信号转变成模拟声音信

2010-03-23 09:38:43 5506

5506 Codec/THX,Codec/THX是什么意思

Codec

由英文编码器(coder)和译码器(decoder)两词的词头组成的缩略语。指

2010-04-12 10:36:01 1180

1180 基于多相滤波的信道化接收机抽取在滤波之前,运算量小,且输出速率低,便于FPGA实现,这使得在 一片FPGA中实现数字信道化成为可能。本文利用信道频率重叠的方法连续覆盖整个瞬时

2012-05-23 10:43:04 3538

3538 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1169

1169 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 赛灵思FPGA设计时序约束指南,下来看看

2016-05-11 11:30:19 48

48 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA设计中的时序问题

2017-01-14 12:49:02 14

14 SuperVessel将包括赛灵思SDAccel开发环境,支持用C、C++和OpenCL实现FPGA加速 All Programmable 技术和器件的全球领先企业赛灵思公司与IBM公司今天联合宣布

2017-02-08 16:06:08 228

228 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2017-02-09 01:59:11 264

264 FPGA 设计的时序性能是由物理器件、用户代码设计以及EDA 软件共同决定的,忽略了任何一方面的因素,都会对时序性能有很大的影响。本节主要给出大规模设计中,赛灵思物理器件和EDA 软件的最优使用方案。

2017-02-11 16:34:11 847

847

fpga时序收敛

2017-03-01 13:13:34 23

23 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

针对八通道采样器AD9252的高速串行数据接口的特点,提出了一种基于FPGA时序约束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行数据,利用FPGA内部的时钟管理模块DCM、位置约束

2017-11-17 12:27:01 6488

6488

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 2951

2951 作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4903

4903

FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43:00 4150

4150

数据采集系统的总体架构如图1所示,其中PCI核、DMA控制器与A/D控制器均在FPGA内部实现。为实现多路并行采样,可选用多片A/D器件并行处理的方式,在FPGA的高速状态机控制下,完成模拟信号经过

2018-08-28 10:16:07 12734

12734

赛灵思公司(Xilinx)推出针对 OpenCL、C 和 C++的S DAccel 开发环境,将单位功耗性能提高达25倍,从而利用 FPGA 实现数据中心应用加速。SDAccel 是赛灵思 SDx

2018-08-30 17:00:00 1023

1023 中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-08-07 06:00:00 2342

2342

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 2539

2539

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

11 、 Synopsys公司的VCS/SS及 FPGA/CPLD厂商的集成开发环境中自带的仿真工具,如 Altera Quartus中集成的仿真软件等

2021-01-20 16:27:59 8

8 针对电子战中的宽带侦察数字信道化接收机,提出了基于短时傅里叶变换的宽带数字信道化接收机的改进方法,给出了该方法的FPGA实现。该方法采用多相滤波结构,通过先对时域抽取信号进行傅里叶变换,再对变换结果

2021-02-05 17:35:51 27

27 基于FPGA的GPS接收机实现说明。

2021-04-09 14:01:04 51

51 一、前言 无论是FPGA应用开发还是数字IC设计,时序约束和静态时序分析(STA)都是十分重要的设计环节。在FPGA设计中,可以在综合后和实现后进行STA来查看设计是否能满足时序上的要求。

2021-08-10 09:33:10 4768

4768

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 2379

2379

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 768

768 FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-23 17:44:00 531

531

STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 344

344

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-26 15:29:05 531

531

FPGA高级时序综合教程

2023-08-07 16:07:55 3

3

电子发烧友App

电子发烧友App

评论