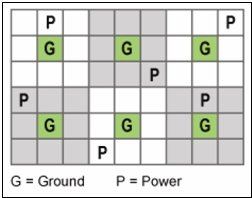

用户端使用的,框图如图1所示。 如图1 所示的中间部分为我们调取的IP 核,user FPGA Logic 为用户端逻辑,DDR2/DDR3 SDRAM 为存储芯片。其中IP 核与存储芯片之间的总线大部分

2020-12-31 11:17:02 5068

5068

2、512Mb-2Gb LP DDR2,以及 LP DDR4x、LP DDR3、LP DDR、SDRAM,适用于需配备4Gb 或以下容量DRAM 的应用, 如人工智能加速器、物联网、汽车、工业用、电信、

2022-04-20 16:04:03 2554

2554

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2871

2871

DDR31.DDR3概述DDR3内存控制器主要用于以JESD79-3C标准做SDRAM设备的外部存储接口。支持的内存类型有DDR1 SDRAM,SDRSDRAM, SBSRAM。DDR3内存控制器

2018-01-18 22:04:33

嗨,我是FPGA领域的新手。现在我正在使用Genesys2。我必须控制DDR3内存。我在Digilent网站上找到了一些使用micrlaze处理器的DDR3示例。但是,在我的情况下,我不必

2019-05-05 15:29:38

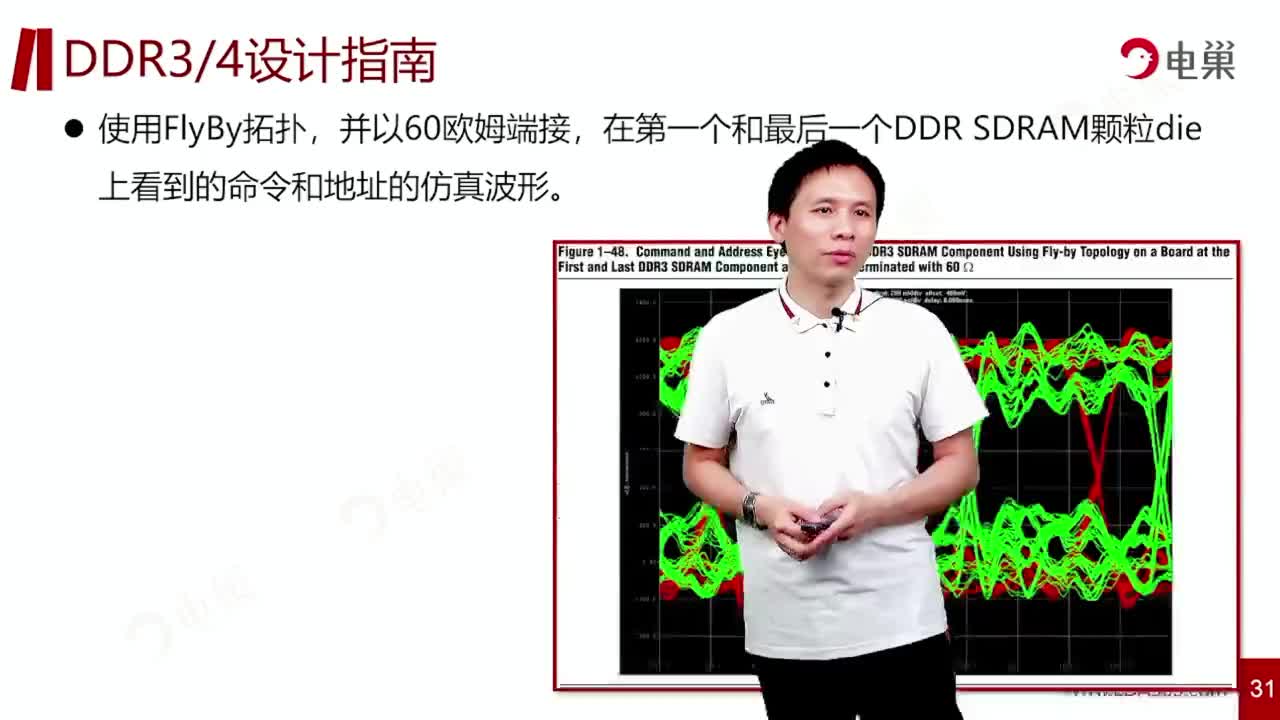

为了实现更强大的系统操作,DDR3 SDRAM驱动器设计通过降低电容得到了增强,动态片上端接(ODT)和新的校准方案。电容减少来自于使用新的合并驱动器。使用新驱动程序,组成输出驱动程序的电路共享用于ODT。DDR2上使用单独的结构作为输出驱动器和终端阻抗。

2019-05-23 08:20:56

转载DDR3内存详解,存储器结构+时序+初始化过程2017-06-17 16:10:33a_chinese_man阅读数 23423更多分类专栏:硬件开发基础转自:首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其...

2021-07-27 07:10:34

成800MHz的时候DDR出现错误,我在程序和表格中都对频率做了修改。

对于DDR3的初始化和配置还是了解的不够,还望有人能够指教一下。

2018-06-21 12:48:07

HI,我的FPGA是Kintex-7的XC7K410T-2FFG900。我的DDR3是2Gb,由128Mb * 16组成。 DDR3数据速率为1600Mbps,因此我必须在HP BANK中使用VRN

2020-07-21 14:47:06

为任意或所有DDR3 SDRAM器件提供单独的终端阻抗控制,提高了存储器通道的信号完整性。图2:DDR3存储器控制器IP核框图DDR3存储器控制器应支持广泛的存储器速率和配置,以满足各种应用需求。例如

2019-05-24 05:00:34

CPU的DDR3总线只连了一片DDR3,也没有复用总线将DDR3的CS直接拉到地的话,DDR3初始化不成功所以说DDR3的CS信号是通过沿采样的吗,电平采样不行?无法理解啊还是有其他方面原因

2016-11-25 09:41:36

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之处?

2021-03-12 06:22:08

在使用DDR3 SDRAM Controller with Uniphy ip(quartus prime 17.1 )核时卡在如下情况,无法生成(持续一晚上), 且软件没有报错误及其它提示。再换用

2018-05-14 19:29:26

你好,ISE版本为13.3,modelsim版本为10.1c 64bit.MIG工具为ddr3生成mcb。modelsim的transcript窗口中的消息如下

2019-07-08 08:44:42

因为工作的需要,最近做了下DDR3 IP核的读写仿真,仿真过程中DDR写数据正常,但在对DDR读取数据时出现以下的情况:1.MEM_DQ、MEM_DQS、MEM_DQSN始终为高阻态

2019-12-26 23:11:56

DDR3 SDRAM内存的总线速率达到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作电压,采用90nm制程达到2Gbits的高密度。这个架构毫无疑问

2019-04-22 07:00:08

FPGA选用alter公司的cyclone V系列,DDR3外接2片,程序调用DDR3 ip核UniPHY,程序综合编译没有问题,只配置了几个引脚定义,就出现了如下错误:Error (14566

2018-04-16 16:35:13

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面写FPGA的BANK1,3连接外部存储控制器(如下图,且只有四个BANK),所以要将DDR3连接在BANK3上。所以DDR3如何与FPGA芯片

2021-11-29 16:10:48

如果没有将均衡功能直接设计到FPGA I/O架构中,那么任何设备连接到DDR3 SDRAM DIMM都将是复杂的,而且成本还高,需要大量的外部元器件,包括延时线和相关的控制。

2019-08-21 07:21:29

Gowin DDR3 Memory Interface IP 用户指南主要内容包括 IP 的结构与功能描述、端口说明、时序说明、配置调用、参考设计等,旨在帮助用户快速了解 Gowin DDR3 Memory Interface IP 的产品特性、特点及使用方法。

2022-10-08 08:10:13

本次发布 Gowin DDR3参考设计。Gowin DDR3 参考设计可在高云官网下载,参考设计可用于仿真,实例化加插用户设计后的总综合,总布局布线。

2022-10-08 08:00:34

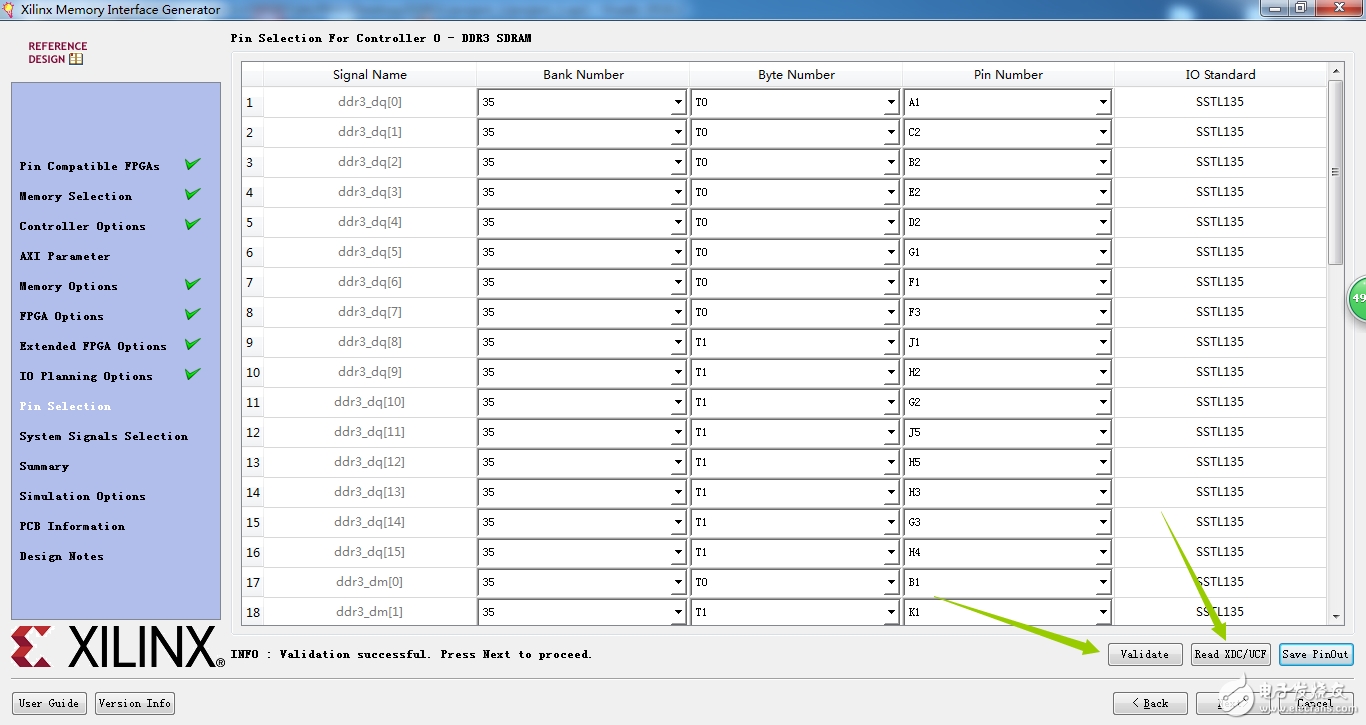

求助大神!!!FPGA对于DDR3读写,FPGA是virtex6系列配置MIG IP 核时,需要管脚分配1.原理图上dm是直接接地,管脚分配那里该怎么办2.系统时钟之类的管脚分配,是需要在原理图上找FPGA与DDR3之间的连线吗?还是?

2018-03-16 18:45:10

我DDR3 IP核设置了两套avalon端口,端口0只写 端口1只读;我得工作流程是:端口0写完整一帧数据到DDR3,大约15ms,然端口1开始读这一帧数据大约需要25ms;但是我的帧周期是35ms

2019-06-19 10:41:29

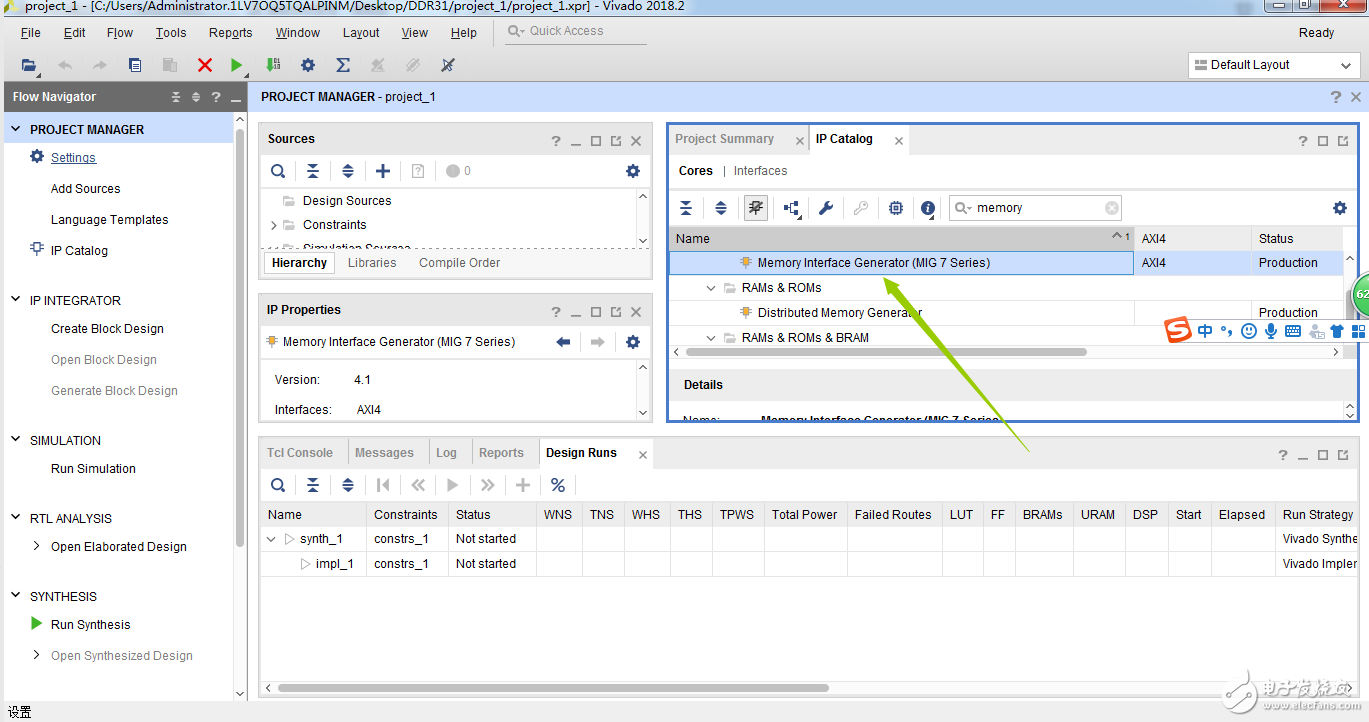

XILINX MIG(DDR3) IP的AXI接口与APP接口的区别以及优缺点对比

2021-11-24 21:47:04

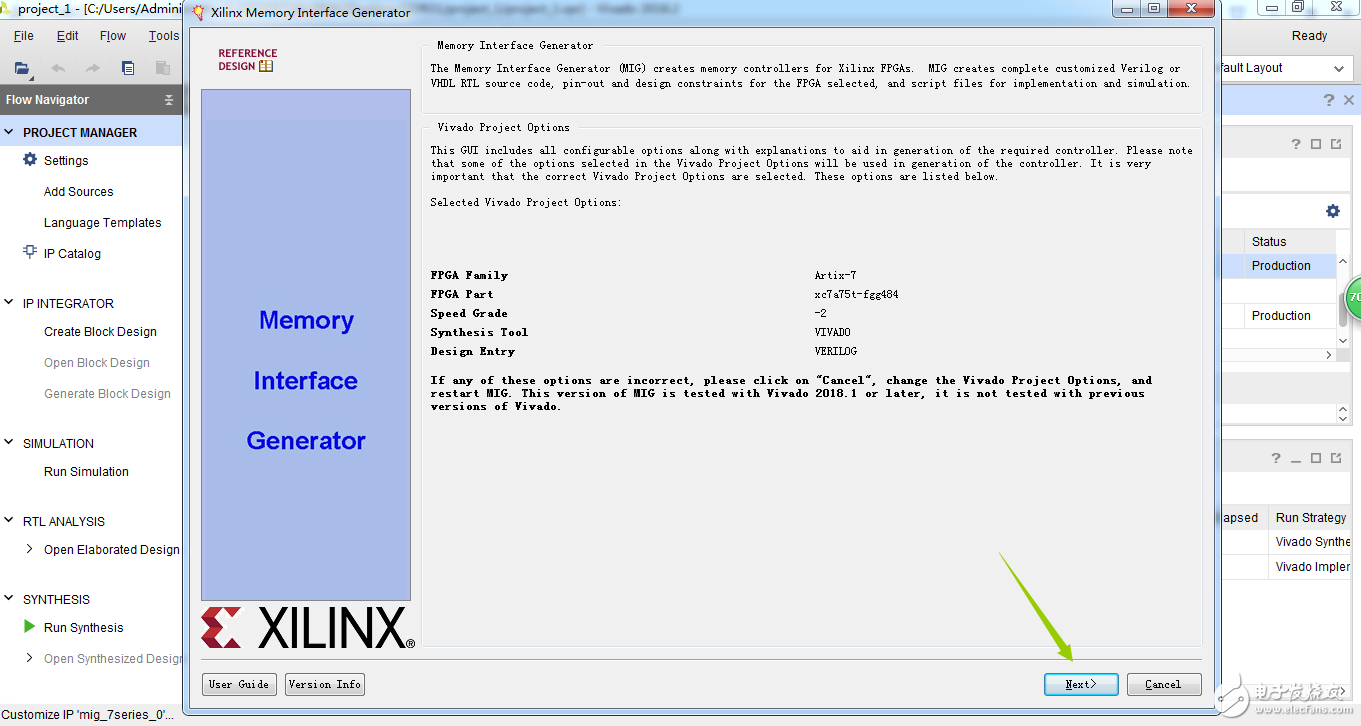

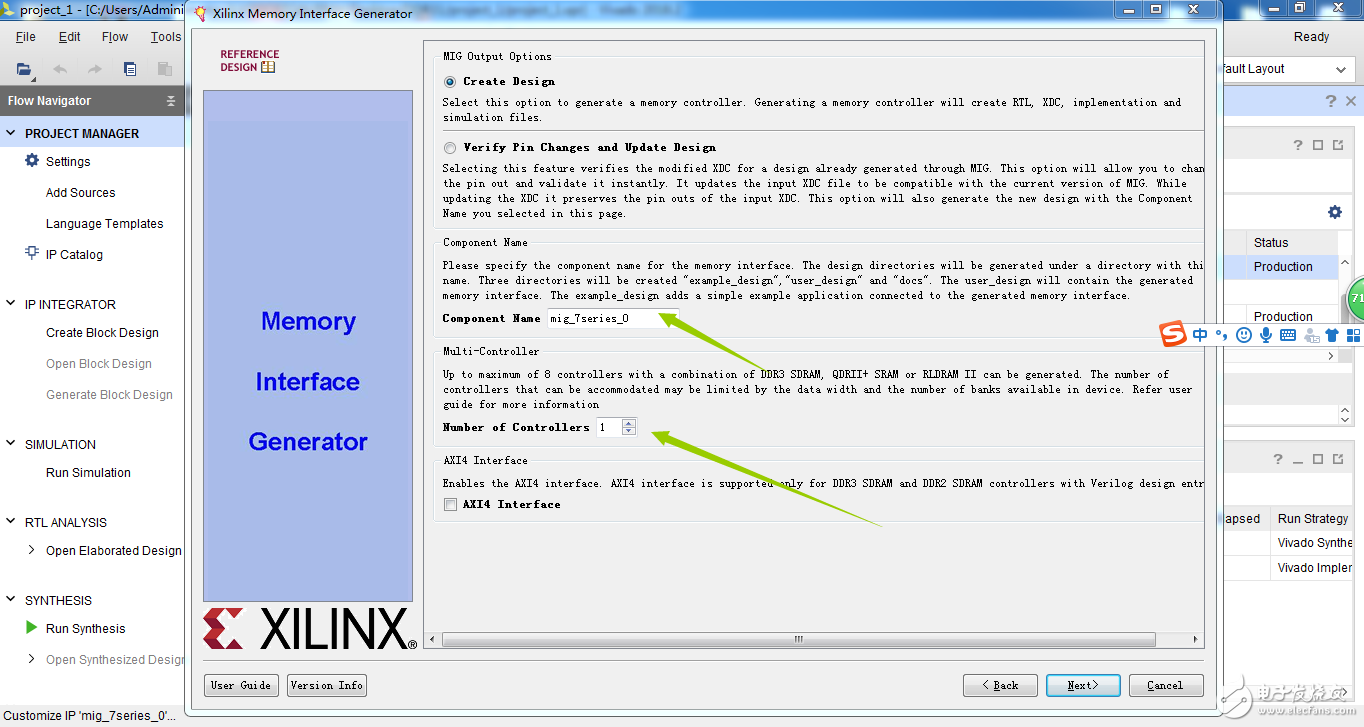

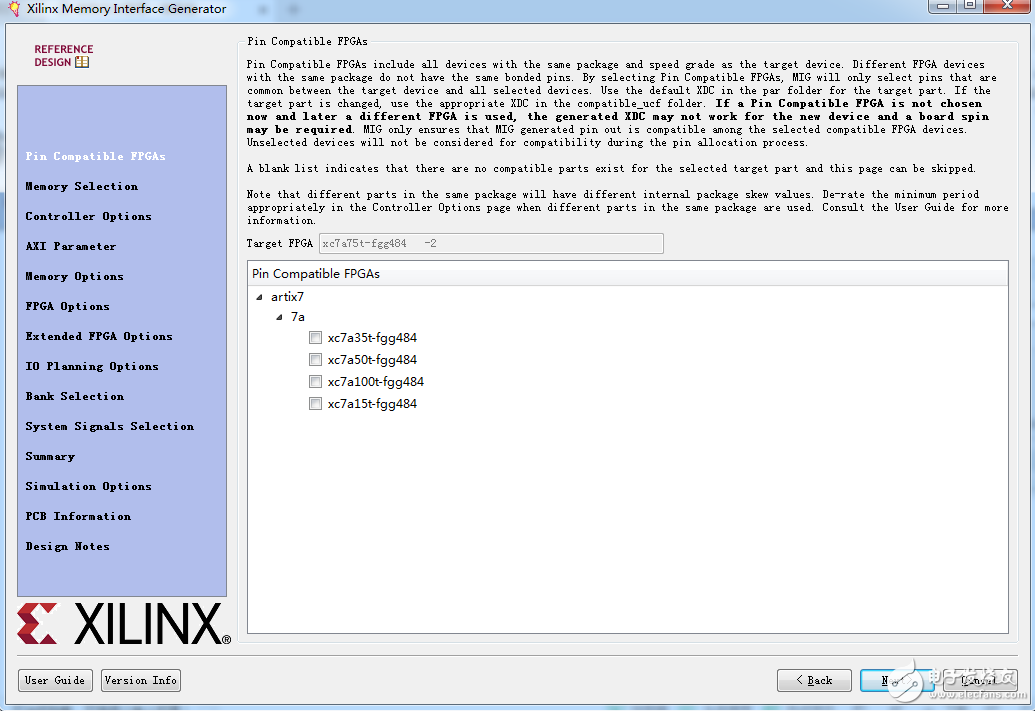

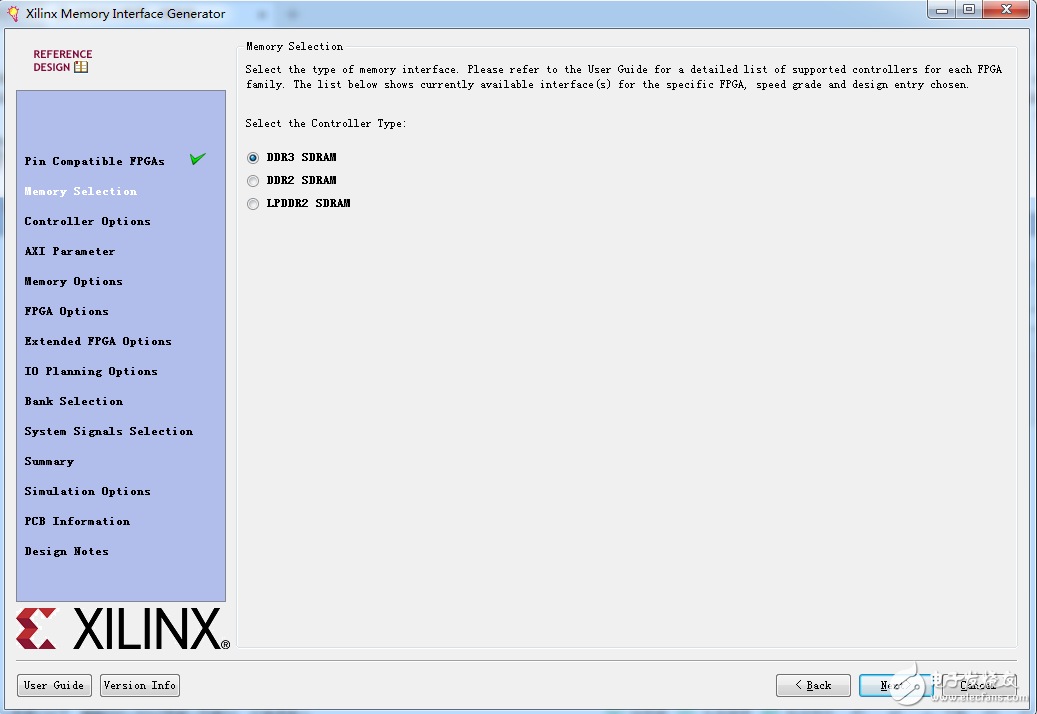

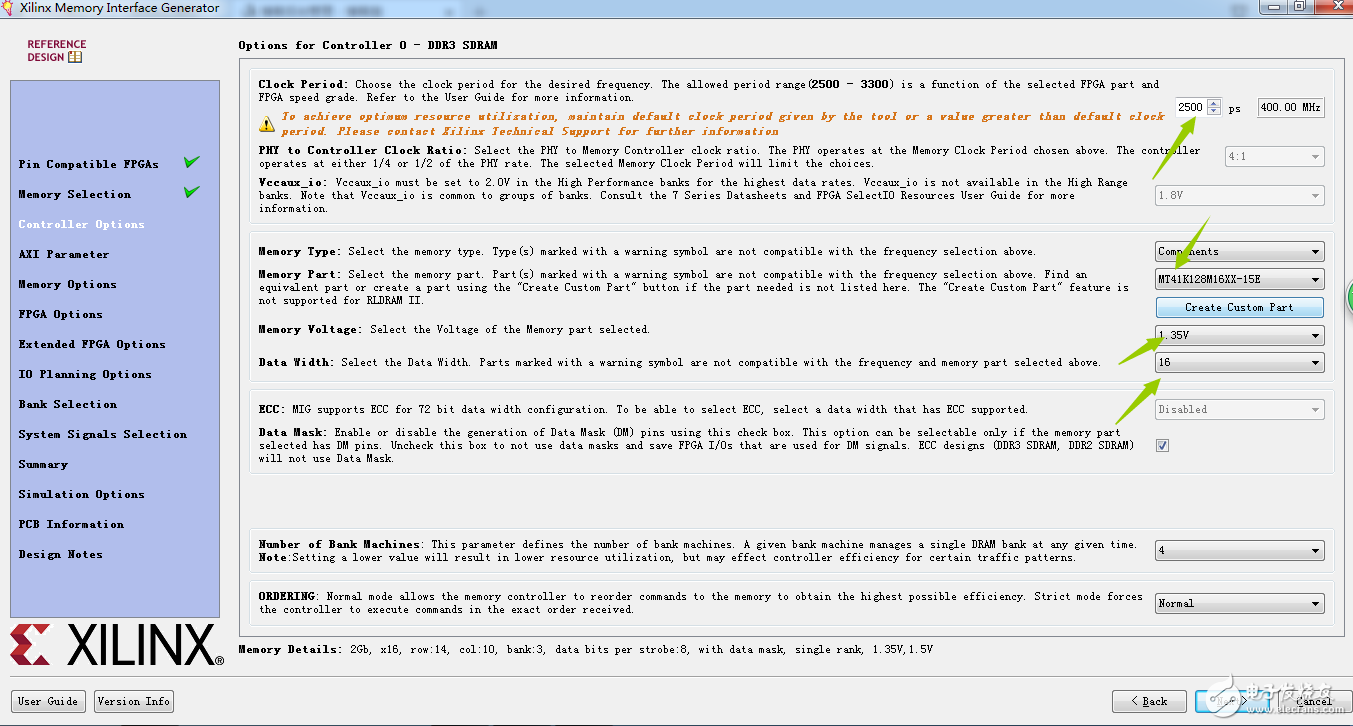

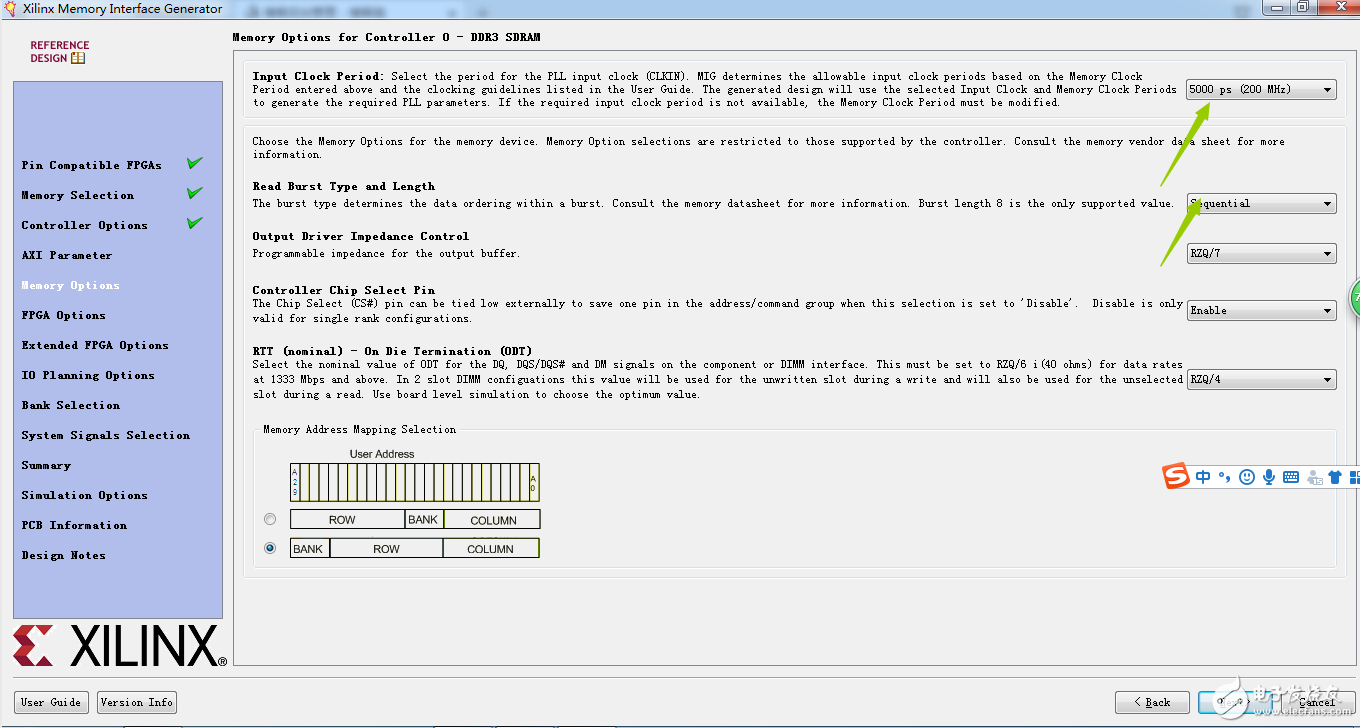

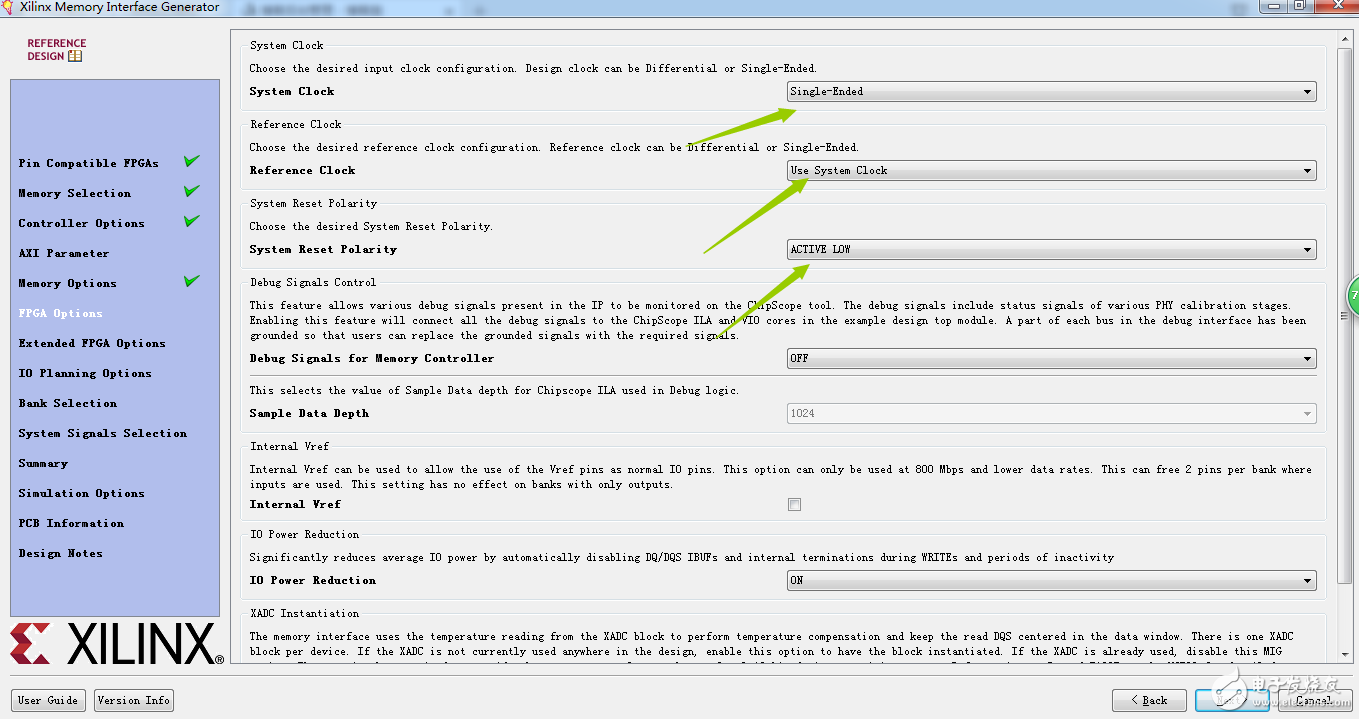

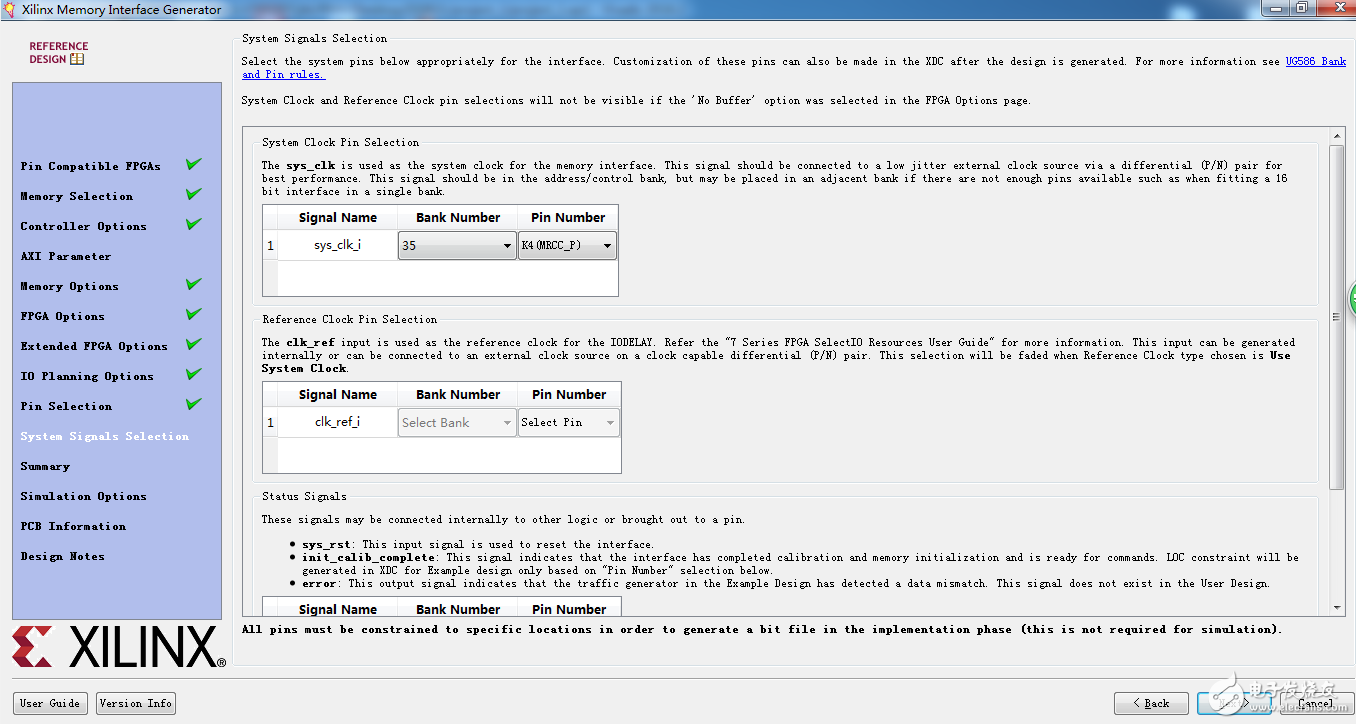

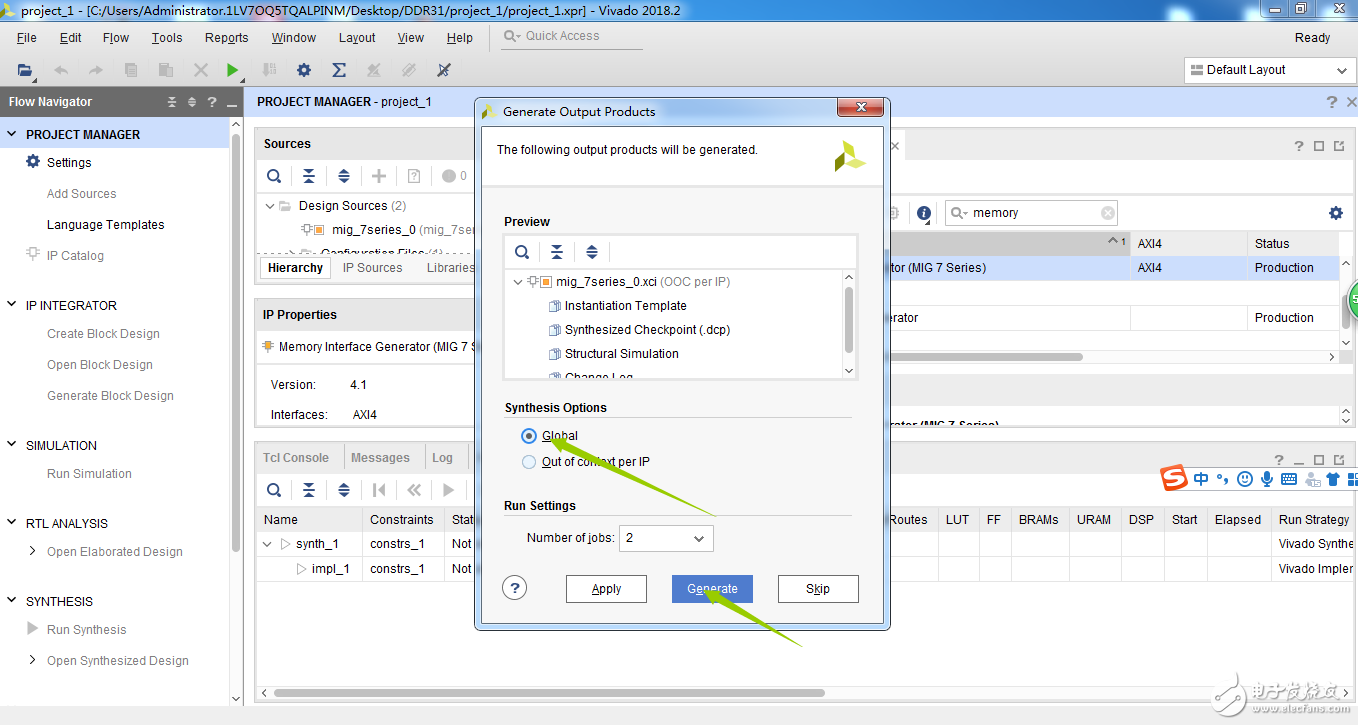

”。13.点击“Generate”生成MIG控制器。四、生成文档点击“Generate”,生成MIG控制器相关的设计文档。以上就是基于Xilinx 的K7 DDR3 IP核的生成配置过程。

2019-12-19 14:36:01

大家好,应用altera Cyclone V外接DDR3,启用HMC实现硬核控制,IP核在设计生成时出现如下错误:Error: Error during execution of script

2018-04-25 10:28:52

RASn,CASn等,是IP核自动产生的么?要如何配置条件,给DDR3写入数据并读取DDR3的数据,谢谢,现在头绪不清,第一次做,拜托各位解惑了

2016-01-14 18:15:19

请教各位大神,小弟刚学FPGA,现在在用spartan-3E的板子,想用上面的DDR SDRAM进行简单的读写,用MIG生成DDR核之后出现了很多引脚,看了一些资料也不是很清楚,不知道怎么使用生成的这个IP核控制器来进行读写,希望大神们稍作指点

2013-06-20 20:43:56

本视频是Combat FPGA开发板的配套视频课程,本章节课程主要介绍Gowin中DDR3 的基础知识、DDR3的IP core的特性和使用以及DDR3的IPcore例程的仿真。课程资料包含DDR3

2021-05-06 15:34:33

`本开发板板载了一片高速 DDR3 SDRAM, 型号:MT41J128M16JT-093, 容量:256MByte(128M*16bit),16bit 总线。开发板上 FPGA 和 DDR3

2021-07-30 11:23:45

后点击“OK”:四、配置IP核在配置界面,“Memory Protocol”选择“DDR3”;在“General”页面“Clocks”“Memory clock frequency”配置DDR的速率为

2019-12-19 10:16:43

的。DDR3控制器调用Write leveling功能时,需要DDR3 SDRAM颗粒的反馈来调整DQS与CK之间的相位关系,具体方式如下图一所示。Write leveling 是一个完全自动的过程。控制器

2022-12-16 17:01:46

、DDR2与DDR3内存的特性区别: 1、逻辑Bank数量 DDR2 SDRAM中有4Bank和8Bank的设计,目的就是为了应对未来大容量芯片的需求。而DDR3很可能将从2Gb容量起步,因此起始

2011-12-13 11:29:47

你好我正在使用新版ML605板当我测试DDR3时,它失败了我在xilinx论坛上找到“ML605 - SO DIMM附带更新的版本”并更改MHS文件和UCF文件,但是当我尝试运行它时,会出现两个错误

2019-09-17 11:15:30

大家好!

我刚刚买了TMDSEVM6678L开发套件,这款套件应该有512MB的DDR3 SDRAM,从图上看,有5块芯片组成这512MB的DDR3,但是我的板子上DDR3部分只有4块芯片,请教一下各位是我的板子少了一块芯片还是这4块芯片容量比5块的要大,所以总量还是512MB呢?

谢谢!

2018-06-24 05:29:03

为任意或所有DDR3 SDRAM器件提供单独的终端阻抗控制,提高了存储器通道的信号完整性。图2:DDR3存储器控制器IP核框图DDR3存储器控制器应支持广泛的存储器速率和配置,以满足各种应用需求。例如

2019-05-27 05:00:02

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

优仲裁模块、读写逻辑控制模块和DDR3存储器控制模块。DDR3存储控制器模块采用Xilinx公司的MIG核,用户只需要通过IP核的GUI选择内存芯片并进行相关参数设置,即可完成DDR3的配置工作[6

2018-08-02 09:32:45

2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电[2][3],能够满足吞吐量大、功耗低的需求,因此选择DDR3 SDRAM作为机载视频图形显示系统的外部存储器。本文以Xilinx公司

2018-08-02 11:23:24

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了

2018-08-30 09:59:01

的 DDR3 SDRAM 器件,型号为 MT41J128M16JT-125:K,两者连接方式为点到点连接。连接示意图如下:

2022-09-29 06:15:25

选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足

2019-06-24 06:07:53

基于Xilinx MIS IP的DDR3读写User Interface解析特权同学,版权所有,转载请注明出处参考文档:ug586_7Series_MIS.pdf1. Command时序首先,关于

2016-10-13 15:18:27

当我们通过IP目录在Vivado中创建一些IP内核时,将使用xdc文件生成一些内核。在这个xdc文件中,它包括时序或物理约束。以DDR3控制器为例,用核心生成xdc文件。它包括时序约束和物理约束

2019-03-26 12:29:31

均衡的定义和重要性是什么如何实现FPGA和DDR3 SDRAM DIMM条的接口设计?

2021-05-07 06:21:53

现在因为项目需要,要用DDR3来实现一个4入4出的vedio frame buffer。因为片子使用的是lattice的,参考设计什么的非常少。需要自己调用DDR3控制器来实现这个vedio

2015-08-27 14:47:57

,以及对应的波形图和 Verilog HDL 实现。我们调取的 DDR3 SDRAM 控制器给用户端预留了接口,我们可以通过这些预留的接口总线实现对该 IP 核的控制,本章节将会讲解如何根据

2022-02-08 07:08:01

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的优势。这些

2019-08-09 07:42:01

.ERROR:Xflow - 程序ngdbuild返回错误代码2.中止流程执行..我该如何纠正它并在船上测试DDR3?谢谢希望你的回答

2019-09-17 11:16:44

我正在使用vivado 2014.3,MIG 7 ddr3 verilog IP,内存时钟400MHz,用户时钟200 MHz,ddr数据宽度64位,AXI数据宽度128位。在我的系统中,我们有微型

2020-08-05 13:45:44

大家好 我的问题是DDR3校准完成失败。调试结果:dbg_wrcal_err = 1,通过波形,我们可以看到写入模式不匹配。 我的问题是MIG IP Core配置中是否有任何参数可以调整它?或者我

2020-07-23 10:09:37

嗨,任何1可以帮我写一个代码,用于连接DDR3 SDRAM内存和Virtex6 fpga。实际上我有一个小疑问,通过MIG我可以为此生成代码。如果不是如何继续这个我对这个PLZ帮助我。谢谢以上

2019-02-15 06:36:48

嗨,我即将使用Virtex-4QV设备(XQR4VFX140)开始一个新项目。虽然我对使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些经验,但我发现MIG IP不支持VIRTEX-4QV器件。那可能是另类?如何将DDR2 SDRAM与此FPGA连接?弥敦道

2020-04-02 06:08:46

本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2021-04-20 06:30:52

DDR,DDR2,DDR3,DDR4,LPDDR区别文所有权归作者Aircity所有1什么是DDRDDR是Double Data Rate的缩写,即“双比特翻转”。DDR是一种技术,中国大陆工程师

2021-09-14 09:04:30

Write Leveling 和 DQS Gate Training

➢DDR3 最快速率达 800 Mbps

三、实验设计

a. 安装 DDR3 IP 核

PDS 安装后,需手动添加 DDR3 IP,请按

2023-05-19 14:28:45

和 DQS Gate Training

➢DDR3 最快速率达 800 Mbps

三、实验设计

a. 安装 DDR3 IP 核

PDS 安装后,需手动添加 DDR3 IP,请按以下步骤完成:

(1

2023-05-31 17:45:39

比较简单,就是让核0和核1同时处理DDR3中一个4K行的数据块,其中核0处理前2K行,核1处理后2K行,两者所处理数据以及所用参数都不交叉,处理后数据以EDMA data sorting模式存储至DDR3

2018-06-25 07:14:21

本帖最后由 叫我阿gu就好 于 2018-12-8 11:09 编辑

sdram~ddr3

2018-01-29 13:36:59

我需要在V7中实现与DDR3 SDRAM相同的功能和接口。这意味着命令/地址,读取数据和写入数据流的方向与MIG的方向不同。这可以实现吗?

2020-07-14 16:18:04

本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

30 不只计算机存储器系统一直需要更大、更快、功率更低、物理尺寸更小的存储器,嵌入式系统应用也有类似的要求。本应用指南介绍了逻辑分析仪在检验DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 采用90nm工艺制造的DDR3 SDRAM存储器架构支持总线速率为600 Mbps-1.6 Gbps (300-800 MHz)的高带宽,工作电压低至1.5V,因此功耗小,存储密度更可高达2Gbits。该架构无疑速度更快,容量

2010-11-07 10:39:57 3920

3920

从那时起,采用DDR2、甚至最新的DDR3 SDRAM的新设计让DDR SDRAM技术黯然失色。DDR内存主要以IC或模块的形式出现。如今,DDR4雏形初现。但是在我们利用这些新技术前,设计人员必须了解如何

2011-07-11 11:17:14 5033

5033

为解决超高速采集系统中的数据缓存问题,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行

2017-11-16 14:36:41 19504

19504

DDR3 SDRAM(Double Data Rate Three SDRAM):为双信道三次同步动态随机存取内存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 25152

25152 为了满足高速图像数据采集系统中对高带宽和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的设计方法,提出了一种基于Verilog-HDL 语言的DDR3 SDRAM

2017-11-17 14:14:02 3290

3290

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

91644 DDR3 SDRAM是DDR3的全称,它针对Intel新型芯片的一代内存技术(但目前主要用于显卡内存),频率在800M以上。DDR3是在DDR2基础上采用的新型设计,与DDR2 SDRAM相比具有功耗和发热量较小、工作频率更高、降低显卡整体成本、通用性好的优势。

2019-10-29 08:00:00 0

0 本文件定义了DDR3 SDRAM规范,包括特性、功能、交直流特性、封装和球/信号分配。本文档的目的是为符合jedec的512 MB到8 GB的x4、x8和x16 ddr3 sdram设备定义一组最低

2019-11-04 08:00:00 73

73 DDR,DDR2,DDR3,DDR4,LPDDR区别作者:AirCity 2019.12.17Aircity007@sina.com 本文所有权归作者Aircity所有1 什么是DDRDDR

2021-11-10 09:51:03 154

154 ,以及对应的波形图和 Verilog HDL 实现。我们调取的 DDR3 SDRAM 控制器给用户端预留了接口,我们可以通过这些预留的接口总线实现对该 IP 核的控制,本章节将会讲解如何根据 Xilinx 官方提供的技术参数来实现对 IP 核的写控制。写命令和写数据总线介绍DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 本文以一个案例的形式来介绍lattice DDR3 IP核的生成及调用过程,同时介绍各个接口信号的功能作用

2022-03-16 14:14:19 1803

1803

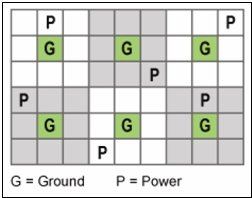

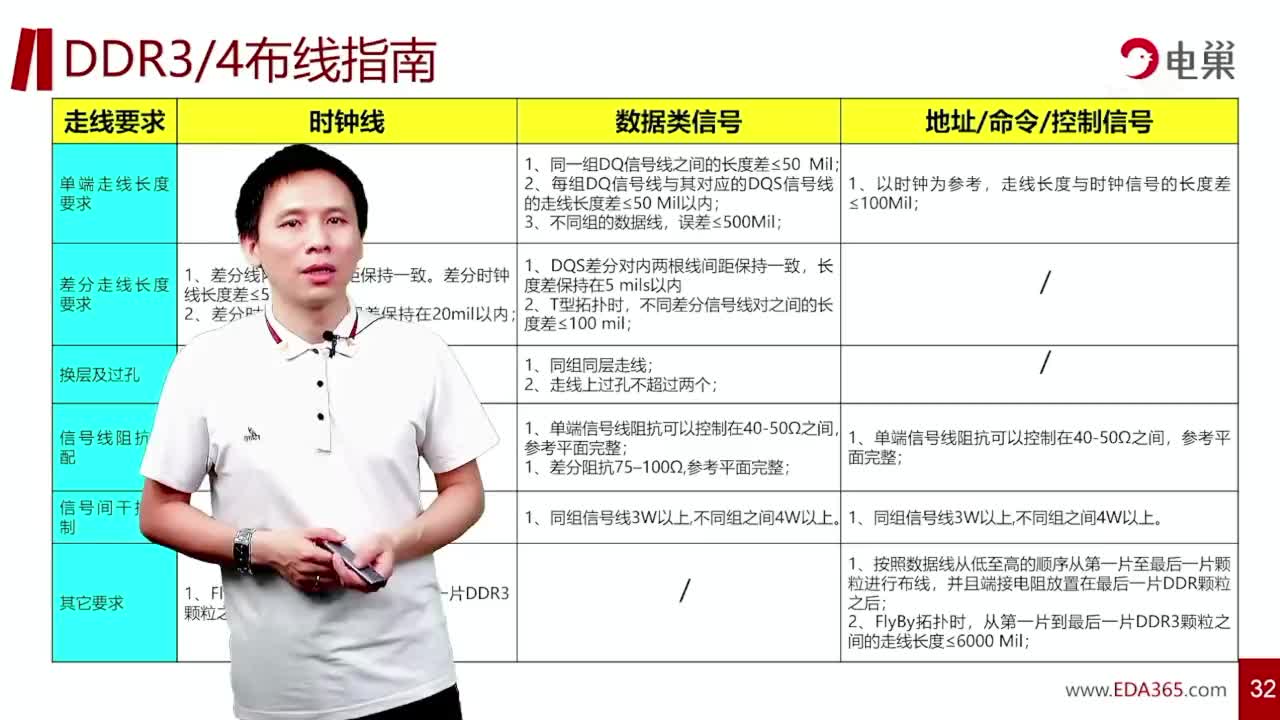

本申请说明中提供的设计指南适用于利用DDR3 SDRAM IP核的产品,它们基于内部平台的汇编由飞思卡尔半导体公司设计这些指导方针旨在最大限度地减少与董事会相关的问题多内存拓扑,同时允许最大董事会设计师的灵活性。

2022-03-31 15:28:58 0

0 这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2022-08-16 10:28:58 1241

1241 电子发烧友网站提供《Gowin DDR3 Memory Interface IP用户指南.pdf》资料免费下载

2022-09-15 14:39:09 0

0 DDR3 SDRAM使用双倍数据速率架构来实现高速操作。双倍数据速率结构是一种8n预取架构,其接口经过设计,可在I/O引脚上每个时钟周期传输两个数据字。DDR3 SDRAM的单个读或写操作有效地包括

2023-02-06 10:12:00 3

3 本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 745

745

电子发烧友App

电子发烧友App

评论