完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

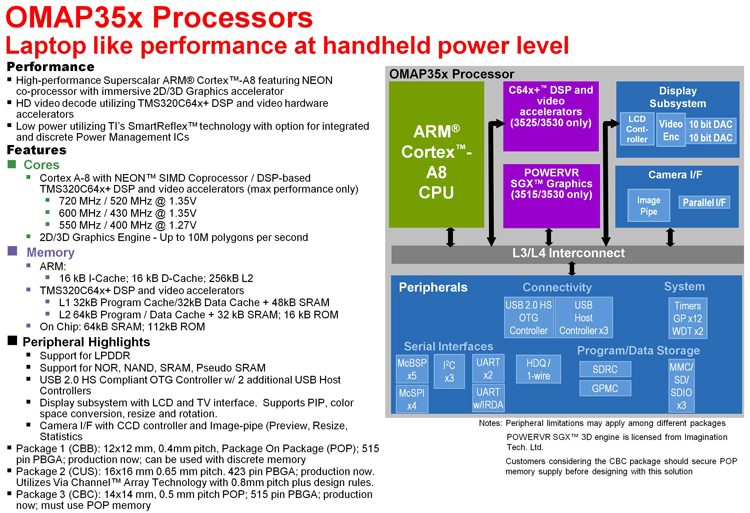

设备基于增强型OMAP 3架构。

OMAP 3架构旨在提供一流的视频,图像和图形处理足以支持以下内容:

该设备支持高级操作系统(HLOS),例如:

此OMAP设备包括高性能移动产品所需的最先进的电源管理技术。

以下子系统是设备的一部分:

该器件还提供:

OMAP35器件采用515引脚s-PBGA封装(CBB后缀),515引脚s-PBGA封装(CBC后缀)和423引脚s-PBGA封装(CUS后缀)。 CUS包中没有CBB和CBC包的某些功能。 (有关封装差异,请参见表1-1)。

本数据手册介绍了OMAP35应用处理器的电气和机械规格。除非另有说明,否则本数据手册中的信息适用于OMAP35应用处理器的商用和扩展温度版本。本数据手册由以下部分组成:

| Arm MHz (Max.) |

| Serial I/O |

| Graphics Acceleration |

| DRAM |

| Operating Temperature Range (C) |

| Approx. Price (US$) |

| OMAP3503 | OMAP3515 |

|---|---|

| 720 | 720 |

|

USB I2C McBSP McSPI UART |

USB I2C McBSP McSPI UART |

| 1 3D | |

| LPDDR | LPDDR |

|

-40 to 105 0 to 90 |

-40 to 105 0 to 90 |

| 23.00 | 1ku | 26.52 | 1ku |