、氮化镓、磷化镓、锗、磷化铟、铌酸锂、蓝宝石、硅、碳化硅、玻璃不同材质晶圆的量测。WD4000国产晶圆几何形貌量测设备自动测量Wafer厚度、表面粗糙度、三维形貌、单

2024-03-15 09:22:08

,而实际的产品误差值会更小。晶发电子实际测试数据显示,行业标准为±30ppm,我司产晶振可实现±5ppm。

·温度频差

在不同的温度范围(-2070℃普通级/民用级晶振;-4085℃工业级晶振;-55

2024-03-04 13:48:39

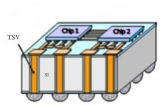

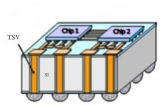

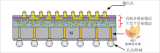

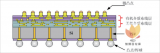

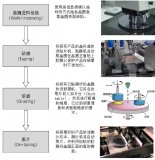

的 2.5D/3D 封装技术可以实现芯片之间的高速、低功耗和高带宽的信号传输。常见的垂直 TSV 的制造工艺复杂,容易造成填充缺陷。锥形 TSV 的侧壁倾斜,开口较大,有利于膜层沉积和铜电镀填充,可降低工艺难度和提高填充质量。在相对易于实现的刻蚀条件下制备

2024-02-25 17:19:00 119

119

以硅通孔(TSV)为核心的 2.5D/3D 封装技术可以实现芯片之间的高速、低功耗和高带宽的信号传输。

2024-02-25 16:51:10 482

482

WD4000无图晶圆几何形貌测量系统是通过非接触测量,将晶圆的三维形貌进行重建,强大的测量分析软件稳定计算晶圆厚度,TTV,BOW、WARP、在高效测量测同时有效防止晶圆产生划痕缺陷。可兼容不同材质

2024-02-21 13:50:34

热阻测试和可靠性测试。结果表明,该半烧结型银浆的工艺操作性好,烧结后胶层空洞率低;当胶层厚度控制在30 µm左右时,剪切强度达到25.73 MPa;采用半烧结型银浆+TSV转接板的方式烧结功放芯片,其导热性能满足芯片的散热要求;经过可靠性测

2024-01-17 18:09:11 185

185

ADuCM360下载程序需要专用转接板吗?还是USB转TTL可直接下载?在网上看到似乎需要一个这样的转接板,接口定义也是如此。

2024-01-15 07:27:17

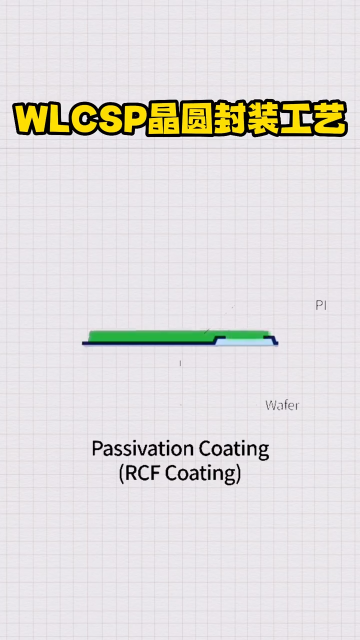

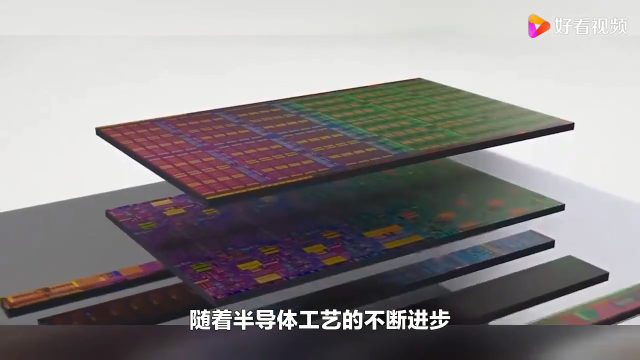

传统封装需要将每个芯片都从晶圆中切割出来并放入模具中。晶圆级封装 (WLP) 则是先进封装技术的一种 , 是指直接封装仍在晶圆上的芯片。

2024-01-12 09:29:13 336

336

WD4000无图晶圆几何形貌测量设备采用高精度光谱共焦传感技术、光干涉双向扫描技术,完成非接触式扫描并建立3D Mapping图,实现晶圆厚度、TTV、LTV、Bow、Warp、TIR、SORI、等

2024-01-10 11:10:39

硅通孔技术(TSV,Through Silicon Via)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的技术,是2.5D/3D 封装的关键工艺之一。通过垂直互连减小互连长度、信号延迟,降低电容、电感,实现芯片间低功耗、高速通讯,增加带宽和实现小型化。

2024-01-09 09:44:13 1879

1879

WD4000半导体晶圆厚度测量系统自动测量Wafer厚度、表面粗糙度、三维形貌、单层膜厚、多层膜厚。1、使用光谱共焦对射技术测量晶圆Thickness、TTV、LTV、BOW、WARP、TIR

2024-01-09 09:08:07

元件,具有完全的偏振灵活性。其他功能包括温度增益补偿和温度报告。该芯片的所有引脚均具有 ESD 保护,采用 +1.2V 电源供电,并采用 WLCSP(晶圆级芯片级

2024-01-02 15:34:01

TC-Wafer是将高精度温度传感器镶嵌在晶圆表面,对晶圆表面的温度进行实时测量。通过晶圆的测温点了解特定位置晶圆的真实温度,以及晶圆整体的温度分布,同还可以监控半导体设备控温过程中晶圆发生的温度

2023-12-21 08:58:53

WD4000晶圆几何形貌测量设备采用白光光谱共焦多传感器和白光干涉显微测量双向扫描技术,完成非接触式扫描并建立表面3D层析图像,实现Wafer厚度、翘曲度、平面度、线粗糙度、总体厚度变化(TTV

2023-12-20 11:22:44

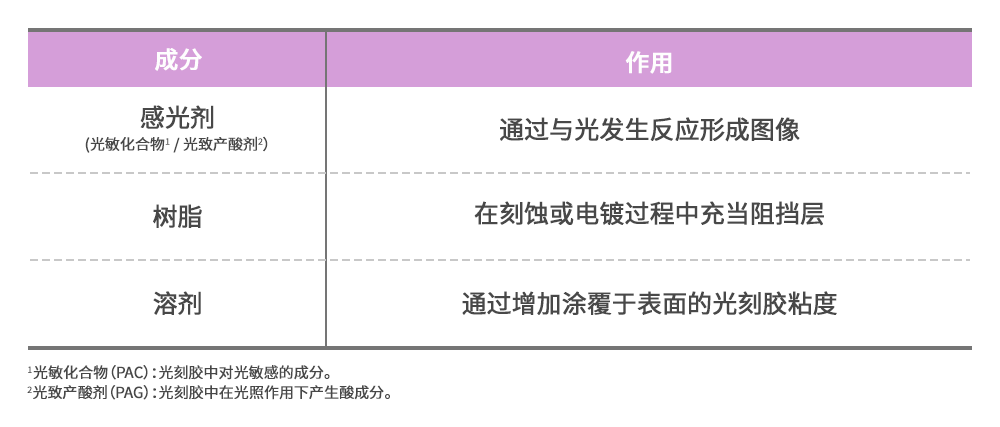

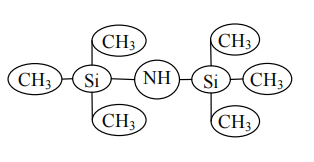

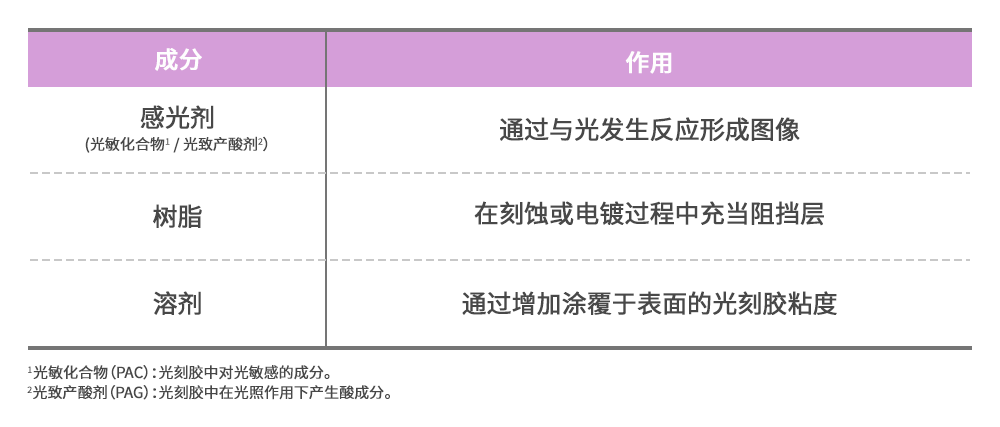

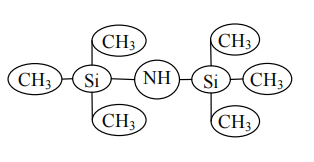

本篇文章将探讨用于晶圆级封装(WLP)的各项材料,从光刻胶中的树脂,到晶圆承载系统(WSS)中的粘合剂,这些材料均在晶圆级封装中发挥着重要作用。

2023-12-15 17:20:36 807

807

中图仪器WD4000无图晶圆几何形貌量测系统自动测量Wafer厚度、表面粗糙度、三维形貌、单层膜厚、多层膜厚。它采用白光光谱共焦多传感器和白光干涉显微测量双向扫描技术,完成非接触式扫描并建立表面3D

2023-12-14 10:57:17

以来迅速发展的新型微电子封装技术,包括焊球阵列封装(BGA)、芯片尺寸封装(CSP)、圆片级封装(WLP)、三维封装(3D)和系统封装(SIP)等项技术。介绍它们的发展状况和技术特点。同时,叙述了微电子

2023-12-11 01:02:56

~ 3.63V)

针对低功耗设计进行优化

支持最小封装尺寸至1.6 x 1.2 x 0.6mm

气密金属陶瓷封装

通过AEC-Q200认证(车规级)

02

SPXO & TCXO

2023-12-07 09:30:19

设计时,AD2S1210的时钟输入采用8.192MHZ的有源晶振,选择晶振时对有源晶振的功率有什么要求???一个有源晶振能不能给两个AD2S1210芯片提供时钟输入???感谢!

2023-12-07 07:07:43

晶圆测温系统tc wafer晶圆表面温度均匀性测温晶圆表面温度均匀性测试的重要性及方法 在半导体制造过程中,晶圆的表面温度均匀性是一个重要的参数

2023-12-04 11:36:42

率低;当胶层厚度控制在30μm左右时,剪切强度达到25.73MPa;采用半烧结型银浆+TSV转接板的方式烧结功放芯片,其导热性能满足芯片的散热要求;经过可靠性测试后,烧结芯

2023-12-04 08:09:57 446

446

3D-IC 中 硅通孔TSV 的设计与制造

2023-11-30 15:27:28 212

212

三星电子和sk海力士用于tsv蚀刻的设备都是Syndion。synthion是典型的深硅蚀刻设备,深度蚀刻到晶片内部,用于tsv和沟槽等的高度和宽度比的形成。泛林集团 sabre 3d将用于用铜填充蚀刻的晶圆孔来制作线路的tsv线路。

2023-11-30 10:15:57 324

324 你好:

我目前在用adau1442,现在调试方式都是用贵公司的USBI转接板,我是想了解,是否可以不通过USBI转接板直接进行软件控制呢或者贵公司可以提供转接板资料我直接集成到我的电路板上,这样以便产品的推广。

谢谢

2023-11-30 07:30:44

TSV是2.5D和3D集成电路封装技术中的关键实现技术。半导体行业一直在使用HBM技术将DRAM封装在3DIC中。

2023-11-27 11:40:20 211

211

请问像AD8233一样的晶圆封装在PCB中如何布线,芯片太小,过孔和线路都无法布入,或者有没有其他封装的AD8233

2023-11-14 07:01:48

并瓜分全部的市场份额,在新应用催化下,也为后端封测厂和TSV设备公司带来了市场机会。 硅通孔 / TSV(Through-Silicon Via) 硅通孔TSV是一种能让3D封装遵循摩尔定律演进的互连

2023-11-09 13:41:21 2341

2341

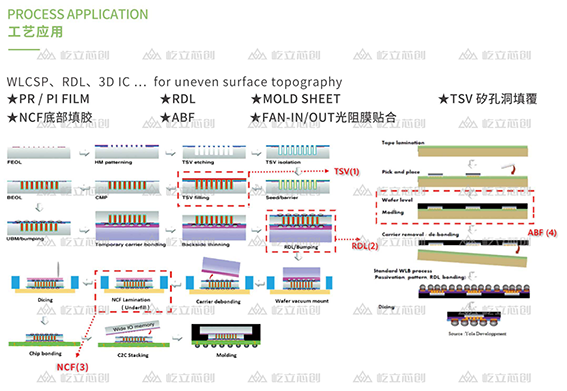

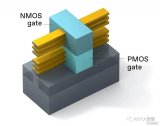

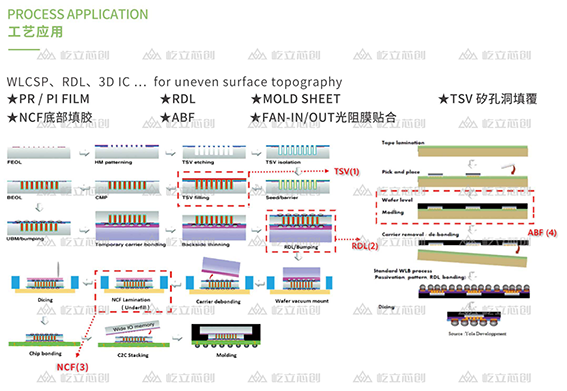

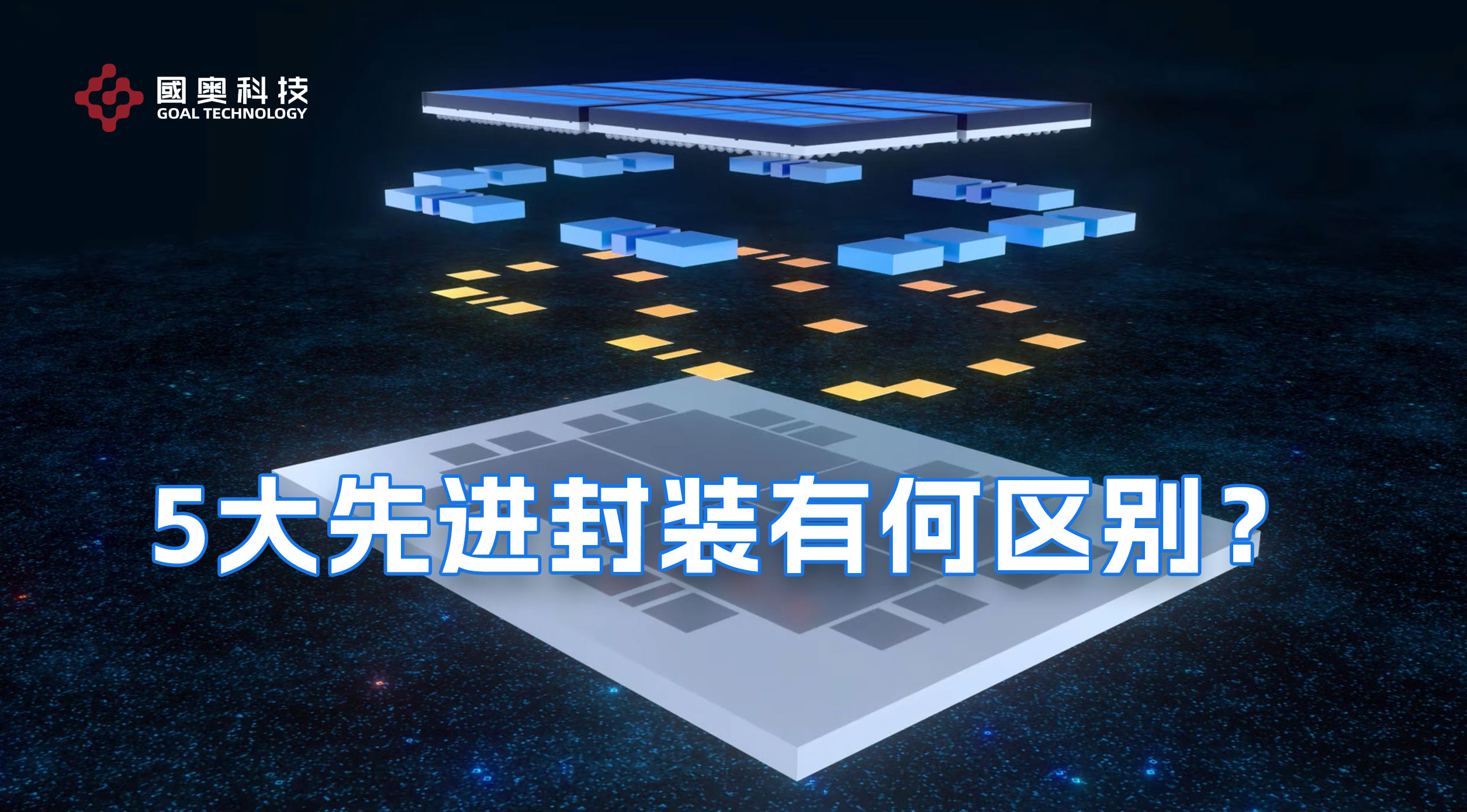

在上篇文章中介绍了扇入型晶圆级芯片封装(Fan-In WLCSP)、扇出型晶圆级芯片封装(Fan-Out WLCSP)、重新分配层(RDL)封装、倒片(Flip Chip)封装,这篇文章着重介绍硅通孔(TSV)封装工艺。

2023-11-08 10:05:53 1825

1825

。WD4000晶圆几何形貌测量及参数自动检测机采用高精度光谱共焦传感技术、光干涉双向扫描技术,完成非接触式扫描并建立3D Mapping图,实现晶圆厚度、TTV、LTV、B

2023-11-06 10:49:18

WD4000系列半导体晶圆几何形貌自动检测机采用高精度光谱共焦传感技术、光干涉双向扫描技术,完成非接触式扫描并建立3D Mapping图,实现晶圆厚度、TTV、LTV、Bow、Warp、TIR

2023-11-06 10:47:07

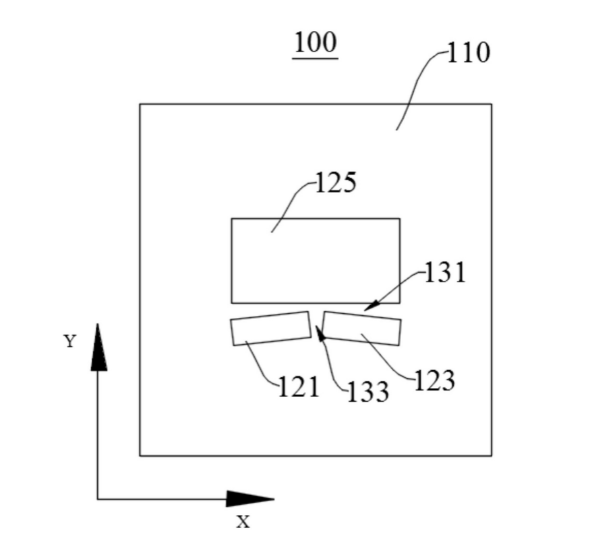

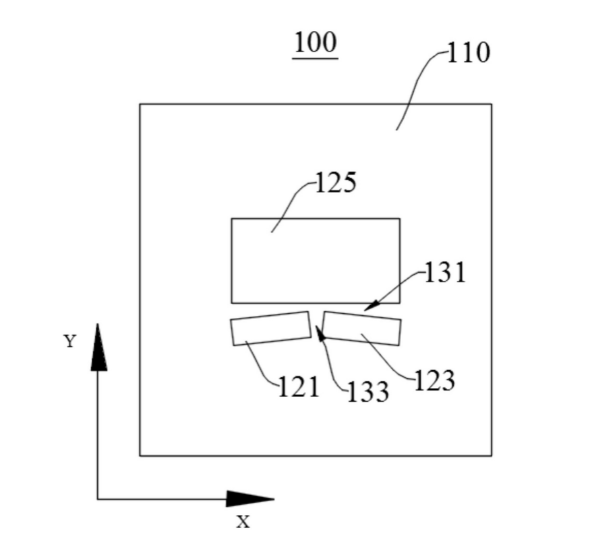

专利摘要显示,本公开实施例提供了一种封装结构和封装方法,涉及半导体封装技术领域。该封装结构包括转接板以及间隔贴装在转接板上的第一器件、第二器件和第三器件,第一器件、第二器件和第三器件之间相互间隔设置,以在第三器件朝向第一器件和第二器件的一侧形成第一间隙槽,第一器件和第二器件之间形成第二间隙槽

2023-11-06 10:44:22 301

301

SOM-3588-LGA 是一款基于Rockchip RK3588芯片平台,采用LGA(506pin)封装设计的一款极小尺寸的商规级核心板。现在核心板 SOM-3588-LGA(商业级

2023-10-23 11:50:30

WD4000半导体晶圆表面三维形貌测量设备自动测量Wafer厚度、表面粗糙度、三维形貌、单层膜厚、多层膜厚。可广泛应用于衬底制造、晶圆制造、及封装工艺检测、3C电子玻璃屏及其精密配件、光学加工、显示

2023-10-23 11:05:50

WD4000半导体晶圆检测设备自动测量Wafer厚度、表面粗糙度、三维形貌、单层膜厚、多层膜厚。1、使用光谱共焦对射技术测量晶圆Thickness、TTV、LTV、BOW、WARP、TIR、SORI

2023-10-19 11:08:24

WD4000无图晶圆几何量测系统自动测量 Wafer 厚度 、表面粗糙度 、三维形貌 、单层膜厚 、多层膜厚 。使用光谱共焦对射技术测量晶圆 Thickness 、TTV 、LTV 、BOW

2023-10-18 09:09:00

[迪拜,阿联酋,2023年10月17日]今日,在GITEX2023期间,主题为“IP商机无限,共赢智能化未来”的商业市场IP Club备受瞩目。来自阿联酋、沙特等多个国家和地区的70多位伙伴共聚一堂

2023-10-17 23:30:02 370

370

手册,更有MAX77540EVKIT: Evaluation Kit for the MAX77540 in

WLP Package Data Sheet的引脚图、接线图、封装手册、中文资料、英文资料

2023-10-16 19:10:59

MAX6069: 1μA WLP Precision Shunt Voltage Reference Data Sheet的引脚图、接线图、封装手册、中文资料、英文资料,MAX6069: 1μA WLP

2023-10-16 18:45:26

MAX17227JEVK-WLP: Evaluation Kit for the MAX17227J Data Sheet的引脚图、接线图、封装手册、中文资料、英文资料,MAX17227JEVK-WLP

2023-10-16 18:35:32

手册,更有Evaluation Kit for the MAX18000 and MAX18002 in WLP Package Data Sheet的引脚图、接线图、封装手册、中文资料、英文资料

2023-10-12 18:53:03

MAX38647BEVKIT: MAX38647B WLP Evaluation Kit Data Sheet的引脚图、接线图、封装手册、中文资料、英文资料,MAX38647BEVKIT: MAX38647B WLP

2023-10-12 18:47:52

:WLP包装数据表MAX77837MAX77837的 MAX77837评价包的引脚图、接线图、封装手册、中文资料、英文资料,MAX77837EVKIT:WLP包装数据表MAX77837MAX77837

2023-10-10 19:15:37

)数据表的评估工具包的引脚图、接线图、封装手册、中文资料、英文资料,MAX77857WGEVKIT:MAX77857(WLP)数据表的评估工具包真值表,MAX77857WGEVKIT:MAX77857(WLP)数据表的评估工具包管脚等资料,希望可以帮助到广大的电子工程师们。

2023-10-09 18:38:40

MAX400008-MAX400009:220ns, 12微A, 6-Bum WLP 与关闭数据表的比较的引脚图、接线图、封装手册、中文资料、英文资料,MAX400008-MAX400009:220ns, 12微A, 6-Bum

2023-10-07 17:52:07

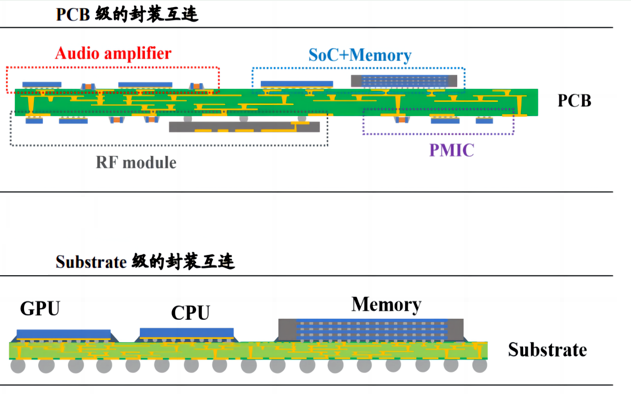

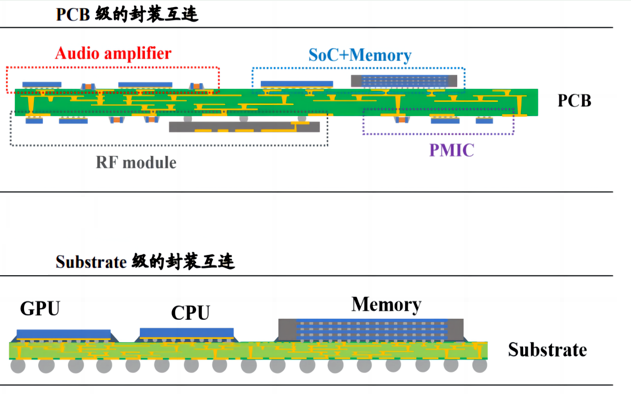

先进封装技术以SiP、WLP、2.5D/3D为三大发展重点。先进封装核心技术包括Bumping凸点、RDL重布线、硅中介层和TSV通孔等,依托这些技术的组合各厂商发展出了满足多样化需求的封装解决方案,SiP系统级封装、WLP晶圆级封装、2.5D/3D封装为三大发展重点。

2023-09-28 15:29:37 1608

1608

先进封装中硅通孔(TSV)铜互连电镀研究进展

2023-09-06 11:16:42 534

534

的顶部和底部都暴露出来,用铜填充的过孔就可以通过晶片提供互连。这提供了由晶片隔离和保护的坚固耐用的互连。它还提供了使用小得多的体积的互连,同时减少了对与现代微电子封装相关的大多数封装的需求。本工作使用两种方法生产铜基TSV,

2023-08-30 17:19:11 326

326

PFA花篮(PFA wafer Cassette) 又名 清洗花蓝 ,铁氟龙卡匣 , 铁氟龙晶舟盒 ,铁氟龙晶圆盒为承载半导体晶圆片/硅片

2023-08-29 08:57:51

先进封装处于晶圆制造与封测的交叉区域 先进封装处于晶圆制造与封测制程中的交叉区域,涉及IDM、晶圆代工、封测厂商。先进封装要求在晶圆划片前融入封装工艺步骤,具体包括应用晶圆研磨薄化、重布线(RDL

2023-08-07 10:59:46 852

852

来源:半导体风向标 从HBM存储器到3D NAND芯片,再到CoWoS,硬件市场上有许多芯片是用英文称为TSV构建的,TSV是首字母缩写,意为“通过硅通孔”并翻译为via硅的事实,它们垂直地穿过

2023-07-26 10:06:15 619

619 TSV不仅赋予了芯片纵向维度的集成能力,而且它具有最短的电传输路径以及优异的抗干扰性能。随着摩尔定律慢慢走到尽头,半导体器件的微型化也越来越依赖于集成TSV的先进封装。

2023-07-25 10:09:36 470

470

SD NAND 测试板,CSSDBRD010转接板,适用LGA-8

2023-07-05 09:10:05

编者注:TSV是通过在芯片与芯片之间、晶圆和晶圆之间制作垂直导通;TSV技术通过铜、钨、多晶硅等导电物质的填充,实现硅通孔的垂直电气互联,这项技术是目前唯一的垂直电互连技术,是实现3D先进封装的关键技术之一。

2023-07-03 09:45:34 2001

2001

随着三维集成技术的发展,如何将不同材料、结构、工艺、功能的芯片器件实现一体化、多功能集成化是未来系统集成发展的重点。基于TSV、再布线(RDL)、微凸点(Micro Bump)、倒装焊(FC)等关键工艺的硅转接基板集成技术是将处理器、存储器等多种芯片集成到同一个基板上,可提供高密度引脚的再分布。

2023-07-01 10:35:21 1392

1392

晶圆测温系统,晶圆测温热电偶,晶圆测温装置一、引言随着半导体技术的不断发展,晶圆制造工艺对温度控制的要求越来越高。热电偶作为一种常用的温度测量设备,在晶圆制造中具有重要的应用价值。本文

2023-06-30 14:57:40

小型0.73mm x 0.73mm(约两个0402电阻大小)4引脚晶圆级封装(WLP),以及5引脚SOT23封装。该器件系列采用1.7V至5.5V( VCC&nbs

2023-06-28 11:35:45

GE211是机智云自行研发的定制转接板,主要适用于白色智能家电等设备应用。转接板采用ESP32-C3-WROOM-02通信模块,具备支持WiFi和BLE的双模无线通信能力,并且还包含TTL电平转换

2023-06-27 18:02:57

不同封装的晶振,有什么差别没有

2023-06-26 06:09:47

硅通孔(Through Si Vias,TSV)硅转接基板技术作为先进封装的一种工艺方式,是实现千级IO芯片高密度组装的有效途径,近年来在系统集成领域得到快速应用。

2023-06-16 16:11:33 342

342

芯片功能测试常用5种方法有板级测试、晶圆CP测试、封装后成品FT测试、系统级SLT测试、可靠性测试。

2023-06-09 16:25:42

由于摩尔定律逐渐接近其物理极限,为进一步追求速度、功耗、功能与制造成本的平衡,后道封装更加强调封装集成度、I/O引脚密度及功能集成度,因此SiP、2.52D/3D集成及WLP成为未来集成电路后道封装

2023-05-31 11:02:40 1312

1312

无论是采用Fan-in还是Fan-out,WLP晶圆级封装和PCB的连接都是采用倒装芯片形式,芯片有源面朝下对着印刷电路板,可以实现最短的电路径,这也保证了更高的速度和更少的寄生效应。

2023-05-24 10:15:58 1529

1529

随着晶圆代工制程不断缩小,摩尔定律逼近极限,先进封装是后摩尔时代的必然选择。其中,利用高端封装融合最新和成熟节点,采用系统封装(SiP)和基于小芯片的方法,设计和制造最新的SoC产品已经成为

2023-05-23 12:29:11 2873

2873

随着半导体工艺的不断进步,封装技术也在逐渐演变。晶圆级封装(Wafer-Level Packaging,WLP)和传统封装技术之间的差异,以及这两种技术在半导体行业的发展趋势和应用领域,值得我们深入了解。

2023-05-12 13:26:05 681

681

请教一下,有部分工程师使用的0402以上阻容件封装焊盘呈子弹头设计(焊盘内测导圆),这样设计走什么优缺点呢?

2023-05-11 11:56:44

半导体大规模生产过程中需要在晶圆上沉积集成电路芯片,然后再分割成各个单元,最后再进行封装和焊接,因此对晶圆切割槽尺寸进行精准控制和测量,是生产工艺中至关重要的环节。

2023-05-09 14:12:38

硅通孔(TSV) 是当前技术先进性最高的封装互连技术之一。基于 TSV 封装的核心工艺包括 TSV 制造、RDL/微凸点加工、衬底减薄、圆片键合与薄圆片拿持等。

2023-05-08 10:35:24 2021

2021

半导体大规模生产过程中需要在晶圆上沉积集成电路芯片,然后再分割成各个单元,最后再进行封装和焊接,因此对晶圆切割槽尺寸进行精准控制和测量,是生产工艺中至关重要的环节。

2023-04-28 17:41:49

MICROFJ-60035-TSV-TR1

2023-04-06 23:35:33

MICROFJ-30035-TSV-TR

2023-04-06 23:31:03

MICROFJ-60035-TSV-TR

2023-04-06 23:31:03

,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。)

2.高传输速度(与传统金属引线产品相比,WLP一般有较短的连接线路,在高效能要求如高频下,会有较好的表现。)

3.高密度连接(WLP可运用数组式连接,芯片

2023-04-06 17:50:56 0

0 wafer晶圆GDP703202DG恒流1mA表压2Mpa裸片压力传感器die产品概述:GDP0703 型压阻式压力传感器晶圆采用 6 寸 MEMS 产线加工完成,该压力晶圆的芯片由一个弹性膜及集成

2023-04-06 14:48:12

是2.5D封装,将光芯片和电芯片都和一个中介板相连(通过TSV和bump),中介板可以实现芯片间高速互联,这个中介板称为interposer。【TSV是硅通孔,可以实现硅芯片内部的互联;bump是金属

2023-03-29 10:48:47

TSV911AIDCKR

2023-03-28 13:13:59

采用 SO-8 封装的 16 位轨至轨微功耗 DAC

2023-03-28 01:07:56

采用 SO-8 封装的 16 位轨至轨微功耗 DAC

2023-03-23 08:13:43

采用 SO-8 封装的 16 位轨至轨微功耗 DAC

2023-03-23 05:00:40

电子发烧友App

电子发烧友App

评论