接口/时钟/PLL

电子发烧友网接口/时钟/PLL栏目提供pll锁相环,锁相环,锁相环电路,锁相环原理,数字锁相环等接口/时钟/PLL设计所需的所有最新行业新闻、产品信息及技术热点方案及介绍。展商资讯|大普通信—打造国产高性能时钟芯片全链条

作为展示全球电子信息产业最新产品和技术的国家级平台,中国电子信息博览会将于2022年5月17日至19日在深圳会展中心举办第十届中国电子信息博览会(CITE 2022)。 届时,大普通信(展位号...

2022-04-08 10361

千字干货,信号反射与反弹图

对于传输线而言,当信号从左向右传播时,如果走线突然加粗,那么对应的单位长度电感和电位长度电容就会发生变化,使得阻抗突变,Z1≠Z2,阻抗突变会引起信号反射。...

2022-02-16 3906

三个经典的运放电路

对于运算放大器而言,分析的思路大同小异,都是以“虚短虚断”为基本原则,这里结合虚短虚断原则,介绍下反相放大电路、同相放大电路和跟随器的计算过程,理解这三个过程以后,就可以...

2022-02-16 9311

LDO输出为什么并联接地电阻?

LDO输出接了一个负载,负载有低功耗和普通模式两种工作模式,低功耗模式时正常,普通模式时工作也正常,但是从低功耗切换到普通模式时,却发生了异常,测量得到LDO的输出电压波形大约如...

2022-02-09 5006

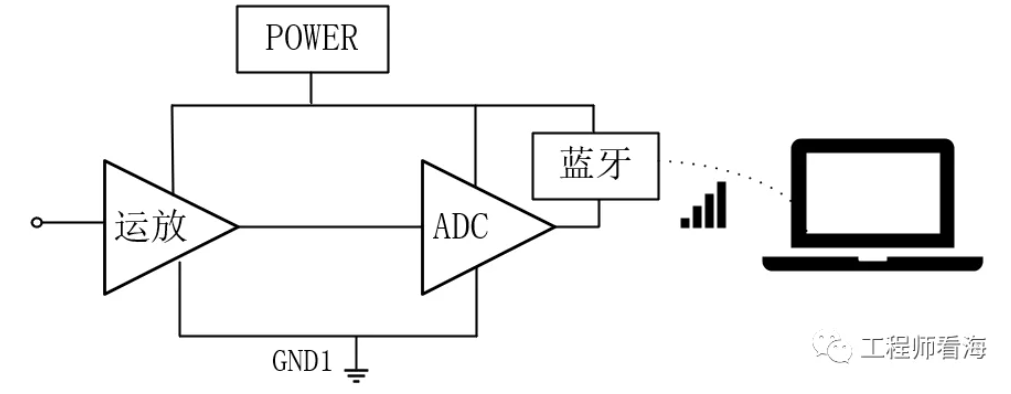

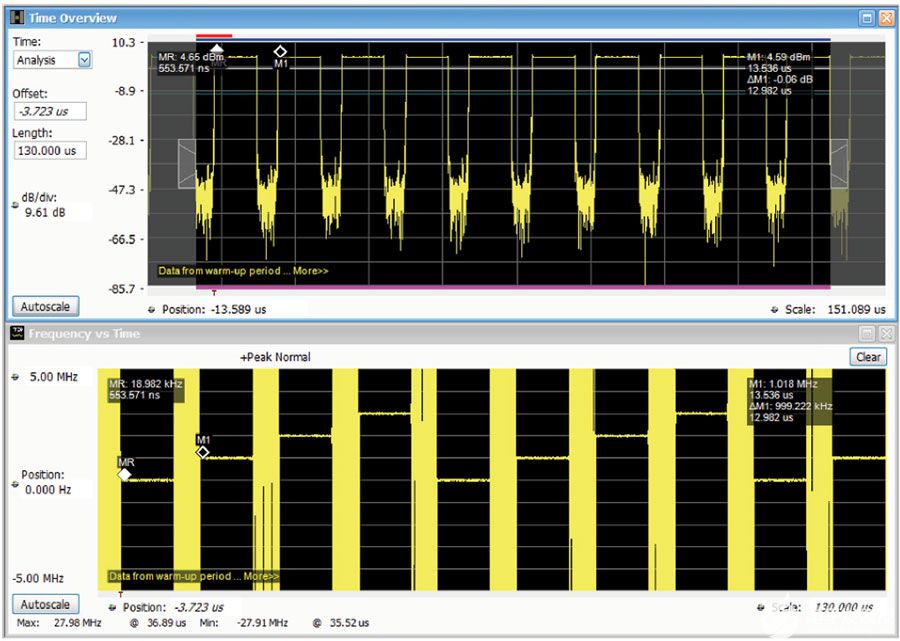

CC2640蓝牙干扰运放的案例分享

原文来自公众号:工程师看海 最近一段时间被拉去支援哥们的一个微弱信号采集项目,解决关于蓝牙干扰模拟信号采集的问题,硬件工程师也要有一定的软件背景,看海采坑小课堂今天和大家...

2022-01-24 10791

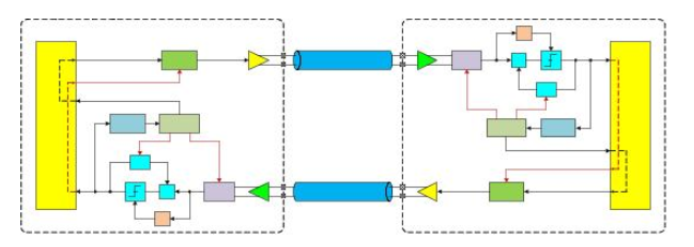

提供显著跳频(FH)优势的下一代软件定义无线电收发器

本文深入探讨了跳频(FH)的概念,以及如何通过灵活设计 ADRV9002 SDR 收发器的锁相环(PLL)架构来实现四大跳频特性。这些特性可为用户提供强大的跳频功能,让他们能够处理单通道和双通道操作模...

2021-12-08 5626

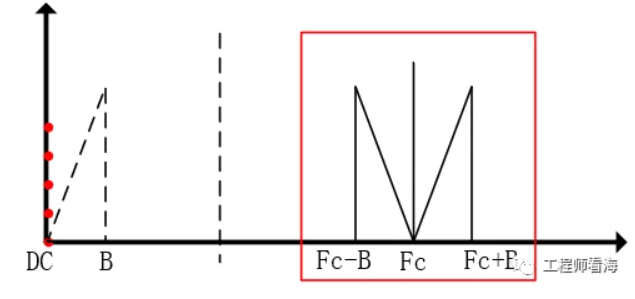

看,这就是调制解调原理分析!附仿真文件

原文来自公众号:工程师看海 调制与解调是通讯中非常常见的技术,其实在微弱信号采集中也会用到此技术,那么调制与解调究竟是怎么一回事呢?关注公众号:工程师看海,让我带你慢慢研...

2021-12-01 6796

SiTime高性能MEMS时钟方案在5G中的应用

一、什么是5G 5G是第五代移动通信技术(5th-Generation)的简称,是新一代的蜂窝移动通信技术,也是继4G、3G、2G系统之后的延伸,5G的性能目标是高数据速率、减少延迟、节少能源、降低成本、提...

2021-10-27 765

大咖谈国产模拟IC创新:从EDA、信号链,到大功率功放、CPU大电流电源芯片…

“浣沙淘金,模拟论芯”,2021年9月28日,由全球知名电子科技媒体电子发烧友主办的 2021第三届中国模拟半导体大会在中国深圳成功举办,在本次大会上,来自华大九天、芯海科技、昱盛电子、...

2021-10-08 9963

为什么低通滤波器也能变成积分器?

原文来自公众号:工程师看海 在数据采集领域,RC低通滤波器是最常见的一种信号调理电路,用于抑制高频干扰或噪声,下图是无源RC低通滤波器的最简单示意图。 仅仅一个电阻和电容就可以实...

2021-09-22 7076

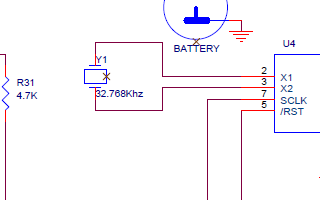

【紫光同创国产FPGA教程】【第二十二章】RTC时间实验

RTC(Real-Time Clock)实时时钟为系统提供一个可靠的时间,并且在断电的情况下,RTC实时时钟也可以通过电池供电,一直运行下去。RTC通过类SPI总线向FPGA传送8位数据(BCD码)。数据包括秒,分,小...

2021-03-10 15271

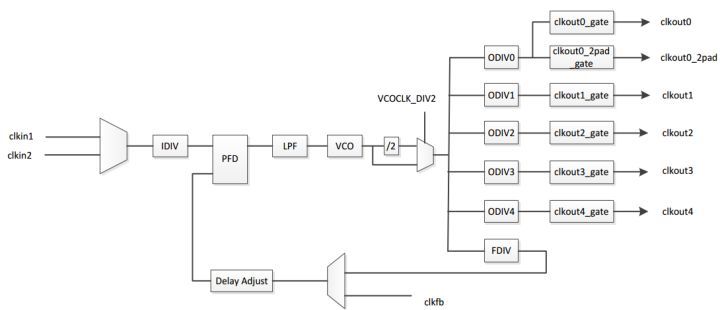

【紫光同创国产FPGA教程】【第四章】PDS下PLL实验

很多初学者看到板上只有一个50Mhz时钟输入的时候都产生疑惑,时钟怎么才50Mhz?如果要工作在100Mhz、150Mhz怎么办?在很多FPGA芯片内部都集成了PLL,其他厂商可能不叫PLL,但是也有类似的功能模...

2021-02-04 6521

时钟信号测试有回沟怎么办?测试点位置与芯片DIE分析

信号回沟,即波形边缘的非单调性,是时钟的大忌,尤其是出现在信号的门限电平范围内时,由于容易导致误触发,更是凶险无比。所以当客户测试发现时钟信号回沟,抱着一心改板的沉痛心情...

2020-11-26 6744

ADMV8416/ADMV8432与PLL/VCO IC配合实现PLL/VCO技术的提升

多年来,微波频率生成使工程师面临严峻的挑战,不仅需要对模拟、数字、射频(RF)和微波电子有深入的了解,尤其是锁相环(PLL)和压控振荡器(VCO)集成电路组件方面,还需要具备可调滤波、宽带...

2020-10-14 4140

实时时钟芯片M41T62主要特性介绍

意法半导体推出的M41T62尺寸仅为3.2 x 1.5mm;而且具备低功耗实时时钟与晶振二合一芯片。 M41T62特别适用于电池供电的便携式产品设计。1.3V至4.4V的低工作电压让这款时钟芯片可直接由锂电池供电...

2020-08-28 1983

PCIe Gen3/Gen4接收端链路均衡测试(上篇:理论篇)

在PCIe 3.0和4.0中的链路均衡技术相较于先前代要复杂得多,这样一种动态均衡技术可以分为两个方面进行讨论。...

2020-04-07 9451

Spartan-3的FPGA与DDR2 SDRAM的接口实现

DDR2 设备概述:DDR2 SDRAM接口是源同步、支持双速率传输。比如DDR SDRAM ,使用SSTL 1.8V/IO电气标准,该电气标准具有较低的功耗。与TSOP比起来,DDR2 SDRAM的FBGA封装尺寸小得多。...

2019-06-22 1723

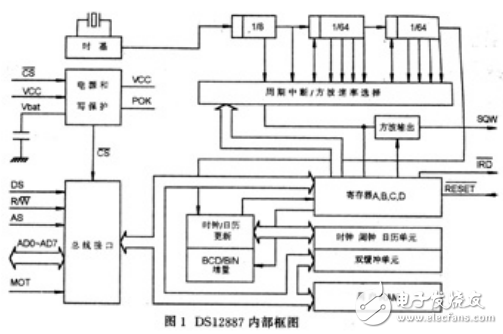

ds12887工作原理及应用设计

本文主要介绍了ds12887工作原理及应用设计。DS12887是采用CMOS技术制成,把时钟芯片所需的晶振和外部锂电池相关电路集于芯片内部,同时它与目前 IBM AT计算机常用的时钟芯片MC146818B和DS1287管脚...

2018-03-16 16181

高速串行总线的信号完整性验证

随着第三代I/O技术的出现,人们开始步入高速传输的时代。在使用PCI Express、SATA等高速串行总线时,如何保持信号的完整性是一个挑战。本文结合实例,介绍信号完整性验证的基础知识和方法。...

2018-02-26 2132

绝对干货!PLL芯片接口常见的11个问题以及应对方法

锁相环(PLL)是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。在使用PLL的过程中您都遇到过哪些问题呢?咱们工程师...

2018-03-09 12733

选择PLL频率合成器时,你必须考虑的键性能参数解说

利用频率合成器,你可以产生单一参考频率的各种不同倍数的输出频率。其主要应用是为RF信号 的上变频和下变频产生本振(LO)信号。 频率合成器在锁相环(PLL)中工作,其中鉴频鉴相器(...

2018-03-09 1406

解决串行接口中的信号完整性问题

一直以来,信号完整性都是模拟工程师考虑的问题,但是随着串行数据链接的传输速率向GHz级发展,数字硬件设计人员现在也必须关注这个重要的问题。...

2018-02-10 1563

信号完整性的价值:存储器接口设计

存储器和其它组件之间的问题通常存在于这些器件之间的接口上,这些系统级的问题有时候是难以觉察的。本文详述了一种能够很容易地识别和解决这些出现在存储器接口上问题的测试工具,从...

2018-02-08 1225

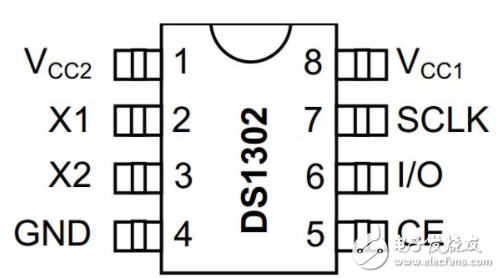

关于实时时钟模块DS1302的介绍

DS1302实时时钟芯片广泛应用于电话、传真、便携式仪器等产品领域,它可以对年、月、日、周、时、分、秒进行计时,且具有闰年补偿等多种功能。...

2018-01-30 18142

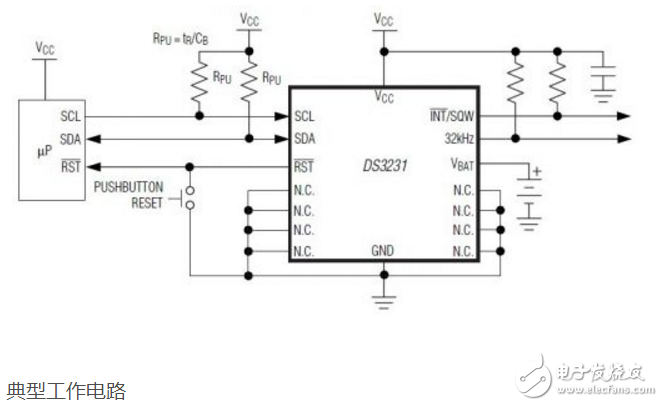

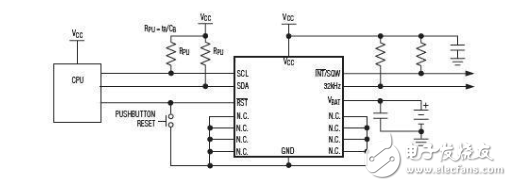

实时时钟DS3231读取信息出错的分析

在单片机系统设计中 ,对系统的抗干扰设计、信号完整性设计、时序设计大都能引起关注;但对由于备用电池与系统电源上电或电源切换导致个别芯片的时序不稳定 ,引起不能正常工作或启动的...

2018-01-29 6623

ds3231时钟模块测试程序

DS3231运行于12小时或者24小时模式,小时寄存器的第六位定义为12小时或者24小时的选择位,该位为高时,选择12小时模式,在12小时模式下,第五为为AM/PM指示位,逻辑高时为PM。...

2018-01-29 13412

DS3231高精度时钟模块程序

DS3231是低成本,高精度I2C实时时钟(RTC),具有集成的温补晶体振荡器(TCXO)和1个32.768kHz的晶体。该晶体包含电池输入端,断开主电源仍可保持精确计时。集成晶体振荡器可提高器件的长期精...

2018-01-29 26707

基于DS1307的可调实时时钟系统设计

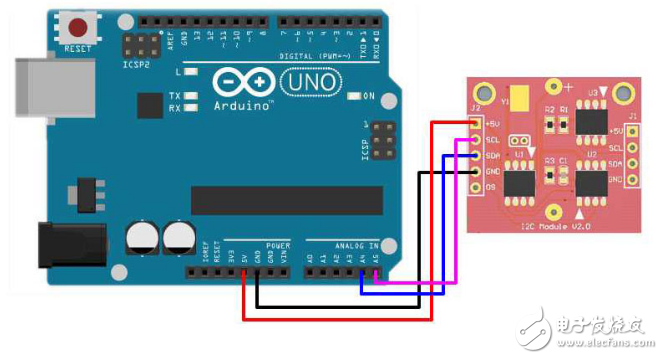

DS1307是一款具有I2C总线接口的实时时钟芯片,要驱动具有I2C总线接口的DS1307芯片,一种办法是选择一款带有I2C总线接口的高档单片机,然而,在很多小型仪器仪表中以及在单片机的教学环境中,...

2018-01-26 9831

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |