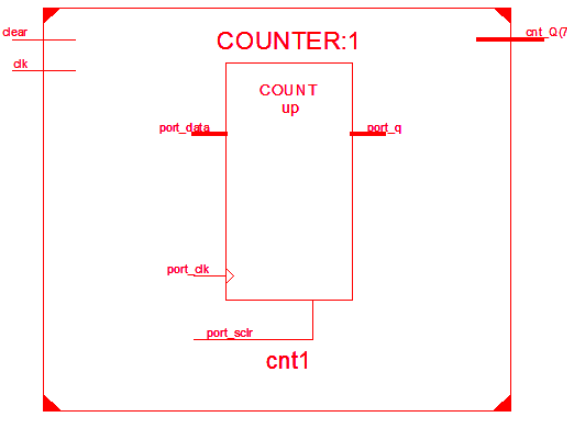

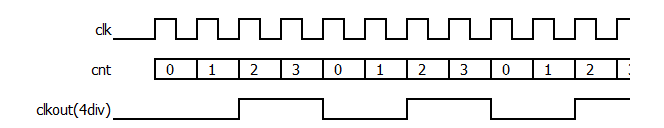

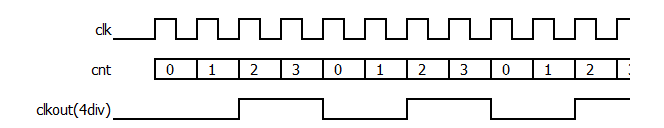

前言: 偶数分频容易得到:N倍偶数分频,可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去

2020-12-28 15:49:20 2620

2620 假设时钟分频是N,则设置一个计数器,计数长度是N(即从0计数到N-1),然后在计数器为计数到(N-1)/2的时候,翻转一下分频时钟信号。

2020-11-06 13:59:47 9658

9658

分频就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。

2024-03-06 17:13:32 384

384

时钟分频电路实现精讲

2013-04-18 12:07:20

时钟分频电路精讲

2013-07-11 09:37:52

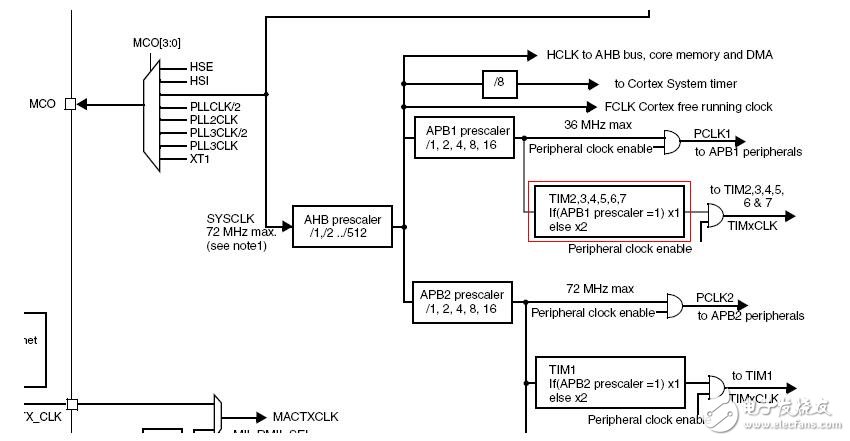

RCC : reset clock control 复位和时钟控制器。 设置系统时钟 SYSCLK、设置 AHB 分频因子(决定 HCLK 等于多少) 、 设置 APB2 分频因子(决定 PCLK2

2021-08-09 07:40:52

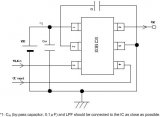

AD转换器中的时钟有什么作用呢?在网上找了很多答案,说了一大堆都没有说到点子上,就是说单纯这个时钟的作用是什么呢?我在原理图中使用过AD7988,上面写着在SCLK的上升沿捕捉数据,在下降沿读取数据。但是说,就单纯的讲这个时钟有什么作用呢?麻烦路过的各位大佬帮忙解答一下,谢谢!!!

2019-10-17 17:16:09

如何配置模块的时钟分频?

2024-02-05 06:01:59

在查阅CPLD设计的相关资料的时候,看到有文章说过当时钟晶振超过20M的时候,最好采用流水线操作现在我用的EPM240T100C5才用的是50M的晶振那么我可不可以将时钟先分频,然后将分频后的时钟

2013-04-25 09:39:35

学习高手的FPGA编程程序,发现他写的程序怎么这么冗余呢?怀着疑问,直到第二次阅读另一高手的FPGA程序,才开始怀疑是自己错了,原来使用时钟使能而不直接使用分频时钟是原因的。查阅相关资料整理了一下

2018-08-08 11:13:26

目录1. RCC 作用概述2. RCC框图剖析—时钟树3. 编程要点4. 源码实例1. RCC 作用概述RCC :reset clock control 复位和时钟控制器。设置系统时钟SYSCLK

2022-02-11 06:11:32

控制器。1. RCC 主要作用——时钟部分设置系统时钟 SYSCLK、设置 AHB 分频因子(决定 HCLK 等于多少) 、 设置 APB2 分频因子(决定 PCLK2 等于多少)、设置 APB1 分频因子(决定 PCLK1 等于多少)、设置各个外设的分频因子;控制 AHB、 APB2 和 APB1

2021-08-06 09:03:46

1、RCC主要作用–时钟部分设置系统时钟SYSCLK、设置AHB分频因子(决定HCLK等于多少)、设置APB2分频因子(决定PCLK2等于多少)、设置APB1分频因子(决定PCLK1等于多少)、设置

2021-08-06 09:28:53

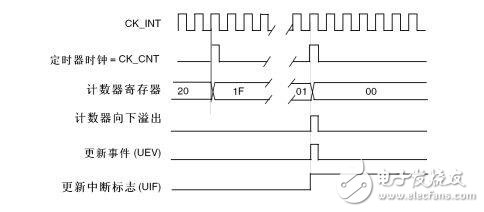

的预分频器,如果可以配置一个定时器Timer1而作为另一个定时器Timer2的预分频处理二、计数模式向下计数模式(时钟分频因子=1)向上计数模式(时钟分频因子=1)中央对其计数模式(时钟分频因子=1ARR=6)三、定时器常用寄存器和库函数定时器参数初始化:voi

2021-08-18 08:24:42

1、分类: 分为系统时钟,外设时钟。 固件库完成系统时钟的配置,外设时钟由分频因子决定。2、系统时钟的配置:下图来自STM32F103中文参考手册。(1)HSE:高速外部时钟 来自晶振,(4-16M

2021-08-12 06:39:06

1)外部时钟HSE:通常的配置是: HSE=8M, PLL 的倍频因子为: 9,系统时钟就设置成:SYSCLK = 8M * 9 = 72M。而改为内部时钟HSI:HSI=8M,分频因子2,即为4M

2021-08-11 07:34:33

程序控制的,是由硬件根据前一级的APB预分频器的输出自动选择,当APB预分频器的分频因子为1时,这个乘法器无作用;

2021-08-10 07:39:13

因子,取值2~63 * n: VCO输出时钟 倍频因子,取值192~432 * p: PLLCLK时钟分频因子,取值2,4,6,8 * q: OTG FS,SDIO,RNG时钟分频因子,取值4~15 * 函数调用举例,使用HSI设置时钟 * SYSCLK=HCLK=168...

2021-08-10 07:35:20

RCC:reset clock control 复位和时钟控制器。我们用的比较多的是时钟控制器。一、RCC的主要作用是时钟部分设置系统时钟 SYSCLK、设置 AHB 分频因子(决定 HCLK 等于

2021-12-09 08:02:37

时钟主要有三个作用,一是为Cotex-M3内核提供运行时钟,二是直接或经过分频后为挂载在各种总线上的外设提供时钟,第三则是以后为RTC(实时时钟)提供时钟源。下面是对应序号的时钟解释:...

2021-08-13 06:53:25

锁相环PLL,具有倍频作用,在这里我们可以输入倍频因子PLLMUL,要是想超频,就得在这个寄存器上做手脚啦。经过PLL的时钟称为PLLCLK。倍频因子我们设定为9倍频,也就是说,经过PLL之后,我们

2013-10-07 16:00:44

,提供给挂载在APB1总线上的外设。PCLK2:外设时钟,由APB2预分频器输出得到,最大频率可为72MHz,提供给挂载在APB2总线上的外设。为什么STM32的时钟系统如此复杂,有倍频、分频及一系列

2014-11-15 19:19:16

目录STMF4时钟系统重点概要HSE作为系统时钟配置方法(附带程序)正点开发板晶振问题(不同频率晶振配置方法)STM F407时钟系统概要时钟框图设置系统时钟SYSCLK、设置AHB 分频因子(决定

2022-02-28 07:40:21

和adi_sport_ConfigFrameSync中的分频系数是多少?

2. adi_sport_ConfigClock这里的时钟分频系数和pcg clk的分频系数有什么关联,比如1中的时钟是由内部pcg生成的,pcg该如何配置,sport是否需要配置?

2023-11-28 07:27:37

pllxtpre是predive1分频因子的l***位,xt是哪个英文单词的缩写

2016-06-02 13:33:21

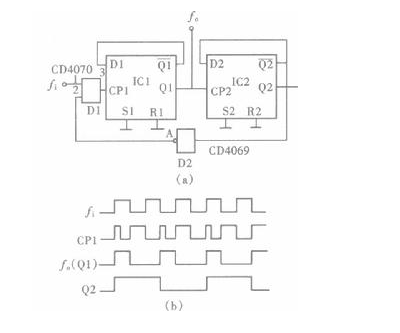

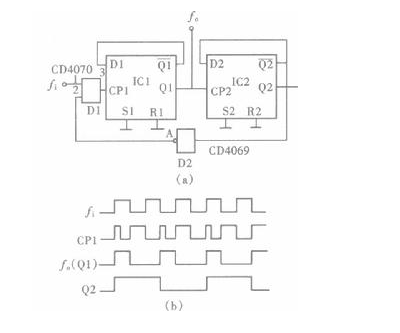

在FPGA的设计中一直都担任着很重要的角色,而说到分频,我相信很多人都已经想到了利用计数器计数来得到想要的时钟频率,但问题是仅仅利用计数器来分频,只可以实现偶数分频,而如果需要三分频、五分频、七分频

2019-12-11 10:15:33

实时时钟 (RTC) 是一个独立的 BCD 定时器/计数器,提供具有可编程闹钟中断功能的日历时钟/日历,可用于管理所有低功耗模式的自动唤醒单元。在配置RTC时钟时预分频器是关键指标,通过配置预分频

2021-08-13 09:10:46

《预分频系数为36000-1,这样计数器时钟为72MHz/36000 = 2kHz/》以上的一段话中的预分频系数36000-1和AHP预分频,分频因子有9中选择且分别为

2018-04-23 21:05:34

哪位高手能给讲一下预分频的作用或者有资料的分享一下先行谢过

2012-02-10 22:42:08

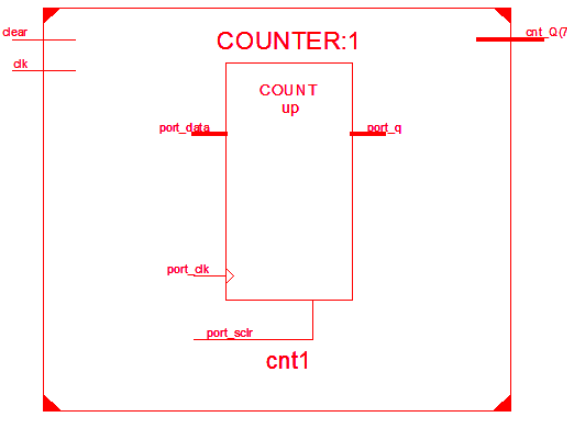

,越来越多的IP集成到片上系统,因此,设计中在不同层级实施了许多可支持多个分频因子的时钟分频器。本文中,我们介绍了一款节能设计,即用带有门控时钟的多级可编程约翰逊计数器系统来取代多个时钟分频器,该计数器

2018-09-30 16:00:50

截取的RTC内部框图,从图中我们可以看到,RTCCLK经过20位分频器RTC_DIV分频后得到日历的1Hz时钟,所以我们只需要配置RTC_DIV就行了,分频公式为RTC_CLK/(RTC_DIV+1

2021-08-29 21:36:46

定时器时钟分频因子和预分频系数区别1、定时器时钟分频因子ClockDivision是决定数字滤波器采样频率的参数。之后在使用输入捕获滤波器时这些参数会被用到,可以根据硬件情况配置滤波。2、预分频系数

2021-08-09 07:37:47

是否有评估板的外部(FPGA外部)时钟分频器而不是使用DCM或PLL?问候,半

2020-03-16 09:11:44

有关VHDL分频的问题,最终输出不对,程序什么的都有,程序的作用是对时钟先进行10分频,再进行20分频,最终级联实现200分频,程序如附件

2016-10-27 12:56:08

独立看门狗的时钟源为40k,分频因子最大为256//初始化独立看门狗5秒钟//prer:分频数:0~7(只有低3位有效!)//分频因子=4*2^prer.但最大值只能是256!//rlr:重装

2021-07-30 08:05:30

(PLL)/振荡器时钟,或任何系统时钟中产生分频时钟,并将不同的分频时钟馈送到不同的器件模块。由于时钟也可以被应用驱动,时钟分频器必须是可配置的。需要可配置性的原因有很多,包括:* 以较低的频率运行

2012-12-11 14:43:20

请给位共同讨论DSP2812中死区控制单元的时钟分频是指对CPU时钟还是高速外设时钟分频?看到论坛里说的很乱,大家讨论一个正确的结果。

2018-08-19 06:31:35

我想对2GHz的正弦波(相位噪声很低)进行16分频,分频出来的125M信号输入给FPGA,想选用ADi的分频器实现分频功能,我有以下几个问题:1.我查了ADi的分频器,分为(1)时钟分频器,(2

2019-01-11 13:39:43

ATtiny13系统时钟可通过设置时钟预分频寄存器CLKPR来分频

2020-11-11 07:03:03

如题 正在学习AD9361的讲座 关于插值因子的定义与其具有作用,是否可以展开形象地解释一下呢?谢谢。

2018-12-05 09:08:40

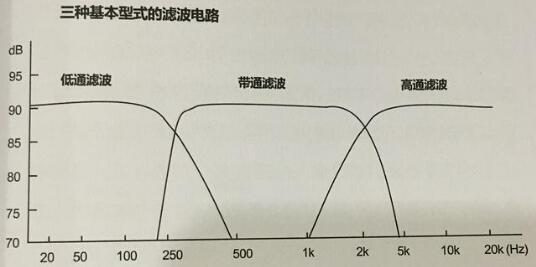

分频器的使用问题音响技术分频器是一种可以将声音信号分成若干个频段的音响设备。我们知道,声音的频率范围是在20Hz—20kHz之间,祈望仅使用一只扬声器就能够保证放送、20Hz—20kHz这样宽频

2019-11-01 09:10:30

分频器的作用: 在一个扬声器系统里,人们把箱体、分频电路、扬声器单元称为扬声器系统的三大件,而分频电路对扬声器系统能否高质量地还原电声信号起着极其重

2006-04-19 16:51:29 10543

10543

供数字时钟使用的+5000分频器电路

2009-01-13 20:07:47 1089

1089

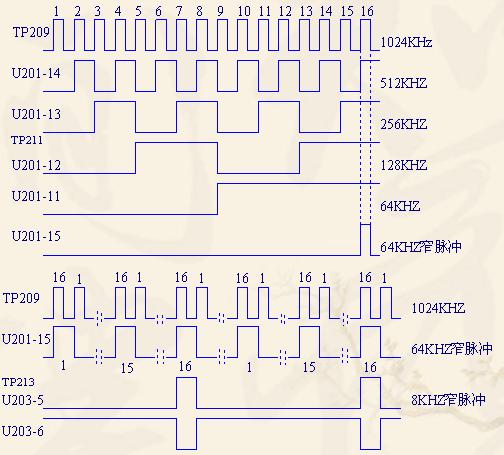

摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

2009-06-20 12:41:04 1238

1238

时钟分频及定时变换电路

2009-10-11 10:35:51 2033

2033

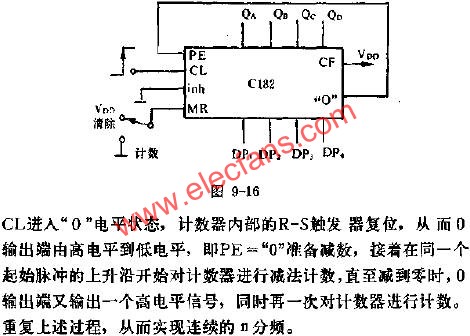

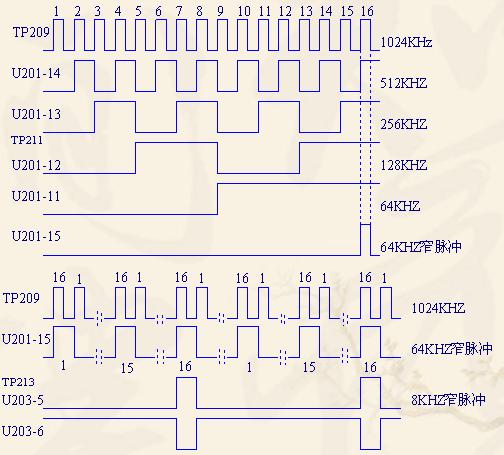

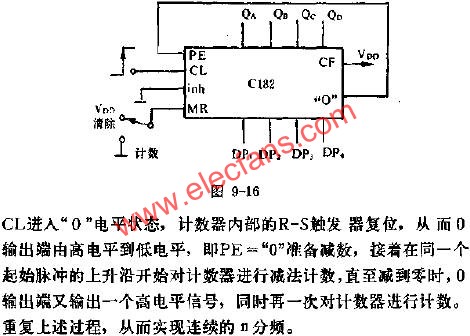

图中所示是用C182进行一级N分频的应用线路.0输出端接到PE端,CF端接高电平,INH接低电平,当计数器在时钟脉冲作用

2010-10-19 15:39:39 1527

1527

分频器的作用: 在一个扬声器系统里,人们把箱体、分频电路、扬声器单元称为扬声器系统的三大件,而分频电路对扬声器系统能否高质量地还原电声信号起着极其重要的作

2010-10-27 11:56:46 22151

22151 时钟是SOC或块级设计最重要的组成部分之一,本文阐述了目前SOC中各种可配置时钟分频器逻辑的实施方案,强调了各自的问题、优势及局限性。

2013-01-09 10:12:48 2890

2890

用 Verilog实现基于FPGA 的通用分频器的设计时钟分频包括奇数和偶数分频

2016-07-14 11:32:47 45

45 本文中,我们介绍了一款节能设计,即用带有门控时钟的多级可编程约翰逊计数器系统来取代多个时钟分频器,该计数器可提供8至任何偶数值(在本文中为38)的时钟分频因子。下面,我们将探讨实施细节和该技术的优劣。

2017-09-15 15:40:12 10

10 STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

2017-11-30 09:14:18 6833

6833

标出;图中间的时钟监视系统(CSS)是在很多ST7的单片机中就出现的安全设置。 特别注意 :图的右边,输出定时器时钟之前有一个乘法器,它的操作不是由程序控制的,是由硬件根据前一级的APB预分频器的输出自动选择,当APB预分频器的分频因子为1时,这个乘法器无作用;当

2017-12-04 17:00:21 549

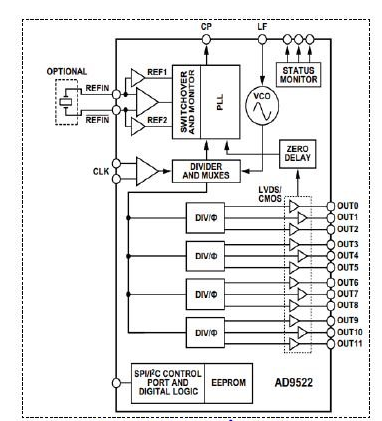

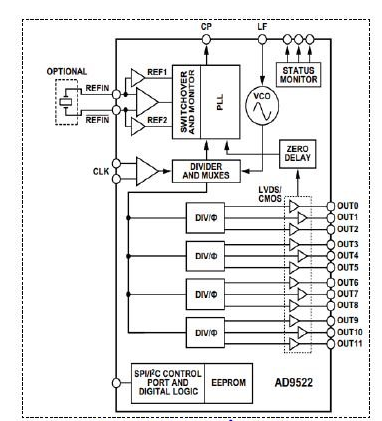

549 在集成度高度发展的今天,不能靠多个晶振源来解决问题,而且一旦晶振固定那么它的灵活性和可移植性必然受到很大影响,所以一些时钟分频芯片应运而生,今天我们将举一个很有代表性的AD9522时钟分频芯片的典型应用来达到一个抛砖引玉的作用。

2018-03-16 16:31:00 11548

11548

本文开始介绍了音箱分频器工作原理,其次介绍了音箱分频器电路及电路的维修方法,最后介绍了音箱分频器中电容电阻电感线圈的作用以及音箱分频器用电感线圈的要求。

2018-04-13 09:15:05 63102

63102 本文首先介绍了分频器的种类及原理,其次详细阐述了分频器的斜率是什么以及斜率有着什么重要作用,具体的跟随小编一起来了解一下。

2018-05-28 11:35:21 29824

29824

本文主要介绍的是汽车音响的分频器,首先介绍了汽车音响的分频器的种类,其次介绍了分频器的作用及分频点的选择,最后分析了汽车音响分频器安装位置,具体的跟随小编一起来了解一下。

2018-05-28 11:54:38 12975

12975 输入端分频因子(M)可从1~2047的分频范围内进行选择;输出端分频因子(N)可从1~4095的分频范围内进行选择。输出频率在1MHz~100MHz的范围内,输入时钟为8kHz~36MHz的标准时钟。在内部可进行微调,在少量外置部件的条件下动作。

2018-08-15 11:16:30 6671

6671

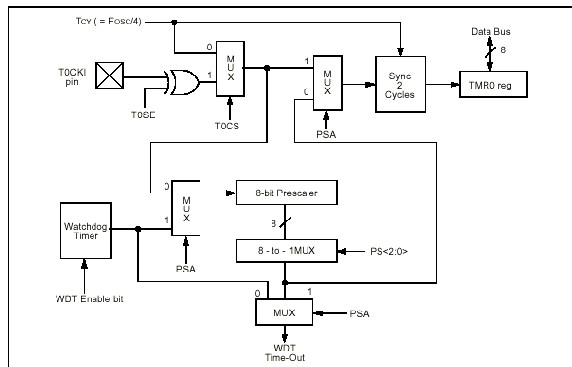

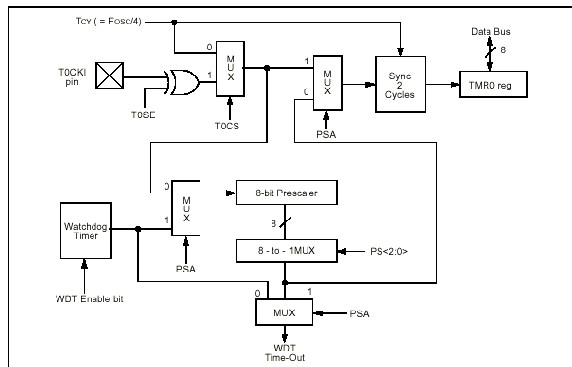

1、从RTCC到WDT的改变 MOVLW B‘XX0X0XXX’ ;选择内部时钟和新的预分频值

OPTION ;如果新的预分频值=“000”或者

CLRF RTCC ;=“001

2018-11-08 16:14:03 9285

9285

分频器主要分为偶数分频、奇数分频、半整数分频和小数分频,如果在设计过程中采用参数化设计,就可以随时改变参量以得到不同的分频需要。

2019-02-01 01:28:00 15719

15719

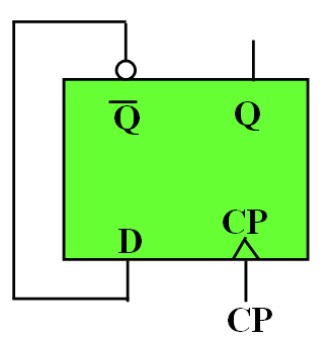

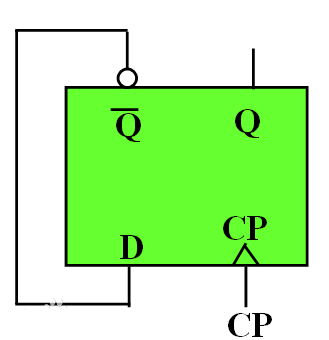

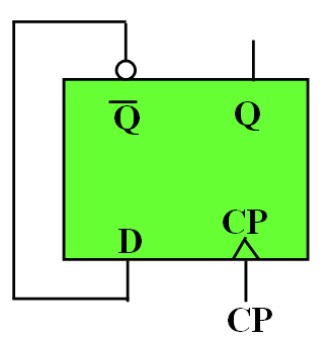

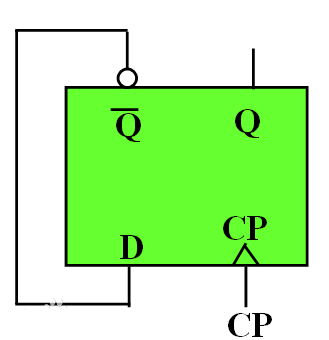

分频就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。而二分频就是通过有分频作用的电路结构,在时钟每触发2个周期时,电路输出1个周期信号。

2019-10-08 09:05:00 22246

22246

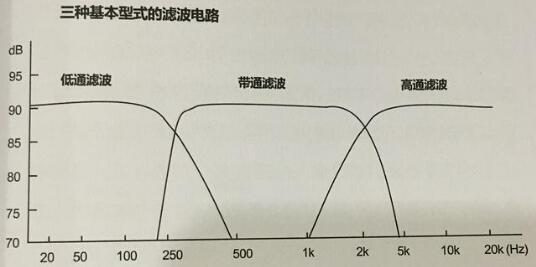

分频点指分频器高通、带通和低通滤波器之间的分界点,常用频率来表示,单位为赫兹。分频点应根据各频段扬声器单元或音箱的频率特性和功率分配来具体确定。

2019-10-08 10:30:47 33851

33851

分频器的功能则相当于音箱中的“大脑”,分频器对音质的好坏起到了至关重要的作用。使用分频器可以将高频信号送到高音扬声器中,低频信号送到低音扬声器中,使高、低频信号各行其道,尽可能的发挥各自扬声器的工作

2019-12-02 08:47:27 18922

18922 对于分频系数为 10 的分频器, 本例的输入时钟系统 50M 时钟(clk_50M), 输出为十分频时钟(f_50) 。设计方法为,通过设置一个 3 位的计数寄存器(cnt)来实现,每个时钟周期的上升沿计数一次, 当计数寄存器数到 4 的时候, 将输出分频信号取反即可得到 10 分频的输出。

2020-10-28 08:00:00 1

1 电子发烧友网站提供《NB7V33MMNGEVB 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:06:41 5

5 电子发烧友网站提供《NB7L32MMNEVB 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:21:59 2

2 电子发烧友网站提供《SY89876L 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:22:31 10

10 电子发烧友网站提供《SY89873L 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:23:10 5

5 电子发烧友网站提供《NB6L239MNEVB/D 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:23:51 13

13 电子发烧友网站提供《SY89872U 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:24:21 1

1 电子发烧友网站提供《SY89871U 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:25:53 6

6 电子发烧友网站提供《SY89875U 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:27:06 4

4 时钟分配器是将输入时钟脉冲经过一定的分频后分别送到各路输出的逻辑电路。

2021-03-02 17:34:58 8497

8497 程序实现对输入时钟信号的7分频介绍。

2021-03-17 14:59:23 11

11 电子发烧友网为你提供理解STM32系统时钟和分频资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-20 08:43:42 11

11 RCC:reset clock control 复位和时钟控制器。我们用的比较多的是时钟控制器。一、RCC的主要作用是时钟部分设置系统时钟 SYSCLK、设置 AHB 分频因子(决定 HCLK 等于

2021-11-25 20:36:06 16

16 目录1. RCC 作用概述2. RCC框图剖析—时钟树3. 编程要点4. 源码实例1. RCC 作用概述RCC :reset clock control 复位和时钟控制器。设置系统时钟SYSCLK

2021-12-08 12:36:07 9

9 分频因子,取值2~63 * n: VCO输出时钟 倍频因子,取值192~432 * p: PLLCLK时钟分频因子 ,取值2,4,6,8 * q: OTG FS,SDIO,RNG时钟分频因子,取值4~15 * 函数调用举例,使用HSI设置时钟 * SYSCLK=HCLK=168

2022-01-12 18:45:37 1

1 目录STMF4时钟系统重点概要HSE作为系统时钟配置方法(附带程序)正点开发板晶振问题(不同频率晶振配置方法)STM F407时钟系统概要时钟框图设置系统时钟SYSCLK、设置AHB 分频因子(决定

2022-01-14 15:59:03 1

1 一、RCC是什么?

RCC: Reset Clock Control,时钟和复位控制器

二、RCC的主要作用

1、设置系统时钟SYSCLK

2、设置AHB分频因子(决定HCLK等于

2022-02-11 15:38:08 5

5 分频器又称为分频网络。分频器的主要作用就是在音频系统中把全频带音频信号分为不同的频段后送到对应的工作频率的扬声器,使它们得到合适频带的激励信号,再进行重放。例如,在二分频的音箱中,通过高通滤波器分类出较高的频率供给高音扬声器,通过低通滤波器分离出较低的频率供给低音扬声器。

2022-04-12 15:24:50 6163

6163 有关小数分频的资料,用于时钟芯片设计,十分经典。

2022-10-24 11:48:44 0

0 时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频始终和源时钟同相

2023-01-05 14:00:07 949

949 小白初学模拟电路时常会遇到音箱实践,而分频器作为音箱的电路装置,也是小白甚至工程师有了解的电子设备之一,但你们知道它的作用和安装方法吗?今天这篇文将分享分频器的作用及安装方法,希望对小伙伴有所帮助。

2023-03-15 17:18:21 5734

5734 时钟分频电路(分频器)在IC设计中经常会用到,其目的是产生不同频率的时钟,满足系统的需要。 比如一个系统,常规操作都是在1GHz时钟下完成,突然要执行一个操作涉及到模拟电路,所需时间是us量级的,显然用1GHz(周期是1ns)的时钟进行操作是不合适的。

2023-04-25 14:46:25 5332

5332

上一篇文章时钟分频系列——偶数分频/奇数分频/分数分频,IC君介绍了各种分频器的设计原理,其中分数分频器较为复杂,这一篇文章IC君再跟大家聊聊分数分频的具体设计实现。

2023-04-25 14:47:44 1028

1028

基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 0

0 为什么单片机内置时钟源不经过pll也可以分频? 单片机内置时钟源不经过PLL也可以实现分频,原因在于单片机内置时钟源自带分频器,可以通过软件设置分频系数来控制内部时钟频率。 在单片机内部,通常会

2023-09-02 15:12:45 597

597 什么是时钟芯片?时钟芯片的工作原理 时钟芯片的作用 时钟芯片是一种用于计算机或其他电子设备中的集成电路,它提供精准的时钟信号。时钟信号是计算机进行各种操作的基础,比如数据传输、运算等等,所以时钟芯片

2023-10-25 15:02:33 2314

2314 分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频 / 倍频,目的

2023-11-03 15:55:02 471

471

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

2023-12-14 15:28:56 257

257

锁相环整数分频和小数分频的区别是什么? 锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种技术。在PLL中,分频器模块起到关键作用,可以实现整数分频

2024-01-31 15:24:48 312

312 分频器是一种电子设备,用于将输入信号分成不同频率的输出信号。其主要作用是将原始输入信号分离成多个频率范围内的信号,以供不同的电路进行处理。分频器广泛应用于通信、测量和音频系统中。 分频器的主要

2024-02-01 11:19:51 461

461

电子发烧友App

电子发烧友App

评论