本文主要带领大家来了解一下分频器的计算和调整,首先来了解一下分频器原理及是分频点,其次详细了解分频器计算的顺序以及调整方法。

2018-05-29 09:59:00 120326

120326

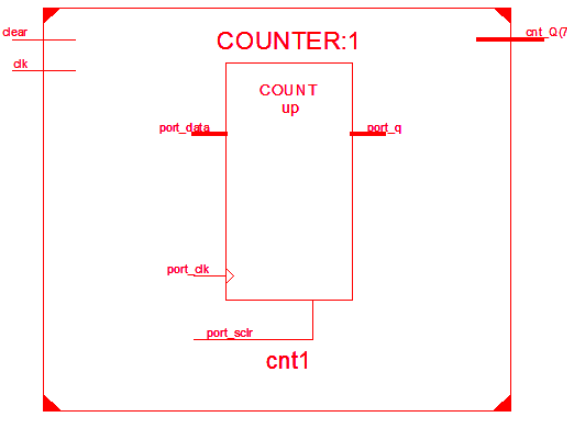

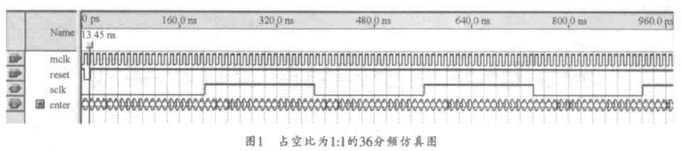

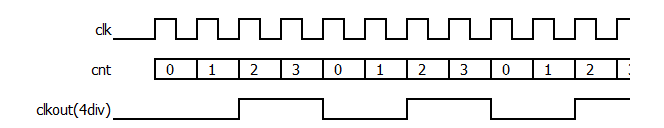

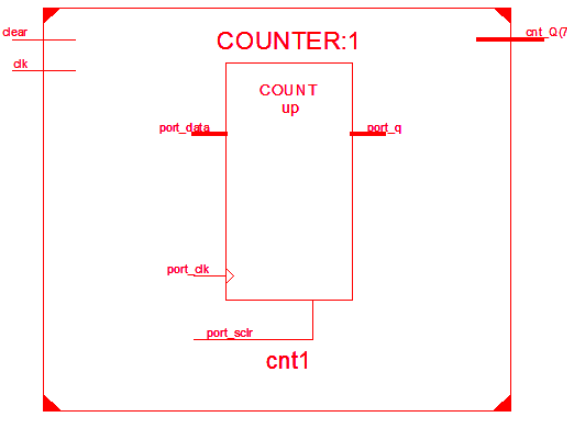

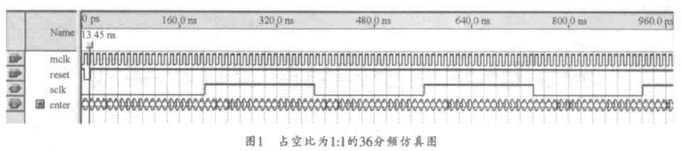

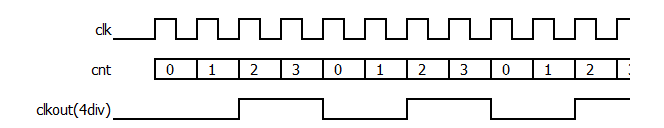

前言: 偶数分频容易得到:N倍偶数分频,可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去

2020-12-28 15:49:20 2620

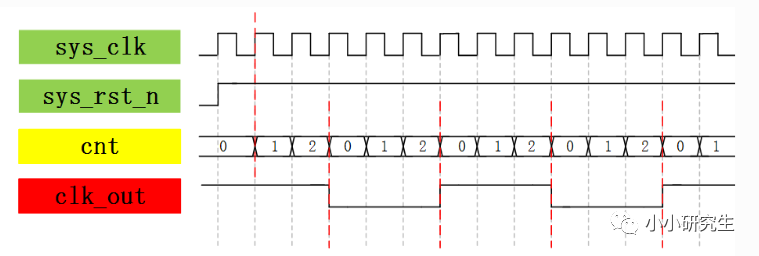

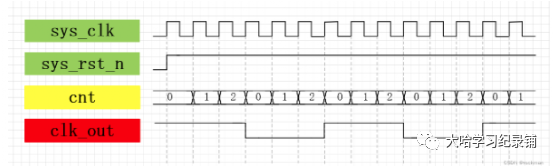

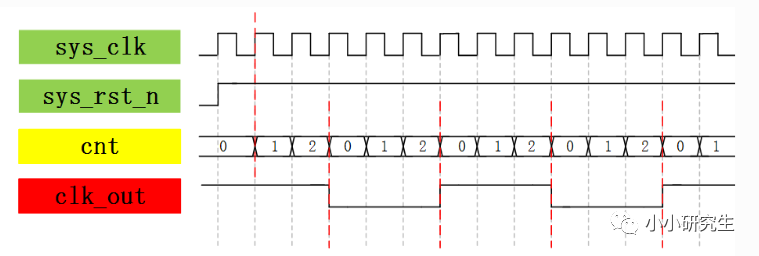

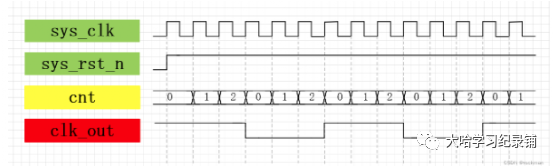

2620 假设时钟分频是N,则设置一个计数器,计数长度是N(即从0计数到N-1),然后在计数器为计数到(N-1)/2的时候,翻转一下分频时钟信号。

2020-11-06 13:59:47 9658

9658

分频就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。

2024-03-06 17:13:32 384

384

时钟分频电路实现精讲

2013-04-18 12:07:20

时钟分频电路精讲

2013-07-11 09:37:52

时钟树寄存器配置详解

2021-08-12 06:06:13

详解STM32的时钟系统STM32的时钟树时钟信号推动单片机内各个部分执行相应的指令,时钟就像人的心跳一样。 STM32本身十分复杂,外设非常多,任何外设都需要时钟才能启动,但并不是所有的外设都需要

2021-08-19 06:33:34

如何配置模块的时钟分频?

2024-02-05 06:01:59

CC3200 工作在定时器捕获模式下,如何进行定时器时钟分频。

当我运行SDK中 timer_cc例程时加入

MAP_TimerPrescaleSet(TIMERA2_BASE,TIMER_A,80);//需要1M Hz时钟

捕获的数据始终是80 MHz时钟的数据。

2018-06-23 07:06:54

在查阅CPLD设计的相关资料的时候,看到有文章说过当时钟晶振超过20M的时候,最好采用流水线操作现在我用的EPM240T100C5才用的是50M的晶振那么我可不可以将时钟先分频,然后将分频后的时钟

2013-04-25 09:39:35

clk_out_div6;//6分频时钟输出;reg [1:0] cnt;//计数寄存器regclk_out_div6;//时钟输出寄存器 always@(posedge clk or negedge rest_n)beginif(!rest_n) //复位信号 begincnt

2016-03-30 11:35:51

学习高手的FPGA编程程序,发现他写的程序怎么这么冗余呢?怀着疑问,直到第二次阅读另一高手的FPGA程序,才开始怀疑是自己错了,原来使用时钟使能而不直接使用分频时钟是原因的。查阅相关资料整理了一下

2018-08-08 11:13:26

BCSCTL2设置,第三位置1,选择XT2CLK作为SMCLK时钟,将第二位和第一位置1,使分频比为8TACTL = 0x01D3;//定时器A控制寄存器设置,第二位置1:清除;第4、5位置1、0

2015-05-20 17:35:21

STM32时钟分频系数的知识点汇总,绝对实用

2021-12-15 07:01:54

的时钟源,系统时钟可选择为PLL输出、HSI或者HSE。系统时钟的做大频率为72MHz,它通过AHB分频器分频后送给个模块使用,AHB分频器可选择1、2、4、8、16、32、64、128、256、512

2018-07-19 03:40:25

PLL(锁相环电路):负责时钟倍频功能时钟通道与流向、分频完全独立的多个时钟:STM32含有多个相互独立的时钟。时钟框图详解总体配置2套独立时钟:HSx和LSx纯内部:HSI、LSI内外部:HSE、LSE纯外部:OSC_IN、OSC32_INPLL2个可选PLL源(PLLSRC控制)倍频可

2021-08-19 07:46:14

STM32时钟树案例详解时钟树直接使用HSI作为时钟源使用配置相应的结构体,最后调用HAL_RCC_OscConfig(), 和HAL_RCC_ClockConfig()初始化时钟

2021-08-20 06:11:55

原文地址:STM32的时钟树深入详解作者:蔡志威在STM32上如果不使用外部晶振,OSC_IN和OSC_OUT的接法如果使用内部RC振荡器而不使用外部晶振,请按照下面方法处理:1)对于100脚或

2021-08-23 07:38:32

和adi_sport_ConfigFrameSync中的分频系数是多少?

2. adi_sport_ConfigClock这里的时钟分频系数和pcg clk的分频系数有什么关联,比如1中的时钟是由内部pcg生成的,pcg该如何配置,sport是否需要配置?

2023-11-28 07:27:37

今天做了下十进制加法计数器,用DE2做的,可是不会添加50M内部时钟分频模块,将分频后的1秒时钟作为计数时钟,在这请教下各位前辈。代码如下:LIBRARY IEEEUSE

2013-05-16 19:59:24

在FPGA的设计中一直都担任着很重要的角色,而说到分频,我相信很多人都已经想到了利用计数器计数来得到想要的时钟频率,但问题是仅仅利用计数器来分频,只可以实现偶数分频,而如果需要三分频、五分频、七分频

2019-12-11 10:15:33

实时时钟 (RTC) 是一个独立的 BCD 定时器/计数器,提供具有可编程闹钟中断功能的日历时钟/日历,可用于管理所有低功耗模式的自动唤醒单元。在配置RTC时钟时预分频器是关键指标,通过配置预分频

2021-08-13 09:10:46

截取的RTC内部框图,从图中我们可以看到,RTCCLK经过20位分频器RTC_DIV分频后得到日历的1Hz时钟,所以我们只需要配置RTC_DIV就行了,分频公式为RTC_CLK/(RTC_DIV+1

2021-08-29 21:36:46

定时器时钟分频因子和预分频系数区别1、定时器时钟分频因子ClockDivision是决定数字滤波器采样频率的参数。之后在使用输入捕获滤波器时这些参数会被用到,可以根据硬件情况配置滤波。2、预分频系数

2021-08-09 07:37:47

嗨,大家好 .......我正在寻找描述.......... GTS,GSR&时钟分频复位你能帮帮我吗以上来自于谷歌翻译以下为原文 hi guys ....... i'm looking

2019-01-09 10:42:15

基于特定的开发板上的时钟策略:倍频/分频系数需要在使能 PLL 之前进行配置,所以需要在 Open PLL 之前将所有系统的时钟分频器系数以及PLL的倍频系数配置好。整个时钟的配置流程如下所示:(1

2021-08-23 09:12:44

RTC时钟要求提供1HZ的时钟,HSE配置为RTC时钟源, 主要配置系统时钟, 使能HSE。然后设置好HSE分频、RTC_PRER分频寄存器的值。计算如下: STM32F7xx的可编程预分

2022-05-13 15:19:08

模块,如内核、闪存、存储器和外设,这些模块需要在不同频率下运行。它们的最大运行速率可能受到所使用的实现技术、实施架构、功率目标、以及IP访问时间等因素的限制。时钟分频器电路是必不可少的,它可以从主锁相环

2012-12-11 14:43:20

【STM32】系统时钟RCC详解(超详细,超全面)1什么是时钟时钟是单片机运行的基础,时钟信号推动单片机内各个部分执行相应的指令。时钟系统就是CPU的脉搏,决定cpu速率,像人的心跳一样 只有有了

2021-08-12 06:40:46

请给位共同讨论DSP2812中死区控制单元的时钟分频是指对CPU时钟还是高速外设时钟分频?看到论坛里说的很乱,大家讨论一个正确的结果。

2018-08-19 06:31:35

ATtiny13系统时钟可通过设置时钟预分频寄存器CLKPR来分频

2020-11-11 07:03:03

(注:文中的x为数字)初始化1.TIMx的外设时钟使能RCC->APB1ENR |= 1 ARR = arr;3.设定预分频器的值在设定预分频器的值之前,先理解这里的预分频器与时钟系统里

2021-08-18 07:54:36

我知道的是,每个IP都可以编程来选择它的时钟源,预分频是什么意思?分频的目的又是什么呢?

2024-01-17 07:34:27

议程PLL介绍及小数分频锁相环的优点小数分频锁相环的错误使用小数分频锁相环详解参考杂散及如何减少杂散总结

2010-05-28 14:58:36 0

0

供数字时钟使用的+5000分频器电路

2009-01-13 20:07:47 1089

1089

具有奇次和偶次分频的分频器

2009-04-11 10:22:12 880

880

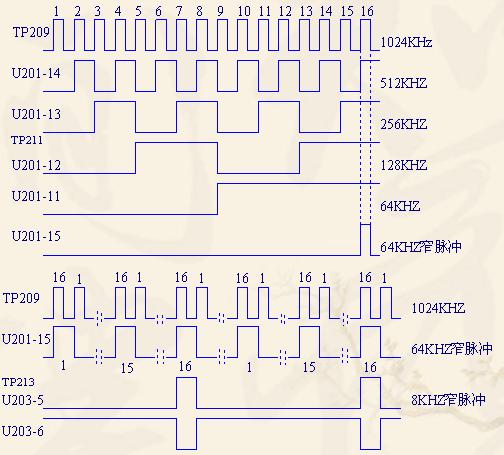

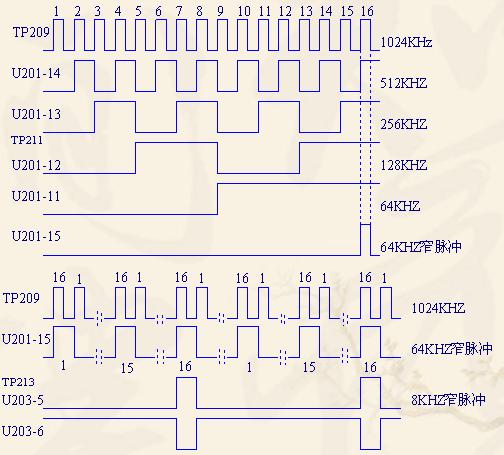

摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

2009-06-20 12:41:04 1238

1238

时钟分频及定时变换电路

2009-10-11 10:35:51 2033

2033

时钟是SOC或块级设计最重要的组成部分之一,本文阐述了目前SOC中各种可配置时钟分频器逻辑的实施方案,强调了各自的问题、优势及局限性。

2013-01-09 10:12:48 2890

2890

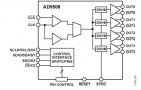

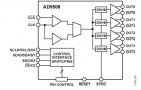

ADI最近发布了一款时钟缓冲器和分频器IC(集成电路)AD9508,该电路结合了高速、极低抖动(12 kHz至20 MHz频段为41 fs)及可选分频功能。

2013-02-21 11:31:00 4020

4020

用 Verilog实现基于FPGA 的通用分频器的设计时钟分频包括奇数和偶数分频

2016-07-14 11:32:47 45

45 分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如赛灵思(Xilinx)的DLL.来进行时钟的分频,倍频以及相移。

2017-02-11 12:33:40 10916

10916 分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如赛灵思(Xilinx)的DLL.来进行时钟的分频,倍频以及相移。

2017-02-11 13:36:36 12409

12409

基于MSP430功能模块详解系列之——系统时钟

2017-10-12 16:40:43 5

5 )或内部高速时钟HSI(high speed internal)或内部低速时钟LSI(low speed internal)提供。这里以内部高速时钟举例,内部高速时钟HSI经过HSIDIV分频,得到

2017-11-15 08:48:12 29503

29503

配置STM8外部时钟(寄存器)步骤:1.设置外部时钟寄存器CLK_ECKR是对其写0xB4。2.设置外部时钟分频,CLK_CKDIVR低三位是外部时钟分频系数设置。3.使能外部时钟向CLK_ECKR写0x01。

2017-11-15 09:05:11 19006

19006

单片机都是有时钟振荡器的。还有定时器,看门狗,程序计数器等等。如果看门狗或者定时器所要求的脉冲速度比较时钟脉冲慢,那么,就要利用分频器进行分频,以得到你所要求的脉冲速率。分频因子就是在定时器时钟进入

2017-11-15 10:07:22 18147

18147

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

2017-11-30 09:14:18 6833

6833

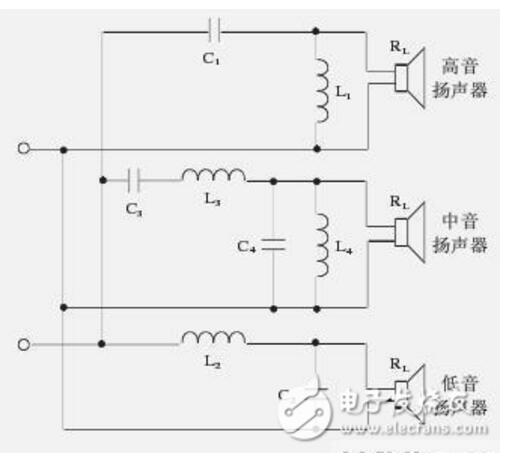

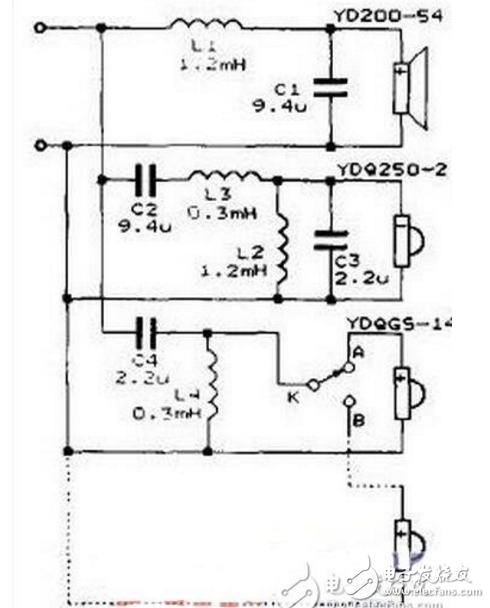

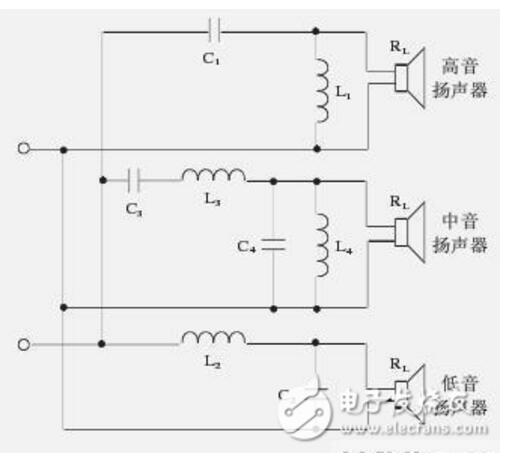

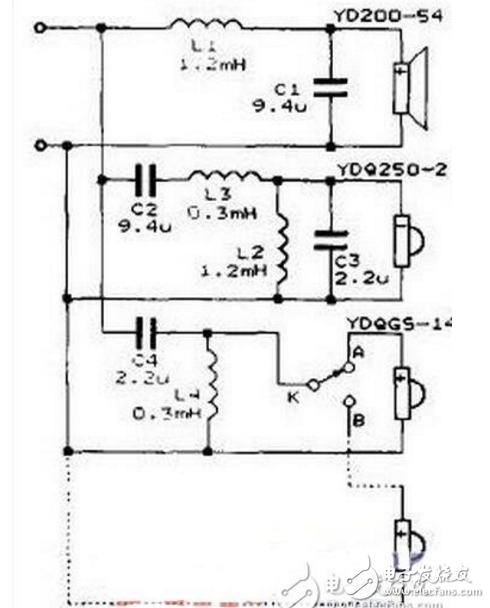

本文主要介绍了音响二分频器电路图(六款模拟电路设计原理图详解)。分频器就是一个由电容器和电感线圈构成的滤波网。高音通道只让高频信号经过而阻止低频信号;低音通道正好相反,只让低音经过而阻止高频

2018-02-01 10:08:01 246621

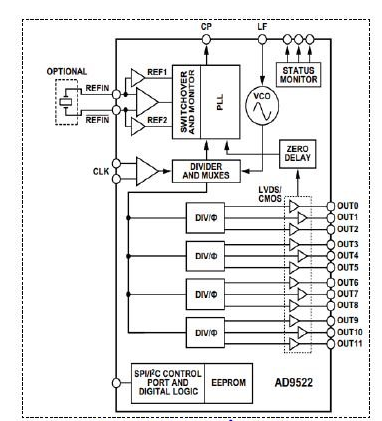

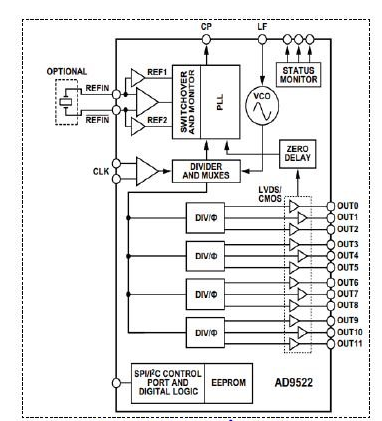

246621 在集成度高度发展的今天,不能靠多个晶振源来解决问题,而且一旦晶振固定那么它的灵活性和可移植性必然受到很大影响,所以一些时钟分频芯片应运而生,今天我们将举一个很有代表性的AD9522时钟分频芯片的典型应用来达到一个抛砖引玉的作用。

2018-03-16 16:31:00 11548

11548

本文主要介绍了电子分频器电路图大全(六款电子分频器电路设计原理图详解)。从工作原理看,分频器就是一个由电容器和电感线圈构成的滤波网。高音通道只让高频信号经过而阻止低频信号;低音通道正好相反,只让低音

2018-03-02 09:41:17 123621

123621

如输出到称为HCLK、FCLK的时钟,还直接输出到SDIO外设的SDIOCLK时钟、存储器控制器FSMC的FSMCCLK时钟,和作为APB1、APB2的预分频器的输入端。GPIO外设是挂载在APB2

2018-04-03 08:45:51 19520

19520

本文主要详解什么是激励器、分频器、均衡器、压缩限幅器,最后还介绍了均衡器与激励器的区别,具体的跟随小编一起来了解一下。

2018-05-28 15:10:19 4787

4787 本文主要详解音箱、扬声器、分频器、功放,首先介绍了音箱的组成、原理、分类及性能指标,其次介绍了扬声器的原理和使用方法,最后详细的阐述了分频器、功放的原理及作用,具体的跟随小编一起来了解一下。

2018-05-29 11:24:35 6767

6767 输入端分频因子(M)可从1~2047的分频范围内进行选择;输出端分频因子(N)可从1~4095的分频范围内进行选择。输出频率在1MHz~100MHz的范围内,输入时钟为8kHz~36MHz的标准时钟。在内部可进行微调,在少量外置部件的条件下动作。

2018-08-15 11:16:30 6671

6671

分频器是FPGA设计中使用频率非常高的基本单元之一。尽管目前在大部分设计中还广泛使用集成锁相环(如altera的PLL,Xilinx的DLL)来进行时钟的分频、倍频以及相移设计,但是,对于时钟要求

2019-08-07 08:00:00 9033

9033

偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2019-02-01 01:49:00 1029

1029

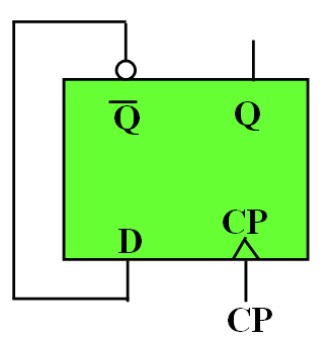

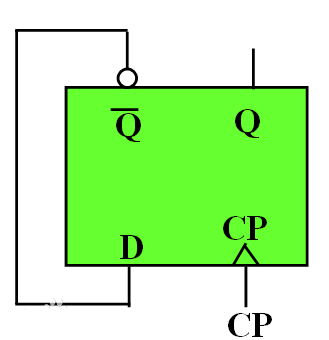

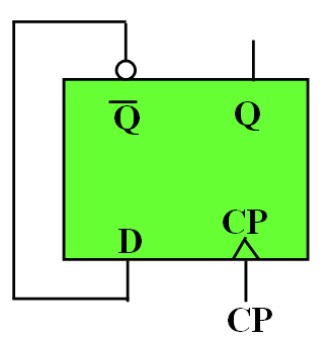

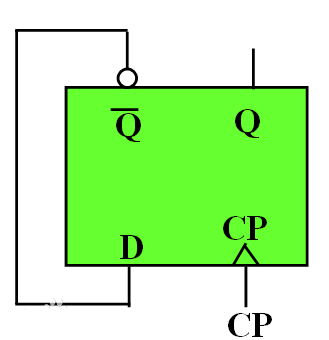

分频就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。而二分频就是通过有分频作用的电路结构,在时钟每触发2个周期时,电路输出1个周期信号。

2019-10-08 09:05:00 22246

22246

从分频方式看可以分为两种,一种是主动分频(PassiveCrossover),或者叫电子分频,也可以叫外置分频、有源分频;另一种是被动分频 (ActiveCrossover),或者叫功率分频,也可以叫内置分频、无源分频。

2019-10-08 10:37:42 11681

11681

通常情况下,时钟的分频在FPGA设计中占有重要的地位,在此就简单列出分频电路设计的思考思路。

2020-07-10 17:18:03 2192

2192 对于分频系数为 10 的分频器, 本例的输入时钟系统 50M 时钟(clk_50M), 输出为十分频时钟(f_50) 。设计方法为,通过设置一个 3 位的计数寄存器(cnt)来实现,每个时钟周期的上升沿计数一次, 当计数寄存器数到 4 的时候, 将输出分频信号取反即可得到 10 分频的输出。

2020-10-28 08:00:00 1

1 电子发烧友网站提供《NB7V33MMNGEVB 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:06:41 5

5 电子发烧友网站提供《NB7L32MMNEVB 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:21:59 2

2 电子发烧友网站提供《SY89876L 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:22:31 10

10 电子发烧友网站提供《SY89873L 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:23:10 5

5 电子发烧友网站提供《NB6L239MNEVB/D 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:23:51 13

13 电子发烧友网站提供《SY89872U 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:24:21 1

1 电子发烧友网站提供《SY89871U 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:25:53 6

6 电子发烧友网站提供《SY89875U 时钟分频器参考设计.pdf》资料免费下载

2020-12-31 05:27:06 4

4 程序实现对输入时钟信号的7分频介绍。

2021-03-17 14:59:23 11

11 AD9510:1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出

2021-03-21 15:32:58 11

11 AD9508:1.65 GHz时钟扇出缓冲器,集成输出分频器和延迟调整

2021-03-21 15:45:30 2

2 AD9515:1.6 GHz时钟分配IC、分频器、延迟调整、双输出数据表

2021-04-13 14:38:52 9

9 电子发烧友网为你提供理解STM32系统时钟和分频资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-20 08:43:42 11

11 LTC6954:低相位噪声、三输出时钟分布分频器/驱动器数据表

2021-05-19 13:19:44 4

4 AD9515 1.6 GHz时钟分配IC,分频器,延迟调整,双输出数据表

2021-06-16 17:13:16 12

12 最小系统1,、供电电路2、复位电路3、时钟:外部晶振(2个)4、Boot启动模式选择5、下载电路(JTAG)6、后背电池时钟详解:在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE

2021-11-17 15:36:02 12

12 DCO频率配置 MCLK,SMCLK时钟源选择,分频配置 时钟信号选择

2021-11-25 09:36:04 40

40 【STM32】系统时钟RCC详解(超详细,超全面) 原创 ...

2021-11-30 12:21:07 13

13 一、RCC是什么?

RCC: Reset Clock Control,时钟和复位控制器

二、RCC的主要作用

1、设置系统时钟SYSCLK

2、设置AHB分频因子(决定HCLK等于

2022-02-11 15:38:08 5

5 有关小数分频的资料,用于时钟芯片设计,十分经典。

2022-10-24 11:48:44 0

0 偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2022-11-21 09:41:24 751

751 时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频始终和源时钟同相

2023-01-05 14:00:07 949

949 初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整数分频以及小数分频进行简单的总结。

2023-03-29 11:38:40 3108

3108

时钟分频电路(分频器)在IC设计中经常会用到,其目的是产生不同频率的时钟,满足系统的需要。 比如一个系统,常规操作都是在1GHz时钟下完成,突然要执行一个操作涉及到模拟电路,所需时间是us量级的,显然用1GHz(周期是1ns)的时钟进行操作是不合适的。

2023-04-25 14:46:25 5332

5332

上一篇文章时钟分频系列——偶数分频/奇数分频/分数分频,IC君介绍了各种分频器的设计原理,其中分数分频器较为复杂,这一篇文章IC君再跟大家聊聊分数分频的具体设计实现。

2023-04-25 14:47:44 1028

1028

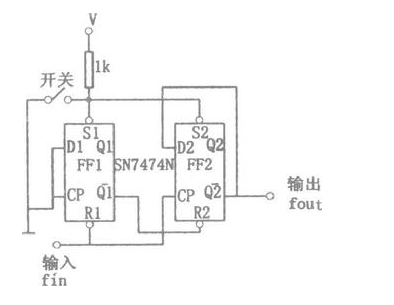

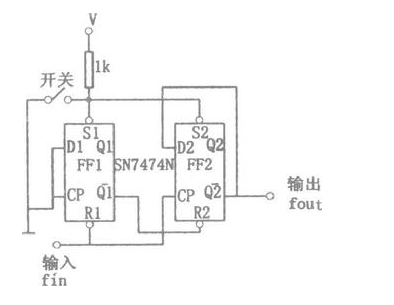

采用触发器反向输出端连接到输入端的方式,可构成简单的 2 分频电路。

2023-05-30 17:21:29 1189

1189

板载晶振提供的时钟信号频率是固定的,不一定满足需求,因此需要对基准时钟进行分频。要得到更慢的时钟频率可以 分频 ,要得到更快的时钟频率可以 倍频 。我们有两种方式可以改变频率,一种是 锁相环 (PLL,后面章节会讲解),另一种是用 Verilog代码描述。

2023-06-23 16:52:00 1149

1149

基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 0

0 为什么单片机内置时钟源不经过pll也可以分频? 单片机内置时钟源不经过PLL也可以实现分频,原因在于单片机内置时钟源自带分频器,可以通过软件设置分频系数来控制内部时钟频率。 在单片机内部,通常会

2023-09-02 15:12:45 597

597 时钟分频电路通过将输入的高频时钟信号分频,生成较低频率的时钟信号。它通常基于计数器和逻辑门实现,用于将高频时钟信号分解成系统所需的各种频率。

2023-09-14 14:53:57 4894

4894 通过一个标志信号作为偶6分频的工作时钟(可靠,常用)

2023-10-10 14:23:52 205

205

分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频 / 倍频,目的

2023-11-03 15:55:02 471

471

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

2023-12-14 15:28:56 257

257

锁相环整数分频和小数分频的区别是什么? 锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种技术。在PLL中,分频器模块起到关键作用,可以实现整数分频

2024-01-31 15:24:48 312

312

电子发烧友App

电子发烧友App

评论