在电源应用中,哪怕已经确定拓扑结构、频率和负载范围等需求,工程师短时间内也很难判断哪一种开关技术最好……“品质因数”(Figure of Merit, FoM),就是帮助电源设计人员直观衡量功率器件性能优劣的重要概念,特别是损耗描述方面,在挑选功率器件时可以发挥“神助攻”。

2023-11-28 11:47:36 2315

2315

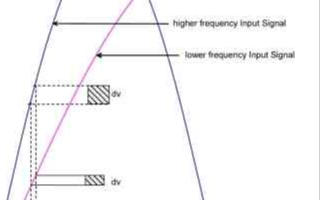

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

2012-04-01 10:19:38 1666

1666

本系列文章共有三部分,第 1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与 ADC 的孔径抖动组合。在第 2 部分中,该组合 抖动 将用于计算 ADC 的 SRN,然后将其与实际

2012-05-07 11:37:30 2668

2668

Analog Devices, Inc. (NASDAQ: ADI) 全球领先的高性能信号处理解决方案供应商,最近推出一款具有业界最低抖动特性的 RF 时钟 IC(射频时钟集成电路)AD9525

2012-11-02 10:16:53 1186

1186 -Si539x时钟提升频率灵活性和抖动性能--Si56x Ultra Series™ XO/VCXO提供最大可达3GHz的任意频率时钟-。

2018-06-26 15:19:41 7075

7075 时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 892

892

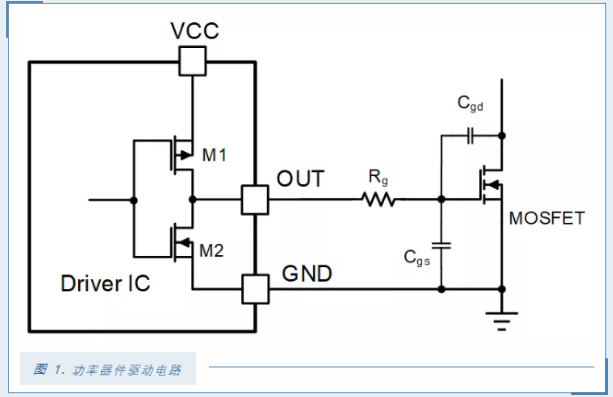

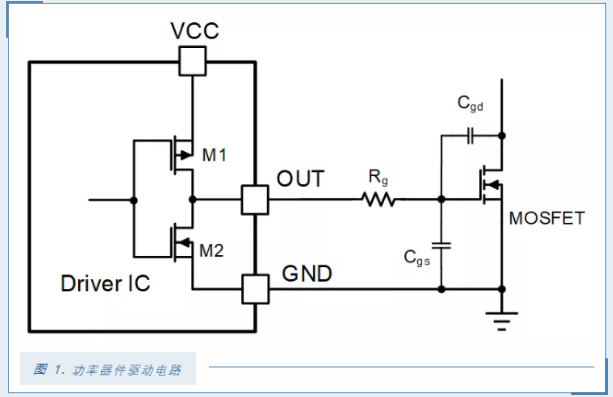

本文主要阐述了在驱动芯片中表征驱动能力的关键参数:驱动电流和驱动时间的关系,并且通过实验解释了如何正确理解这些参数在实际应用中的表现。

2022-01-27 10:45:00 3263

3263

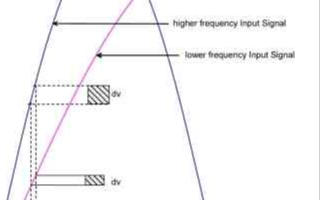

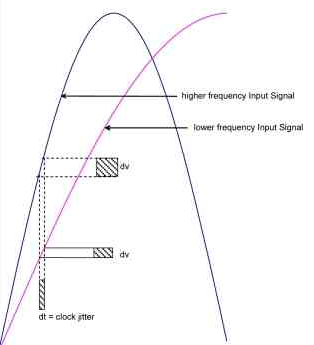

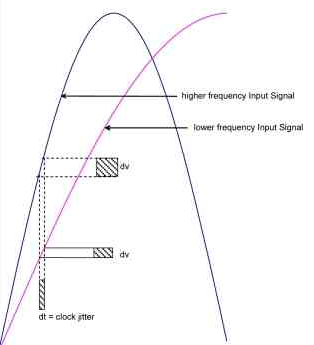

John Johnson 德州仪器 在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t

2018-09-19 11:47:50

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。那么时钟抖动会对高速ADC的性能有什么影响呢?

2021-04-08 06:00:04

在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

2022-11-23 07:59:49

作者:John Johnson,德州仪器 本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成

2018-09-19 14:23:47

本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成了各种委员会和标准机构,根据其开发标准的目标

2022-11-23 06:59:24

转时钟抖动的理解

2016-10-05 12:08:25

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2019-07-30 07:57:42

其它时钟分配方法,其可降低整体抖动性能。您可使用如 LMK03806 等一款器件来克服这个问题,其在同一器件中整合了所有主时钟发生器和时钟分配功能(带驱动器),如图 1 所示。该器件可在 300MHz

2018-09-13 14:18:06

正确理解AC耦合电容在高频电路设计中,经常会用到AC耦合电容,要么在芯片之间加两颗直连,要么在芯片与连接器之间加两颗。看似简单,但一切都因为信号的高速而不同。信号的高速传输使这颗电容变得不“理想

2021-12-30 07:52:17

一、正确理解DC/DC转换器: DC/DC转换器为转变输入电压后有效输出固定电压的电压转换器。DC/DC转换器分为三类:升压型DC/DC转换器、降压型DC/DC转换器以及升降压型DC/DC转换器

2021-11-16 06:32:19

://www.xilinx.com/support/回答/ 38506.htm 250MHz参考时钟应提供0.724pS的时钟抖动。在这种情况下,器件“ICS874001”的抖动为3pS。但是它被用作MGT参考的时钟源。如果

2020-06-08 15:30:33

、STM32F427IIH6外设时钟1、时钟树时钟树的讲解可以参考野火或者原子的书籍,下图展示了STM32F427IIH6的时钟的分频倍频关系。正确理解时钟树有助于我们从一个整体的角度把握芯片的工作时钟,对代码的编写是十分有用的。对于 SYSCLK、 HCLK(AHB总线时钟)、 PCLK2(APB

2021-08-10 07:17:42

开关电源的相关概述,正确理解各类开关电源很重要。

2021-03-16 08:41:02

,TIE 测量非常有用。如果 TIE 值比较大,则表明恢复的时钟 PLL 无法跟上信号数据速率的变化。图3:时间间隔误差测量感谢阅读《定时决定一切》!希望您现在对抖动技术规范有了更好的理解。 更多资源

2018-09-13 14:29:18

您已了解GaN晶体管出色的性能,您很兴奋。样品总算来到,您将它们放入板中。您打开电源,施加负载,结果……性能并没有比以前更好。更糟糕的是,遇到了以前不存在的开关问题。这些晶体管不好。真遗憾。为何出现这种情况?有没有可能遗漏了什么?如何正确理解GaN?十分重要!

2019-07-30 06:21:32

`如何正确理解功率MOSFET的数据表(上篇).`

2012-08-13 14:24:17

磁珠经常在电路中使用,但是如何正确理解磁滞损耗呢?

2021-03-06 08:22:12

本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2021-04-07 06:30:45

采样时钟抖动对ADC信噪比的性能有什么影响?如何实现低抖动采样时钟电路的设计?

2021-04-14 06:49:20

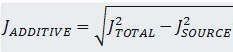

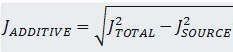

时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要达到所需的系统抖动性能,一定要保持尽可能低的时钟抖动,并在整个

2022-11-22 07:13:40

。这工作正常,直到我决定董事会所做的测量不够准确(在时间轴上)。因此,我将生成的时钟使能信号(2MHz)输出到IO-Pin,并使用示波器测量频率抖动。抖动似乎具有高斯分布,标准偏差约为28ns。我还测量

2020-08-19 06:09:57

嗨,我正在使用Virtex-6和Spartan-6用于医学成像应用,我需要为多普勒测量提供精确的频率可变时钟。歪斜并不重要,但抖动确实如此。对于其他用途和其他器件,我使用了驱动IOB DDR寄存器

2020-06-10 16:36:37

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

2018-09-13 14:38:43

网络分析仪测试基本概念测试对象:各种元器件及器件组成的系统 正确理解关于器件(系统)相关性能指标要求和定义掌握网络分析仪的正确操作和应用的方法[hide][/hide]

2009-11-04 17:11:49

设计采样系统时,关于时钟抖动性能如何考虑?抖动对时钟采样系统有何影响?

2021-04-06 06:07:38

一块音视频处理芯片输出1080i的数据Data及其同步时钟Clk,但是时钟clk的抖动很大,我该如何处理呢?另外,抖动很大的时钟源能否在后面接入一个模拟锁相环降低时钟的抖动呢?

2018-11-12 09:12:43

时钟抖动或结束时钟抖动的最佳方法是什么?

2021-03-17 07:04:07

,你可以实现更高的性能—最多比传统SAW示波器高9倍。 图1:SAW示波器和TI LMK03328的10G链路性能一个低相位噪声基准时钟转化为串行链路中其它关键块的更高抖动允许量分配。随着数据速率快速

2018-09-05 16:07:30

随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展

2008-12-27 12:24:05 6

6 随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展。目前

2009-07-07 14:01:21 20

20 本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24:07 15

15 本文分析了晶振的漂移对GPS 接收机的影响,从锁相环理论的角度,重点分析了采样时钟抖动对基带载波跟踪和伪码跟踪性能的影响,并给出一种环路分级降带宽的方法来消除这种

2009-12-19 13:49:58 19

19 高速互联链路中参考时钟的抖动分析与测量

在高速互联链路中,发送器的参考工作时钟的抖动是影响整个

2010-04-15 14:01:39 19

19 AD9520/AD9522 时钟发生与分配IC,实现最佳器件集成度、低噪声、低抖动性能与信号输出灵活性

全球领先的高性能信号处理解决方案供应商,最新推出一

2008-10-08 11:34:57 1871

1871 该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预期。关

2009-04-21 23:14:05 723

723

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-22 09:35:13 296

296

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16:50 3736

3736

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-25 09:54:26 482

482

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-05-08 10:19:03 431

431

用模拟时钟IC替代昂贵的高频率VCO,改善抖动性能

Analog Devices, Inc.,全球领先的高性能信号处理解决方案供应商,

2009-09-01 17:26:25 855

855 AD9547 具有高出66%的抖动性能、100倍的更窄回路滤波器带宽的时钟器件

AD9552能够替代包括OCXO(恒温

2009-09-01 17:28:35 851

851 评估低抖动PLL时钟发生器的电源噪声抑制性能

本文介绍了电源噪声对基于PLL的时钟发生器的干扰,并讨论了几种用于评估确定性抖动(DJ)的技术方案。推导出的关系式提

2009-09-18 08:46:32 1461

1461

理解不同类型的时钟抖动

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误

2010-01-06 11:48:11 1608

1608

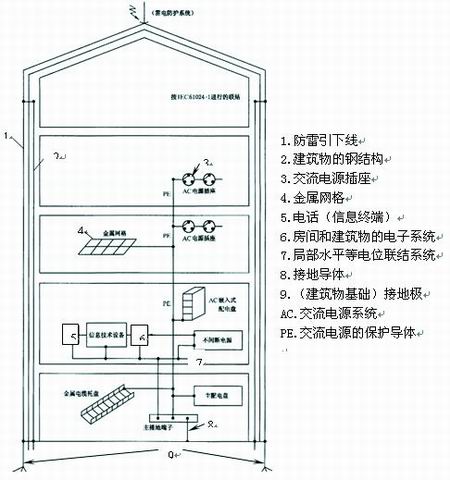

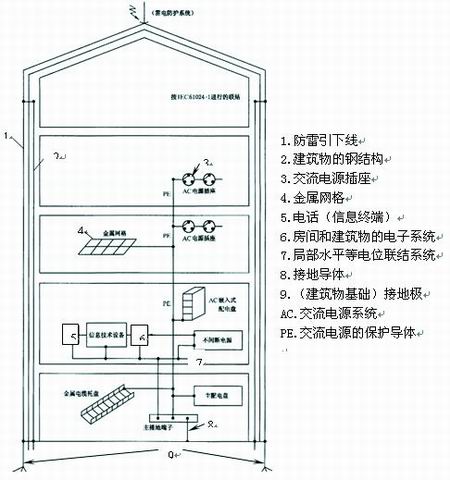

正确理解和测试信息技术设备的接地

正确理解电气设备,尤其是敏感的信息技术设备的“接地”概念,是工程施工与检测的基础。所谓“接地”是否意味着必

2010-01-08 11:40:16 725

725

基于DDS的时钟抖动性能与DAC重构滤波器性能的关系

2011-11-25 00:01:00 36

36 时钟抖动时域分析(下):

2012-05-08 15:26:25 29

29 的系统设计,如在某些情况下系统性能极限由系统决定时序裕量。所以对时序抖动有很好的了解在系统设计中变得非常重要。总抖动可以随机抖动和确定性抖动分离组件。我们将不讨论抖动的组件本申请说明。我们将专注于不同类型的时钟

2017-04-01 16:13:18 6

6 很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们

2017-04-08 04:51:23 1266

1266

了解高速ADC时钟抖动的影响将高速信号数字化到高分辨率要求仔细选择一个时钟,不会妥协模数转换器的采样性能(ADC)。 在这篇文章中,我们希望给读者一个更好的了解时钟抖动及其影响高速模数转换器的性能

2017-05-15 15:20:59 13

13 时钟抖动时域分析,第 2 部分

2017-10-26 16:10:42 6

6 时钟抖动时域分析 第 3 部分

2017-10-26 16:13:28 4

4 时间域中分析的时钟抖动,第 1 部分

2017-10-26 16:16:23 4

4 本文主要讨论采样时钟抖动对 ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。 ADC 是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定

2017-11-27 14:59:20 17

17 因此,设计人员必须假定来自各个芯片厂商的参考时钟抖动规格指标与他们预期使用的这些器件相关,并且这些规格指标已经被完全和正确地确定。

但如果没有一些基本准则可循,设计师可能会指定过高的时钟抖动

2018-06-06 16:19:00 3019

3019

时钟接口阈值区间附近的抖动会破坏ADC的时序。例如,抖动会导致确定性抖动由干扰引起,会通过某些方式使阈值发生偏移,通常受器件本身特性限制。查看时钟信号噪声通常有三种途径:时域、频域、相位域。

2018-03-12 13:39:33 21583

21583 该应用报告提出了在TI仪器上的CDCE72010抖动清理器和同步器PLL器件上获取的相位噪声数据。CDCE72010的相位噪声性能取决于基准时钟、VCXO时钟和CDCE72010本身的相位噪声。该应用报告显示了几个最流行的CDMA频率的相位噪声性能。此数据有助于用户为特定应用选择正确的时钟解决方案。

2018-05-15 10:58:53 7

7 ADI研讨会:高性能时钟: 解密抖动

2019-08-20 06:05:00 1656

1656 时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速ADC在内的数字电路的性能。高速时钟可以对它们所接收的功率的“清洁度”非常敏感,尽管量化关系需要一些努力。

2019-09-14 11:24:00 7712

7712

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2020-09-23 10:45:00 2

2 对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。借助本文,我们将使读者更好地理解时钟抖动问题及其对高速ADC性能的影响。

2020-08-01 11:26:11 1116

1116

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。借助本文,我们将使读者更好地理解时钟抖动问题及其对高速ADC性能的影响。

2020-08-20 14:25:16 791

791

电子发烧友网为你提供正确理解电路保护设计及器件选择资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-01 08:53:02 12

12 前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容: 时钟抖动的构成 时钟抖动对ADC SNR的影响 如何计算时钟抖动 如何优化时钟抖动 1.采样理论

2021-04-07 16:43:45 7378

7378

电子发烧友网为你提供选型必读:正确理解电阻在电路中的作用资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-13 08:54:23 59

59 电子发烧友网为你提供如何正确理解嵌入式软件可靠性设计?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-18 08:50:56 2

2 超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 ADC时钟接口中的最小抖动

2021-05-09 12:19:40 6

6 作者: Richard Zarr

如果您在通信行业工作,那么您可能很熟悉抖动对系统性能的影响。抖动不仅会降低数据转换器的性能,而且还可在高速数字系统中产生误码。凭直觉判断,给时钟增加噪声会增大

2021-11-23 17:45:07 1769

1769

的 TI 时钟专家能解决您的所有时钟问题,满足您的任何需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速

2021-11-10 09:42:52 901

901

正确理解ESD单元在一个器件中是如何实现的,设计人员就能通过适当的电路设计大大扩展放大器的生存范围。

2022-09-05 10:07:19 402

402 超低抖动时钟发生器如何优化串行链路系统性能

2022-11-04 09:50:15 0

0 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 时钟抖动解秘—高速链路时钟抖动规范基础知识

2022-11-07 08:07:30 1

1 1.1.1. 抖动定义和分类 ITU-T G.701对抖动的定义为:“抖动是指数字信号在短期内相对于理想位置发生的偏移重大影响的短时变化”。 对于真实物理世界中的时钟源,比如晶振、DLL、PLL,它们的时钟输出周期都不可能是一个单点的固定值,而是随时间而变化的

2023-03-10 14:54:32 657

657

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1637

1637 首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。

2023-06-02 09:09:06 1026

1026

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 1128

1128

本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 960

960

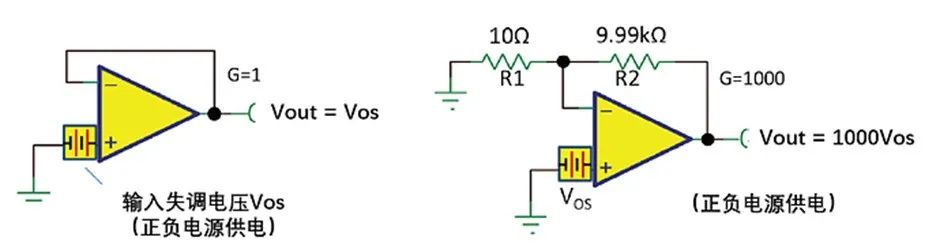

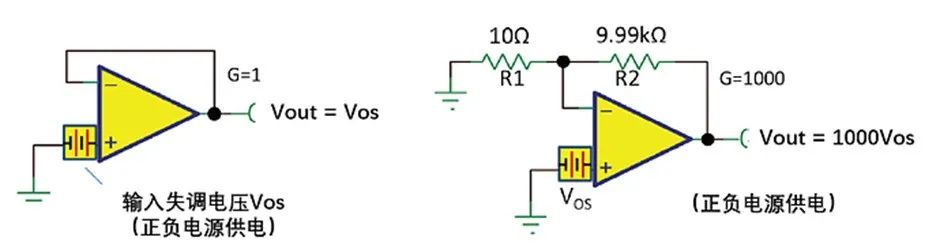

如何正确理解运算放大器输入失调电压?

2023-12-07 11:05:11 227

227

电子发烧友网站提供《时钟抖动对ADC性能有什么影响.pdf》资料免费下载

2023-11-28 10:24:10 1

1

时,峰峰值约等于14 倍的标准偏差值,即为

时,峰峰值约等于14 倍的标准偏差值,即为 。

。

(1)

(1) dBc/Hz,BC 段20dBc 衰减,幂率近似为

dBc/Hz,BC 段20dBc 衰减,幂率近似为  的噪声类型。

的噪声类型。

电子发烧友App

电子发烧友App

评论