已经有段时间了。但是,在要求快速切换速度、低相位噪声或低杂散信号电平的场合,有必要使用更为复杂的架构。通过正确的设计方法,结合使用现代低成本高集成度的PLL和直接数字合成器(DDS)集成电路(IC)可以极大地促进高性能架构的实现。

2022-10-14 10:30:36 2026

2026 ,人们倾向于 PLL 的原因之一是熟悉它。所以,有必要让我们加深对 DDS 的了解。(注意,这并不需要联系美国牙医协会) 在简要评述先进 DDS 技术之前,为了避免将已经出版的东西老调重弹,我要再次提醒

2018-08-01 07:29:23

的可变分频器扫频,但这样做的可控性或可重复性远不如DDS扫频。 相位分辨率与灵活性在模拟PLL中,任何相位调整的结果都是遍历环路,所以它不是像DDS那样的精确可重复变化。数字PLL可提供一定程度的相位调整能力。 幅度分辨率与灵活性幅度不是PLL所改变的参数。

2019-01-18 13:19:36

这样做的可控性或可重复性远不如DDS扫频。相位分辨率与灵活性:在模拟PLL中,任何相位调整的结果都是遍历环路,所以它不是像DDS那样的精确可重复变化。数字PLL可提供一定程度的相位调整能力。幅度分辨率与灵活性:幅度不是PLL所改变的参数。:ADI工程师博客分享——DDS与PLL的细微差别

2018-10-11 11:15:23

本文仅以DG5000为例来详细说明DDS信号源在扫频测试中的具体应用。

2021-05-13 06:25:54

本人很喜欢短波,希望各位分享一下DDS在短波电台的应用资料。

2012-11-05 12:16:06

DDS的工作原理是什么?基于DSP Builder和DDS设计基于FPGA的DDS设计

2021-05-06 06:27:03

合成一个正弦信号,那么了解一点直接数字式频率合成器(Direct Digital Synthesizer,DDS)会有助于您确定最佳解决方案哦~ 多数工程师在求学时接触过锁相环(PLL),但DDS不是

2019-02-13 11:54:20

几何尺寸缩小,这一差距也会缩小,但规模经济也会导致其缩小。PLL使用更广泛,生产规模要大得多,有助于改善成本结构。如果是针对大规模应用,并且DDS方案有一些优势,那么在价格上应该有一定的协商空间。宽频

2018-10-31 10:57:30

大家好 在virtex 5 FPGA用户指南ug190中,它说: “Virtex-5 FPGA中的时钟管理磁贴(CMT)包括两个DCM和一个PLL。在CMT中有专用路由将各种组件耦合在一起。” 在7

2020-08-21 09:16:28

我尝试使用“clockin向导”在Spartan6中使用PLL我们可以指定的2个参数是输入和输出抖动。但是与构建PLL的常用参数有什么关系:1)输入捕获范围,定义输入频率的窗口:是输入抖动吗?2

2019-06-06 11:14:34

在quartus上想修改软核PLL中设置,为什么打不开啊?想改一改PLL的分频,打不开pll核。如图

2017-02-02 16:10:34

在输入时钟为1G的情况下,设置了00,01,02,0b,0c,0d寄存器后,能实现DRG扫频,现在需要改成输入时钟换小点,10M或者其他的。看手册只需对SFR3(02)进行设置,外部时钟我设为83M

2018-11-20 09:08:13

!请问各问大神有没有遇到类似问题;寄存器参数写入顺序如下,

dds_data_ram[0] <= 40'h02_00050C00; // PLL

2023-12-06 06:27:34

如何去描述AD9958的内部结构?AD9958串口特点有哪些?AD9958工作模式有怎样的?AD9958在PLL及调制系统中的应用是怎样的?

2021-04-13 07:10:18

切实可行。 0 引言 电源的信号测控部分由DDS信号发生和信号测量组成。DDS 在电源设计中的应用早已存在。在早期的DDS 设计中,硬件组成由计数器、触发器等多种多个分立逻辑元件组成; 而在

2018-11-29 17:08:05

在配置PLL过程中,打开了megawizard plug-in manager后,下拉菜单中没有IO这个选项,更别说选ATLPLL了,求问这是什么情况!PLL配置教程原帖http

2017-03-22 09:58:41

最近,在 Modelsim 中仿真含有 PLL quartus 工程时,遇到了问题:Error: (vsim-3033) E:/Software_class/eda_study

2014-02-22 14:31:28

SI2302DDS-T1-BE3

2023-03-29 21:44:21

本文着重介绍了泰克示波器全新频谱分析功能Spectrum View在电源调试和PLL故障排查诊断中的应用。实测表明,Spectrum View的多通道时频域联动分析,非常便于干扰信号定位以及电路故障排查,为开发工程师调试产品提供了重要依据。

2020-11-24 06:25:57

本文着重介绍了泰克示波器全新频谱分析功能SpectrumView在电源调试和PLL故障排查诊断中的应用。

2021-06-17 10:45:32

quartus中PLL的复位是高电平复位还是低电平复位,可不可以修改

2014-03-21 11:10:25

什么是DDS?DDS的工作原理是什么?怎么做出一个DDS模块呢?

2022-01-26 06:31:21

限,因此在设计工作频率宽、调协精度高的频率合成器时,这两种方式均不能满足技术要求。但是,采用DDS+PLL方式,可以满足高精度和宽频带的需要,其实现的难点是如何提高合成器输出频谱纯度。在实际印制电路板制作中,DDS的良好接地和合理布线非常有助于系统设计的实现。来源:与非网

2011-07-16 09:09:54

请教有经验的射频工程师,采用DDS+PLL的方式设计雷达发射源,要求发射信号为26GHz单频连续波信号以及三角形LFMCW信号,25.5GHz~26.5GHz,调制周期2ms,通过单片机控制波形切换,请推荐DDS和PLL芯片型号,以及晶振的选择,十分感谢

2018-10-09 17:39:06

想问一下,在使用PLL中,输出的Locked管脚是什么,具体有什么作用,能不能作为整个系统的复位信号?

2014-06-27 20:40:38

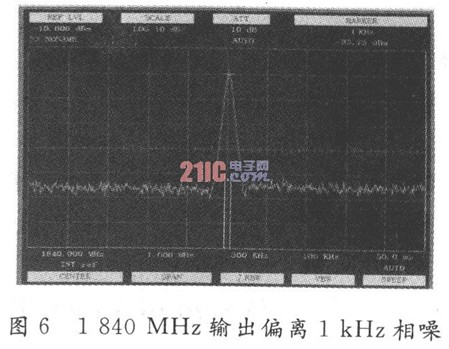

低通滤波得到正弦信号,然后对该信号进行调频,调幅。其中调频部分可以通过在软件中修改DDS芯片的频率控制字,相位控制字等来实现,而调幅部分需在DDS输出正弦信号之后外加一调幅器实现。调幅部分将DDS输出作为载波信号,RC振荡器提供1KHz振荡作为调幅信号,它利用了乘法器MC1496完成对正...

2021-07-21 07:14:36

直接数字频率合成(DDS)在过去十年受到了频率合成器设计工程师极大的欢迎,它被认为是一种具有低相位噪声和优良杂散性能的灵活的频率源,基于DDS的频率合成器在许多应用中能比基于锁相环(PLL)频率

2019-07-08 07:26:17

介绍直接数字合成器 (DDS) 是软件定义无线电和数字通信系统中的关键工具,因为它们提供了一种在数字域中生成复杂信号的方法,该信号也是可变的。虽然 DDS 背后的理论相当简单,但第一次在 FPGA

2023-02-08 15:39:30

将哪些文件复制到项目中。在询问之前,我试图将xxx.vhd和.ngc文件复制到我的项目中dds编译器模块实例。但是在合成步骤。 ise告诉我第385行找不到模块/原语'dds_compiler_v4_0'....请帮我解决这个问题

2020-04-01 09:40:21

我们的产品要求低功耗,我现在想通过设置PLL降低主频,根据不同的使用状态使用不同的PLL分频系数,请问在程序运行中能够切换吗?怎么实现?

2020-04-21 10:08:34

DDS的工作原理是什么?如何抑制DDS输出信号中杂散问题?

2021-05-26 07:15:37

讨论了何时、在哪里以及为什么用基于 DDS 的方法代替基于 PLL 的方法。不过,人们倾向于 PLL 的原因之一是熟悉它。所以,有必要让我们加深对 DDS 的了解。(注意,这并不需要联系美国牙医协会

2018-10-31 10:53:03

图2中,同一100 KHz音以完全相同的频率偏移传输到DDS/DAC输出,不受调谐字频率影响。图2中的频率调谐字表现出四个相互叠加的不同DDS载波。注意,在全部四个载波改变时,参考时钟杂散的频率

2023-12-15 07:38:37

230MHz无线电台通信系统在电力负荷管理系统和用户用电信息采集系统中有着广泛的应用。然而,随着无线通信技术的发展,在不同时期投入应用的无线电台,虽然基本结构类似,但调制方式、波形结构、调制速率都有

2019-08-02 06:59:56

本文将介绍DDS和PLL的工作原理,并结合一电台(工作频率2 MHz~500 MHz)的设计,给出DDS做参考的PLL频率合成器的设计方案。

2021-04-20 06:42:27

亲爱的先生,我正在尝试在Spartan 6中使用PLL。我有Nexys 3板和Lx16封装CSG324封装。参考手册说它有2个CMT,即4个DCM和2个PLL。但每当我想从新的源向导中插入新的源代码

2019-03-04 12:15:52

信号发生器是一种常用的信号源,广泛应用于通信、测量、科研等现代电子技术领域。信号发生器的核心技术是频率合成技术,主要方法有:直接模拟频率合成、锁相环频率合成(PLL)、直接数字合成技术(DDS

2019-09-29 08:08:12

公司相比,在价格上要优惠很多(如,成都国腾生产的GM4954,GM9910,GM4940,GM4153等) ——一块DDS芯片中主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分(如Q2220

2012-06-20 15:51:30

挺挺好的! 实际工作中很是讨厌PLL数字调台的基准频率和CPU时钟振荡:他们的n次谐波往往落在FM工作频段,这些问题次次都搞得我们七荤八素的。所以在这类机机中往往能看到铁皮盒子。 另外一个方面,PLL线路不需要调谐机构,产品的外型设计较灵活。

2010-12-25 10:26:40

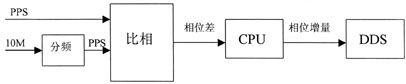

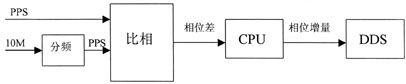

。图1中,DDS作为PLL的激励源,PLL作为跟踪倍频锁相环[2]。 图1 常规用DDS驱动PLL的原理 改进型DDS驱动PLL原理如图2所示: 图2 改进用DDS驱动PLL的原理 主要

2020-12-03 16:06:44

高温、湿润、低温、强电磁场或尘埃较大的环境中运用,在对数传电台进行测验时,有必要接上匹配的天线或5Ω假负载,不然简单损坏发射机。假如接了天线,那么人体离天线的间隔最佳超越2米,避免造成伤害,切勿在发射

2018-08-29 09:17:44

是否可以通过软件在驱动程序中交换/更改 PLL(IMX8MM_AUDIO_PLL1_OUT、IMX8MM_AUDIO_PLL2_OUT)?目前,我们的 SoC CODEC 驱动程序使用固定 PLL

2023-03-28 08:36:52

发展起来的新型的频率合成技术,与传统的VCO+PLL的模拟方式产生所需频率相比,DDS技术具有频率分辨率高,相位噪声低,带宽较宽,频谱纯度好等优点。这些技术指标在一个系统中是至关重要的,决定着一个系统的成败。

2019-08-22 06:06:12

,PLL锁定引脚为低电平,DDS出来的信号也频也不对,也没有锁定,而且当我把外部时钟关掉后,DDS出来的那没有锁定的信号还在,当不加外部时钟时配寄存器无信号出来,加外部时候后那没有锁定的信号出来后就跟时钟

2023-11-27 08:04:33

直接数字频率合成(DDS)具有快速频率切换和调制能力,应用广泛。但是,当低功耗和低成本是主要考虑因素时,DDS常常不得不退居其次,让位于模拟锁相环(PLL)。AD9913改变了这一局面,不仅

2011-09-06 14:47:52

在DDS系统中通过DDS内部倍频得到芯片参考时钟,内部倍频是否对输出信号有影响,比如说AD9951采用100M晶振然后芯片内部4倍频得到参考时钟,经过测试,输出信号经过滤波之后存在100M频率分量,总是不能完全抑制,这是什么原因导致的呢???

2018-09-26 14:15:33

@使用AD9858评估板中的DDS和PLL来实现YTO(或者叫YIG)的锁频,但是目前锁不住,我想有可能是环路滤波器的问题,照着网上的资料下载了ADI计算PLL参数的软件,发现里面可以选择的芯片

2018-09-28 15:05:29

。数传电台透明传输是数传电台发送端数据串口收到的数据会无更改从接收端数据串口输出,在透明传输的数传电台中,电台通常不会识别传输数据内容。目前大多数的数据采集和控制系统采用透明传输数传电台,在透明数传电台

2020-12-03 14:56:58

。 RPM网格中所需的相对坐标(可在FPGA编辑器中看到)显示在组件名称旁边的括号中。由于放置限制,不可能将组件放置在所需的形式中。PLL PLL_BASE_inst / PLL_ADV(0,0)锁定

2018-11-05 11:31:02

四种合成方式:直接模拟式频率合成、锁相频率合成(PLL)、直接数字式频率合成(DDS)和混合式频率合成(DDS+PLL)1 指标要求与方案分析 具体指标如下: 频率范围:9.87~10.47 GHz

2019-06-21 06:32:34

DDS(直接数字频率合成)技术是一门在频率合成领域的新兴技术,具有响应时间短,精度高等优点。而PLL(Phase Locked Loop)锁相环技术虽然工作速度慢,但稳定可靠。VXI 总线具有

2009-06-01 16:12:24 17

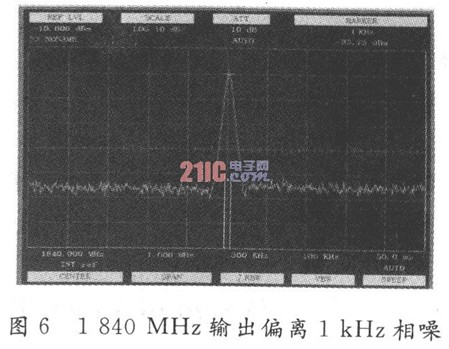

17 本文讨论了DDS+PLL 结构频率合成器硬件电路设计中需要考虑的几方面问题并给出了设计原则,依此原则我们设计了一套短波波段频率合成器,实验结果证实了其可行性。

2009-09-07 16:07:29 34

34 直接数字合成(DDS)是近年发展起来的一种新型合成技术,有频率分辨率高,转换时间短,相位噪声低等特点,与锁相合成技术(PLL)配合,可以设计出频带宽、分辨率高的频率

2009-09-11 15:55:32 13

13 针对直接数字频率合成(DDS)和集成锁相环(PLL)技术的特性,提出了一种新的DDS 激励PLL 系统频率合成时钟发生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用滤波的方法

2009-12-14 10:22:00 36

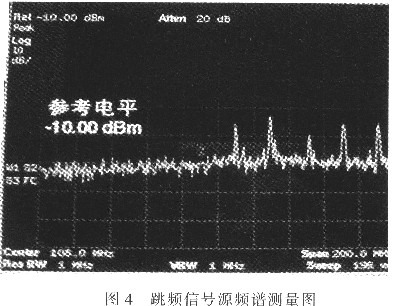

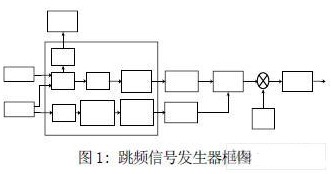

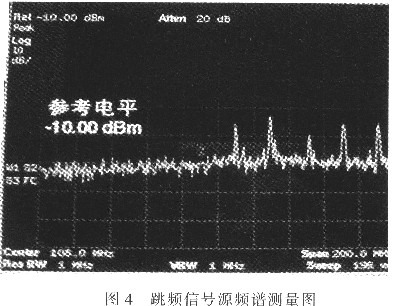

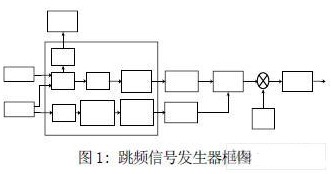

36 针对某机载电台技术指标的检测控制需求以及该电台激励信号和响应信号的特点,提出一种以FPGA(EP1C12)作为控制核心,采用DDS(AD9850)+PLL(MC145152)数字频率合成的跳频信号发

2010-01-07 12:36:34 13

13 概述OMG DDS(Data-Distribution Service)协议测试套件是北汇信息与臻容科技合作研发的针对 DDS 中间件软件的测试套件。该套件用于验证 DDS(Data-Centric

2023-10-11 13:48:54

直接数字合成(DDS)是近年发展起来的一种新型合成技术,有频率分辨率高,转换时间短,相位噪声低等特点,与锁相合成技术(PLL)配合,可以设计出频带宽、分辨率高的频率合

2010-08-04 15:57:03 0

0 DDS技术及其在BITS中的应用

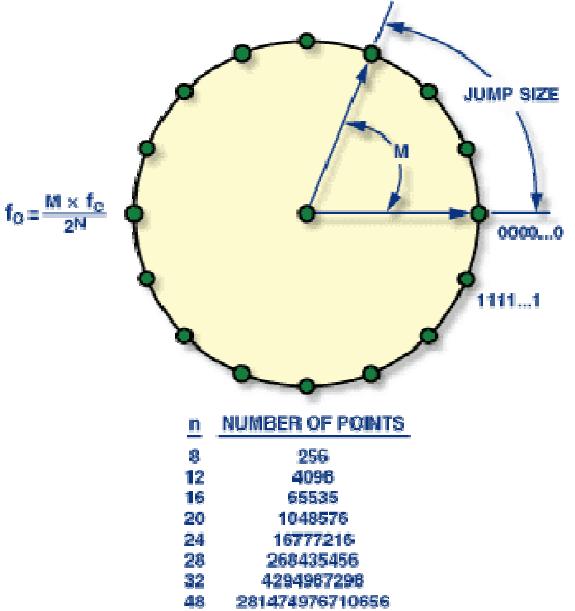

在频率合成(FS, Frequency Synthesis)领域中,常用的频率合成技术有模拟锁相环、数字锁相环、小数分频锁相环(fractional-N PLL Synthesis)等

2009-02-08 11:13:16 728

728

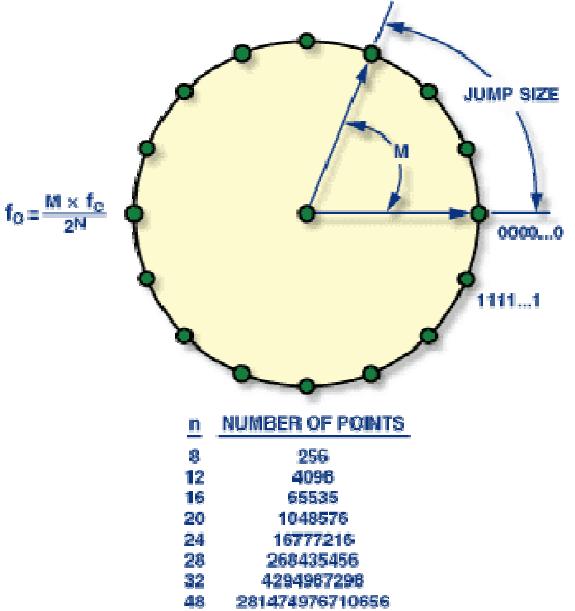

DDS,什么是DDS,DDS的结构

DDS概述

直接数字式频率综合器DDS(Direct Digital Synthesizer),

2009-09-03 08:42:40 4227

4227

数传电台

数传电台(data radio)是指借助DSP 技术和无线电技术实现的高性能专业数据传输电台。数传电台的使用从最早的按键电码、电报、模拟电台加无

2010-01-06 14:08:25 3027

3027 DDS是什么意思,DDS结构,DDS原理是什么

什么叫DDS

直接数字式频率合成器DDS(Direct Digital Synthesizer),实际

2010-03-08 16:56:38 45260

45260 电台modem,电台modem是什么意思

目录1 modem的概念 2 modem的分类 3 modem的工作原理 4 电台的概念 5 电台分类 6 电台相关

2010-03-23 10:19:23 1263

1263 锁相环(PLL),锁相环(PLL)是什么意思

PLL的概念

我们所说的PLL。其

2010-03-23 10:47:48 6005

6005 数字PLL,什么是数字PLL

数字PLL

PLL的概念

我们所说的PLL,其实就是锁相环路,简称为锁相环。许多电子设备要正常工作,通常

2010-03-23 10:50:06 4281

4281 模拟PLL,模拟PLL是什么意思

所谓模拟PLL,就是说数字PLL中的各个模块的实现都是以模拟器件来实现的,是一个模拟

2010-03-23 10:52:01 2645

2645 直接数字合成(DDS),直接数字合成(DDS)是什么意思

直接数字合成(DDS)的概念

1971年,美国学者J.Tierncy,

2010-03-23 11:06:11 2286

2286 DDS+PLL高性能频率合成器的设计方案

频率合成理论自20世纪30年代提出以来,已取得了迅速的发展,逐渐形成了直接频率合成技术、锁相频率合成技术、直接数字式频率

2010-04-17 15:22:13 3209

3209

航空通信设备包括短波通信、超短波通信设备,短波、超短波通信设备又分为常规通信方式和跳频通信方式,跳频通信因具有抗干扰性强、抗侦测能力好、频谱利用率高和易

2010-09-08 11:15:52 1939

1939

倍频/混频方法杂散较大,谐波难以抑制;DDS器件工作频率较低且功耗较大,而PLL 技术相对来说具有应用方便灵活与频率范围宽等优点,是现阶段主流的频率合成技术。

2011-10-26 12:05:01 215

215 为了满足宽频段、细步进频率综合器的工程需求,对基于多环锁相的频率合成器进行了分析和研究。在对比传统单环锁相技术基础上,介绍了采用DDS+PLL多环技术实现宽带细步进频综,输

2013-04-27 16:26:51 48

48 2014-09-25 09:23:41 0

0 关于DDS ad9854芯片的应用介绍 单片机ad9854芯片整体构架。

2016-05-09 10:15:22 0

0 DDS-PLL组合跳频频率合成器,有需要的都可以看看。

2016-07-20 15:48:57 42

42 学习单片机电路图的很好的资料——DDS-PLL组合跳频频率合成器

2016-11-03 15:15:39 0

0 The AD9956 is Analog Devices’ newest AgileRF synthesizer. The device is comprised of DDS and PLL

2017-10-20 08:55:00 8

8 将DDS和PLL技术结合起来,采用DDS直接激励PLL的混合频率合成方案完成了X波段微波变频信号源的设计,一定程度上解决了频率分辨率、频率转换速度和相位噪声的问题,并完成了实机研制、系统联调试

2017-10-27 11:18:52 4

4 结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分 辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析

2017-10-27 17:54:21 8

8 在现代电子测量、雷达、通信系统、电子对抗等技术领域中,具有频率范围宽,分辨率高,转换快速的多种模式的信号源是重要和必不可少的。20世纪70~80年代大都采用锁相 频率合成技术 ,实现频率范围为DC(MHz)~几十GHz,分辨率达到MHz的信号源。虽然转换速度不高(几十μs到ms量级),但已广泛应用到现代电子系统中;与此同时,各种规格的锁相频率合成技术的信号源产品也投入到国际市场。

2018-03-17 11:18:00 6524

6524

为了保证机载电台的设计性能和通信质量,并且各种电台都有各自详细的技术指标要求,需要使用很多台单一功能的仪器或综合检测仪来测试。目前,产生稳定可靠、符合要求的跳频信号已成为进行跳频关键技术验证、通信

2019-07-18 08:14:00 3811

3811

直接数字频率合成技术(DDS+PLL)资料下载。

2021-06-07 14:41:54 38

38 介绍了采用单片机控制DDS+PLL组合式频率合成器的方法,结合实际项目给出了采用双模分频器MB1505和直

接频率合成器AD9835寄存器参数的算法,以及如何利用单片机对频率进行微调和线性校准,并对设计的频率合

成器进行了测试实验。

的应用

2023-05-18 09:41:00 3

3 本文对DDS以及基于DDS的SOA系统的测试策略进行探讨,并介绍DDS测试方案。

2022-08-04 14:52:04 1326

1326

频率的产生有两种方法:DDS和PLL,但是为什么射频工程师一般用PLL多,很少用DDS呢?

2023-06-28 09:38:48 1823

1823

电子发烧友网站提供《一种用DDS激励PLL的X波段频率合成器的设计方案.pdf》资料免费下载

2023-10-24 09:10:26 4

4 V CO 输出本地参考频率。由于V CO 采用模拟电路, 这将带来元件 饱和、直流漂移、非线性等问题。因此, 全数字锁相环得到了越来越广泛的应用。

本文介绍一种 DD S(D irect D igital Syn thesizer) 与 PLL (Phase L ocked L oop ) 技术

2023-11-09 08:31:40 1

1

电子发烧友App

电子发烧友App

评论