异步 FIFO 读写分别采用相互异步的不同时钟。在现代集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟,多时钟域带来的一个问题就是,如何设计异步时钟之间的接口电路。异步 FIFO

2020-07-16 17:41:46 1050

1050

FIFO是队列机制中最简单的,每个接口上只有一个FIFO队列,表面上看FIFO队列并没有提供什么QoS保证,甚至很多人认为FIFO严格意义上不算做一种队列技术,实则不然,FIFO是其它队列的基础

2022-07-10 09:22:00 1338

1338 刚才看了A/D与D/A的教程视频,哦 原来 A/D与D/A是 数字量与模拟量之间的转换。A/D嘛 可以做 很多的功能,如万用表,电压,电流,电阻,等等,通过A/D 把模拟量转换成数字量,经过一些处理

2012-12-29 09:29:21

A/D转换的原理是什么?电路之间如何连接?

2022-01-20 06:54:04

/ VPSS) links;//两个M3核之间,M3Vpss -- M3Video

Inter processor (M3 to A8 or DSP);//M3 -- A8 或者 M3 -- DSP

2018-06-21 03:28:07

想咨询一个问题,我想用5509A来读取存放在FIFO(IDT7205,9*8192)中的数据(来自8位ADC采集),ADC和FIFO用的相同的CLKIN,DSP的CE1定义为异步存储器,DSP

2014-11-04 20:29:28

想通过FIFO, 把数组Uint16 dataA={123,123,123,123,123,123,123,123}发送到上位机,FIFO是一次发送8个数据,分别是dataA的8个元素,但用串口助手

2019-08-30 11:17:37

我有个项目,要处理一个具有44个字节的数据帧,加上帧头和校验位等共48个字节左右,而DSP2812的FIFO是16级深度的,怎么解析数据较好?

2019-08-21 23:16:48

FIFO将数据传到DSP F2812 的IO引脚来实现数据的传输,但是FIFO输出的电流时mA级别的,而DSP吸收的电流时uA级别的,导致电流不匹配,以至于DSP读出的数据是错误的。因为DSPIO引脚本身接上了上拉电阻,如果再接下拉分流的话,IO电压降固定咯。这个问题怎么破?求大神HELP。

2014-09-19 11:10:11

; 系统设计方案 根据RTL8139的以上特点,作者设计了RTL8139与DSP之间的接口解决方案。目前DSP与PCI的接口一般有二种方案:(1)用CPLD来实现。优点是可以进行功能优化,不必实现所有

2009-09-19 09:43:24

在由DSP芯片组成的信号处理系统中,A/D和D/A转换器是非常重要的器件。一个典型的实时信号处理系统的输入信号可以有各种各样的形式,可以是语音信号或是来自电话线的已调制数字信号,也可以是各种传感器

2015-09-07 22:23:47

做基于DSP的氧化锌避雷器在线监测装置设计,想将一模拟信号输入DSP,进行A/D转换与FFT。有没有程序。

2014-05-20 22:02:58

大家好,我有一个设计问题,我有两个域之间的接口:输入是50MHz的16位并行数据输出为500 MHz的1位串行数据,对于这种情况,我需要设计一个FIFO。任何人都可以帮助我设计FIFO,特别是最小

2019-01-10 10:45:27

领域。本文基于雷达实时信号处理的需要,用FPGA实现了多DSP信号处理模板局部总线和基于标准VME总线的计算机进行通信的接口设计。 2 VME总线的功能特点VME总线系统的功能结构可以分为4类:数据传输

2019-04-22 07:00:07

AD7768的pin control mode是什么意思,引脚D0-D7应该连接DSP的什么接口呢?串口?SPI?FSI?

2024-01-26 06:16:37

摘要:讨论了CAN总线控制器与DSP之间的接口,介绍了流行的CAN控制器芯片SJA1000和TMS320系列DSP芯片的接口时序,并给出了它们的接口方法和电路。关键词:CAN控制器 DSP 时序

2018-12-03 15:22:37

正在工作。现在我要从/到SD卡进行块R / W,我被困在这里,因为s-port不支持任何FIFO接口(如果我错了请指正)。我看了看参考代码和代码中,我看到s-port与DMA接口。请注意,在我的情况下

2018-09-26 10:03:16

MAX153和MX7545的工作模式是什么TMS320C30与A/D和D/A接口的设计,有什么注意事项?

2021-04-22 06:43:58

和TMS320C54XX DSP芯片之间采用FIFO(First In First Out SRAM)芯片连接,可以使USB接口芯片和DSP之间的最大数据交换速度超过USB总线的速度,使之不成为数据传输的瓶颈

2019-04-26 07:00:18

限制。由于AN2131Q芯片内嵌8位8051处理器,所以使用两片8位FIFO芯片实现USB接口和DSP之间的双向通信。FIFO选用具有1K×9bit内存的IDT72V02。从AN2131Q或者DSP

2018-12-20 10:54:45

TMS320VC5402+DSP与串行AD73360+A_D转换器的接口设计

2013-11-12 23:15:53

\\XQ_EMIF16文件夹下。1.1.2 功能简介实现DSP与ZYNQ PL端之间EMIF16接口传输功能。DSP首先通过EMIF16接口往ZYNQ PL端发送4096字节数据,然后再读回来,并检测数据是否有错,数据

2023-03-08 16:46:37

实现DSP与ZYNQ PL端之间EMIF16接口传输功能。DSP首先通过EMIF16接口往ZYNQ PL端发送4096字节数据,然后再读回来,并检测数据是否有错,数据发送、读回以及错误情况实时打印

2023-03-21 15:30:37

。FIFO_PATTERN_[9:0] 从哪里来?Next reading from FIFO output registers 和 FIFO_PATTERN 之间的关联是如何设置的?读取16位字序列Gx Gy Gz XLx XLy XLz需要哪些详细步骤?

2023-02-07 08:16:18

请教ti技术专家:看了keystone 2 -----tci6638k2k的硬件架构,包括了4片arm a15与1片c6678 DSP ,其中dsp包含了8个core。软件架构是用muticore

2018-12-27 11:16:33

不同的时钟域间就可以采用FIFO来作为数据缓冲。另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配

2016-10-04 14:38:07

不同的时钟域间就可以采用FIFO来作为数据缓冲。另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配

2016-10-11 22:17:54

,采用FIFO器件作为A/D转换器与DSP之间的桥梁,可以根据具体需要灵活设置FIFO的各个标志,使其具有很强的外部接口能力;并且通过软件很容易调整A/D转换器、FIFO和DSP的操作时序,增强了操作

2012-12-25 15:45:49

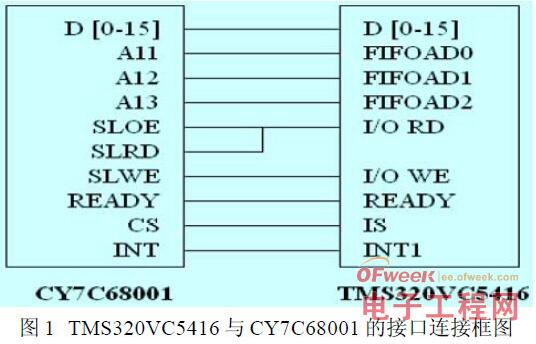

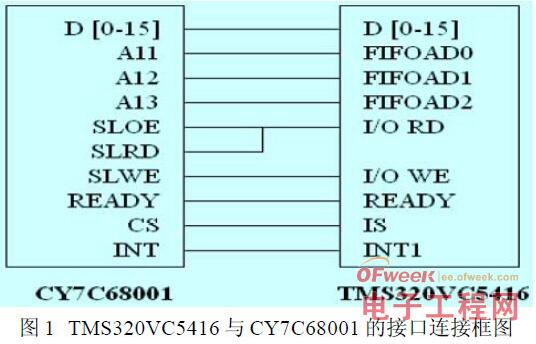

CY7C68001 实现了USB2.0 从机接口设计,通过硬件平台的搭建和软件程序设计,实现了PC 机与DSP 之间高速双向地传输数据。 1 引言 近年来,随着数字信号技术的发展,需要处理的数据量

2019-06-12 05:00:10

可以接收512, 512, 512、512和352字节的数据包。b)FPGA必须立即读出任何到达的包。否则,问题A发生。这需要在主机和FPGA之间进行额外的流量控制。有没有更好的方法来解决这个框架问题时,使用FIFO从接口?某人

2019-09-30 13:50:04

复杂、开发周期长,本文介绍一种采用单片机为控制单元,通过RS232C接口,使用高速FIFO存储器件作为缓冲,在单元电路与计算机之间传输数据的方案。该方案实现简单,开发周期短,完全可以满足对于上述的数字

2019-04-29 07:00:07

C6727B,由于其片内集成dMAX模块,使得实现嵌入式FIFO成为可能。其实现嵌入式FIFO的本质就是将DSP的片内一段RAM空间设置成FIFO空间,FIFO和外部设备的数据交换由EMIF接口完成。该

2011-07-25 09:13:51

PDIUSBD12的并行接口时序较慢,只能达到2MB/s。这个速度相对于DSP来说比较低,而且有些地方不是简单地在程序中加入延时就可以调整,所以需要一个时序调整电路来完成它们之间的配合。1.2

2019-05-21 05:00:21

设计中的关键软硬件技术;同时以TMS320C549 CSP评估板为基础,设计完成了DSP与CompactFlash卡之间的接口电路,正确实现了DSP对CompactFlash卡的读写及数据管理等各种功能

2018-12-12 09:53:01

DSP的嵌入式系统与LAN91C111型自适应10Mb/s/100Mb/s嵌入式以太网控制的接口电路及软硬件实现方法。 TX INT:当TX completion FIFO不为空时置1e; TX

2019-06-12 05:00:08

在高频超声波数据采集系统中,很多高速A/D转换器往往不能直接与处理器相连接,这时就需要使用FIFO在处理器与A/D转换器之间架一座桥梁,FIFO的先入先出特性可以方便缓存大量的数据块。在基于ARM

2020-12-28 06:55:06

与ISA总线声卡的接口原理声卡的工作原理图1示出了声卡的基本工作原理:主机通过总线将数字化的声音信号以PCM方式送到数模转换器(D/A),将数字信号变成模拟的音频信号;同时又可以通过模数转换器(A/D)将

2018-12-14 10:57:58

~328μs),输出读信号,此时数据接口单元的写允许信号wr_fifo变为有效,同时外部A/D转换器的读允许信号也变为有效,此后ADC0804的数据端口上输出有效数据,在wr_clk的上升沿将A/D

2019-04-17 07:00:01

A/D转换,经过足够的时间后(T=327μs~328μs),输出读信号,此时数据接口单元的写允许信号wr_fifo变为有效,同时外部A/D转换器的读允许信号也变为有效,此后ADC0804的数据端口

2019-04-25 07:00:02

我的输入模拟量是在正负5V之间,频率小于120KHz,想要做一个数字功放,输出小于200KHz,接驱动1KW的负载,用DSP+FPGA控制现在第一步想要选择外部A/D转换芯片,初次设计,还望请各位学者说的详细些,谢谢!

2016-07-12 11:50:41

FIFO芯片是什么?如何利用FIFO去实现DSP间双向并行异步通讯?

2021-06-02 06:08:17

嗨,伙计们,最近,我正在开发一个USB项目,其中CY7C68013A-128AXC被用来通过奴隶FIFO接口与FPGA通信,在68013中,EP2被配置为512字节双缓冲Mulnual OFF

2019-03-01 14:17:46

的可编程逻辑器件EPM7256A完成对数据的缓存和传输的各种时序控制以及开关量采样时序、路数判别。采用FIFO器件作为高速A/D与DSP处理器间的数据缓冲,有效地提高了处理器的工作效率。

2020-12-31 07:52:43

C6727B,由于其片内集成dMAX模块,使得实现嵌入式FIFO成为可能。其实现嵌入式FIFO的本质就是将DSP的片内一段RAM空间设置成FIFO空间,FIFO和外部设备的数据交换由EMIF接口完成。该

2019-08-08 07:03:56

实时钟DS12887与DSP的接口设计摘要:讨论了并行实时钟DS12887 与DSP 之间的接口。介绍了DSP 通过时序模拟的方法实现对实时钟芯片DS12887 的读写访问,并给出了它们的接口

2009-11-03 15:03:04

现在在做一块主控板,板子搭载DSP的28335芯片,利用FPGA的飓风2代EP2C144芯片桥接100脚STM32F103,起初规划是用双口RAM通信,后来改用FIFO通信,现在的情况是,DSP

2014-08-29 11:11:37

DSP48A的SPARTAN 3A DSP FPGA之间存在什么形式的通信?它是基于公交车的吗?有仲裁吗?他们的沟通协议是什么?以上来自于谷歌翻译以下为原文What form

2019-06-28 06:19:32

因为FPGA管脚不太够,想问下CY7C68013A-56PVXI可以使用8bit FIFO数据接口吗?可以的话,FPGA连接的是低8bit(FD0~FD7) 还是高8bit(FD8~FD15)呢?

2024-02-27 08:18:39

用strstr提取两个0D0A之间的字符串 怎么提取啊

2019-03-06 00:40:09

怎么实现A/D数据采集接口的设计?

2021-04-20 07:19:20

; ②通过USB接口,实现PC机对DSP图像采集系统的操作与控制; ③实现图像数据在DSP摄像系统与PC机之间高速的双向传输。 基于以上几点可以看出,本方案最主要的特点是成本低廉且传输速度高

2019-06-19 05:00:08

FIFO芯片。芯片的存储空间是2K×9 bit,读写时间最小是10ns。其主要的控制管脚功能如表1所示。3.接口电路的CPLD实现通过上面的介绍,可以大致归纳出接口电路需要实现的主要功能如下:(1)将A/D

2019-05-23 05:01:08

与ISA总线声卡的接口原理2.1 声卡的工作原理图1示出了声卡的基本工作原理:主机通过总线将数字化的声音信号以PCM方式送到数模转换器(D/A),将数字信号变成模拟的音频信号;同时又可以通过模数转换器

2019-05-31 05:00:03

总线声卡的接口原理2.1声卡的工作原理图1示出了声卡的基本工作原理:主机通过总线将数字化的声音信号以PCM方式送到数模转换器(D/A),将数字信号变成模拟的音频信号;同时又可以通过模数转换器(A/D

2019-06-05 05:00:14

位接口模式,数据地址复用总线D0~D15与DSP总线XD0~XD15相连;DM9000A的写信号引脚与DSP的XWE0n相连;读信号引脚与DSP的读引脚相连;DM9000A的片选信号引脚与DSP

2019-06-18 05:00:11

输入缓冲区。CY7C68013A的,Slave FIFO接口模式如图6所示。3.2 EZ-USB FX2时序设计在本设计的FPGA中,设计了如图6的外部主控制器的功能逻辑。由于DSP端Linkport

2019-05-31 05:00:04

所有现代的定点和浮点DSP 引擎都具有一个串行接口或并行存储器接口。并行数据总线宽度等于DSP 的内部字长,对于大多数的定点处理器其字长通常为16 位。然而,在某些DSP 家庭中

2009-11-12 14:30:00 39

39 介绍了PCI 9054 接口芯片的性能及数据传输特点,提出了一种基于PCI 9054 外扩异步FIFO(先进先出)的FPGA(现场可编程门阵列)实现方法。由于PCI 9054 内部FIFO存储器主要用于数据

2010-01-06 15:20:10 44

44 实时钟DS12887 与DSP 的接口设计

摘要:讨论了并行实时钟DS12887 与DSP 之间的接口。介绍了DSP 通过时序模拟的方法实现对实时钟芯片DS12887 的读写访问,并给出了它们的接口设

2010-04-02 15:29:00 31

31 介绍了异步FIFO在Camera Link接口中的应用,将Camera Link接口中的帧有效信号FVAL和行有效信号LVAL引入到异步FIFO的设计中。分析了FPGA中设计异步FIFO的难点,解决了异步FIFO设计中存在的两

2010-07-28 16:08:06 32

32 【摘 要】 针对某脉冲警戒雷达设计了一种新的基于单倍FIFO存储空间的乒乓存储电路,实现了DSP与A/D、D/A之间的数据交换。 &

2009-05-10 20:02:41 721

721

基于FPGA的FIFO设计和应用

引 言

在利用DSP实现视频实时跟踪时,需要进行大量高速的图像采集。而DSP本身自带的FIFO并不足以支持系统中大量数据的暂时存储

2009-11-20 11:25:45 2127

2127

摘要:介绍了TMS320F2407A DSP芯片上USB接口的实现,DSP与PC之间的高速通信一直是DSP应用的关键问题,文中分析了PC与DSP通过USB接口通信的原理,使用AN2131Q芯片实现了USB接口,说明了软件和硬件设计的框架。 关键词:USB;DSP;固件

2011-02-25 16:42:45 144

144 摘要:随着数字信息的发展,对数据处理能力的要求日益提高,越来越多地需要利用多个DSP协调工作.该文提出一种利用软FIFO实现多个DSP间的高速通信的方案,并进行了仿真试验.仿真结果表明该方案是可行有效的. 关键词:先进先出队列;数字信号处理;VHDL;现场可编程门

2011-02-25 23:12:18 33

33 详细介绍了TMS320C6205读取FIFO中数据的速度以及如何设置EMIF的CExCTL寄存器的接口时序。

2011-11-30 11:45:00 3787

3787

文中给出了异步FIFO的实现代码和FPGA与DSP的硬件连接电路。经验证,利用异步FIFO的方法,在FPGA与DSP通信中的应用,具有传输速度快、稳定可靠、实现方便的优点。

2011-12-12 14:28:22 51

51 DSP接口,从入门到精通只DSP接口,参考下。

2016-01-19 11:30:44 59

59 自定义fifo接口控制器,利用sopc builder实现。

2016-03-22 14:09:34 1

1 异步FIFO在FPGA与DSP通信中的运用

2016-05-19 11:17:11 0

0 大多数的高速模数转换器不能够直接和DSP 相连。一个比较好的解决办法是使用FIFO 作为输入缓冲。FIFO 可以通过C6000 系列的外部存储器接口( EMIF) 与TMS320C6000 系列

2017-05-31 16:09:36 3

3 基于异步FIFO在FPGA与DSP通信中的运用

2017-10-19 10:30:56 10

10 基于FIFO的高速A_D和DSP接口设计

2017-10-19 14:10:23 9

9 介绍了利用CYPRESS公司的FIFO芯片CY7C419实现DSP间双向并行异步通讯的方法,该方法简单实用,速度快,特别适用于小数据量的数据相互传送。文中给出了CY7C419的引脚功能以及用FIFO

2017-10-25 11:35:25 0

0 摘要 利用异步FIFO实现FPGA与DSP进行数据通信的方案。FPGA在写时钟的控制下将数据写入FIFO,再与DSP进行握手后,DSP通过EMIFA接口将数据读入。文中给出了异步FIFO的实现

2017-10-30 11:48:44 1

1 据量的数据交换及通讯来说,要提高DSP的工作效率,不仅要求并行接口的响应快,而且必须采用异步方式以免相互等待。本文介绍了采用CYPRESS公司的FIFO芯片CY7C419来实现DSP间的双向并行异步通讯接口。该方法不仅比用TTL锁存器的方式速度快,而且译码逻

2017-11-01 11:34:19 5

5 在现代的集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟。多时钟域带来的一个问题就是,如何设计异步时钟之间的接口电路。异步FIFO(Firstln F irsto ut)是解决这个

2018-02-07 14:22:54 0

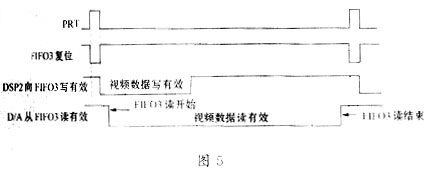

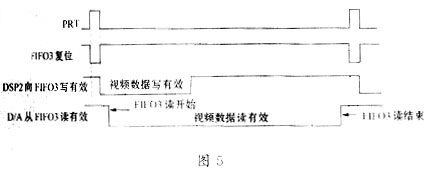

0 本系统是基于DSP的数字图像处理系统,总体结构设计如图1所示。首先CCD摄像机拍摄视频图像,输出标准PAL制式视频信号,输入到视频解码芯片TVP5150中,TVP5150将模拟图像信号转换为数字图像信号送入FIFO中,本系统采用AL422B。

2018-02-26 19:57:54 2336

2336

本文档的主要内容详细介绍的是DSP2833X FIFO的程序和资料合集免费下载。

2019-03-11 08:00:00 1

1 FIFO队列不对报文进行分类,当报文进入接口的速度大于接口能发送的速度时,FIFO按报文到达接口的先后顺序让报文进入队列,同时,FIFO在队列的出口让报文按进队的顺序出队,先进的报文将先出队,后进的报文将后出队。

2019-11-29 07:04:00 4345

4345 。DSP用于实现USB协议,通过DSP编程实现DSP数据通过USB接口与PC机通信,且USB芯片的描述符写入及各种命令状态的处理均通过DSP编程实现。

2019-06-19 15:17:17 1813

1813

介绍了TI公司TMS320C67系列DSP的EMIF(外部存储器接口)与异步FIFO(先进先出)存储器的硬件接口设计,着重描述了用EDMA(扩展的直接存储器访问)方式读取FIFO存储器数据的软件设计

2019-07-31 16:40:47 20

20 EE-144:在两个ADSP-2191 DSP之间创建主从SPI接口

2021-05-24 15:14:48 1

1 基于McBSP实现DSP与串行Flash之间的接口通讯(android嵌入式开发教程)-该文档为基于McBSP实现DSP与串行Flash之间的接口通讯总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-08-04 11:12:54 10

10 FIFO的使用非常广泛,一般用于不同时钟域之间的数据传输,或者用于不同数据宽度之间的数据匹配。在实际的工程应用,可以根据需要自己写FIFO。不考虑资源的情况下,也可以使用Xilinx提供的IP核来完成。

2022-08-14 10:49:47 3567

3567 同步FIFO的意思是说FIFO的读写时钟是同一个时钟,不同于异步FIFO,异步FIFO的读写时钟是完全异步的。同步FIFO的对外接口包括时钟,清零,读请求,写请求,数据输入总线,数据输出总线,空以及满信号。

2022-11-01 09:58:16 1189

1189 位宽变换:对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

2022-11-09 20:00:03 1253

1253 异步FIFO主要由五部分组成:写控制端、读控制端、FIFO Memory和两个时钟同步端

2023-05-26 16:17:20 911

911

FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。

2023-06-14 08:59:29 223

223

再由FIFO的半满信号HF作为外部中断信号,当FIFO存储器半满时,便可由HF经逻辑处理后向DSP发出中断申请INT4。由于外部FIFO占用着DSP的CE0空间,所以读信号的逻辑关系为:R=CE0+ARE,启动DSP 的EDMA(Enhanced Direct Memory Access)通道传输,可将FIFO中的数据读入内部RAM中,这样,在FIFO输出数据的同时,也将A/D转换的数据写入了FIFO中,从而达到了同时读写的目的。使用EDMA方式传输数据的好处在于:EDMA控制器可以独立于CPU工作,从而可方便地实现片内存储器、片内外设以及外部存储空间之间的数据转移。由外部中断INT4启动EDMA传输,可以大大提高传输速率和CPU的工作效率。DSP读完2048个数据后即开始处理,处理完后便可以在一次扫描结束与下一次扫描尚未开始的时间内将16Bit计算结果数据输出,总的处理时间为一个帧周期。FIFO的写信号可由FPGA产生,并可在A/D转换结束后向FIFO写数据。另外,在每一帧处理之后,还应由FPGA输出控制信号以对FIFO进行初始化,然后重新输入下一帧数据。

再由FIFO的半满信号HF作为外部中断信号,当FIFO存储器半满时,便可由HF经逻辑处理后向DSP发出中断申请INT4。由于外部FIFO占用着DSP的CE0空间,所以读信号的逻辑关系为:R=CE0+ARE,启动DSP 的EDMA(Enhanced Direct Memory Access)通道传输,可将FIFO中的数据读入内部RAM中,这样,在FIFO输出数据的同时,也将A/D转换的数据写入了FIFO中,从而达到了同时读写的目的。使用EDMA方式传输数据的好处在于:EDMA控制器可以独立于CPU工作,从而可方便地实现片内存储器、片内外设以及外部存储空间之间的数据转移。由外部中断INT4启动EDMA传输,可以大大提高传输速率和CPU的工作效率。DSP读完2048个数据后即开始处理,处理完后便可以在一次扫描结束与下一次扫描尚未开始的时间内将16Bit计算结果数据输出,总的处理时间为一个帧周期。FIFO的写信号可由FPGA产生,并可在A/D转换结束后向FIFO写数据。另外,在每一帧处理之后,还应由FPGA输出控制信号以对FIFO进行初始化,然后重新输入下一帧数据。 外设时钟ECLK为90MHz,所以,最后设定SETUP=1、STROBE=2、HOLD=2来满足DSP与异步FIFO接口的要求。

外设时钟ECLK为90MHz,所以,最后设定SETUP=1、STROBE=2、HOLD=2来满足DSP与异步FIFO接口的要求。 电子发烧友App

电子发烧友App

评论