引言

DVR(Digital Video Recorder,数字视频录像机)由于采用硬盘进行图像存储处理,也被称为硬盘录像机。DVR采用的是数字记录技术,在图像处理、图像储存、检索、备份、以及网络传递、远程控制等方面也远远优于模拟监控设备。在国内,DVR经过十几年的应用和快速发展,逐步呈现出高清化、智能化、个性化趋势。当然随之而来的也是DVR价格的白热化竞争。如何提供高清晰、高稳定性、低层本DVR产品成为摆在每个DVR企业面前的首要课题。莱迪思凭借其多年的视频领域开发、应用经验,提出了基于高性能、高稳定性、低成本LatticeECP3 FPGA在多通道HD-SDI DVR应用中的低成本解决方案。本文详细介绍了如何采用特定的FPGA (Field-Programmable Gate Array) 系列- LatticeECP3,实现多通道、低成本HD-SDI(High Definition Serial Digital Interface) DVR系统中的HD-SDI视频数据解析、缩放、叠加、抽帧、视频切换以及接口转换。

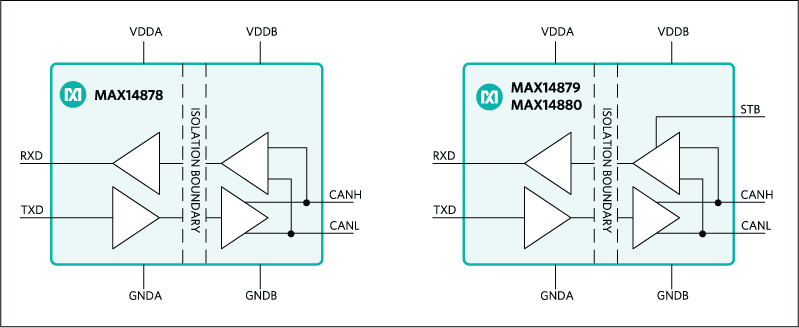

FPGA VS 分立SDI接收芯片

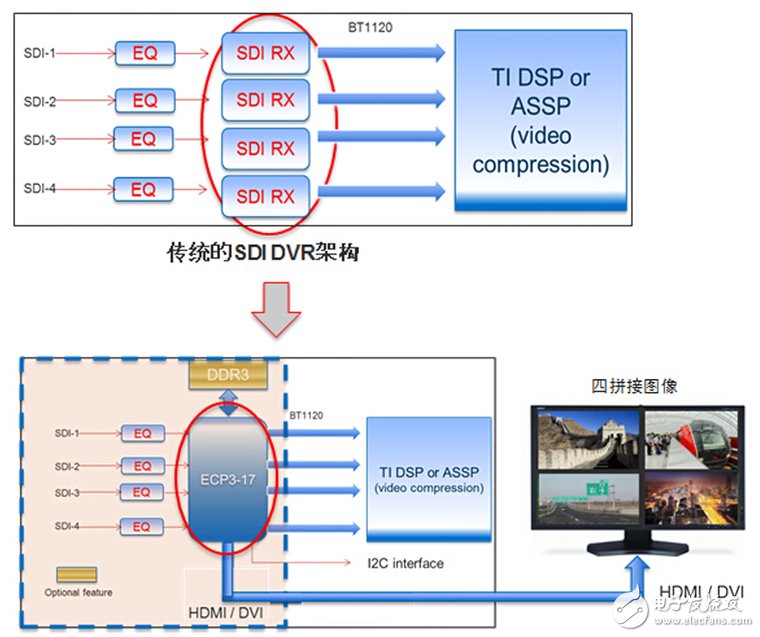

DVR系统应用中,由于传统的DSP (Digital Signal Processor)或者ASSP(Application Specific Standard Parts)并不能直接支持SDI接口,经常采用分立EQ+分立SDI接收芯片完成接口转换,再传输至DSP或者ASSP进行后期的视频处理。面临的问题就是当支持多通道HD-SDI时,布线变得非常复杂、分立器件占用PCB面积大、BOM(Bill of Material)成本提高,这将直接导致DVR产品成本大幅上升。由于LatticeECP3 FPGA系列具有多达16个通道的高速串行Serdes接口,并且支持拥有自主知识产权的三速率SDI IP(IntelligentProperty)核(标清SD-SDI、高清HD-SDI、3G-SDI)完成SDI数据的收发。对于SDI接收模块来说,输出的接口是标准的BT1120格式,不用任何处理即可输出给下一级DSP芯片处理。因此,采用其中的一个低成本系列ECP3-17EA就可以取代四个分立的SDI接收芯片,完成四路HD-SDI到BT120的接口转换,其中不需要外挂任何帧数据缓存单元。当然,客户在实现四路数据直通的同时也可以选择莱迪思提供的PCIE IP核、HDMI IP核、DVI IP核以及桥接参考设计实现其他输出接口。这大大降低了BOM成本以及PCB的尺寸。同时LatticeECP3 FPGA支持128bit的AES加密功能可以更好的保护客户的自有知识产权。

多通道低帧率HD-SDI视频处理参考设计

低成本的LatticeECP3 FPGA除了提供HD-SDI IP核完成数据收、发功能以外,还支持诸如LVDS7-to-1、Sub LVDS、Mini LVDS、HDMI和DVI、MIPI等丰富的视频处理接口。同时对于视频处理中不可或缺的帧数据存储提供了线速率高达800Mbps的DDR3(3rd Generation Double Data Rate)SDRAM(Synchronous Dynamic Random Access Memory)接口、IP核。这些特性确保了LatticeECP3 FPGA提供了更多的灵活性,支持更多的特性,定制更多的个性化功能,为客户需求提供快速反应,缩短开发周期使得客户的产品快速走向市场。经过大量测试的IP核、成熟的参考设计包括基于多通道的视频缩放、多通道视频叠加、OSD(On Screen Display)菜单定制、帧率转换、帧率抽取以及接口转换功能等等。简单、低速的I2C接口完成这些特定功能、模式的配置以及切换。在下面的内容中,我们会详细介绍一个LatticeECP3 FPGA在八通道低帧率的HD-SDI DVR系统中的成功应用。

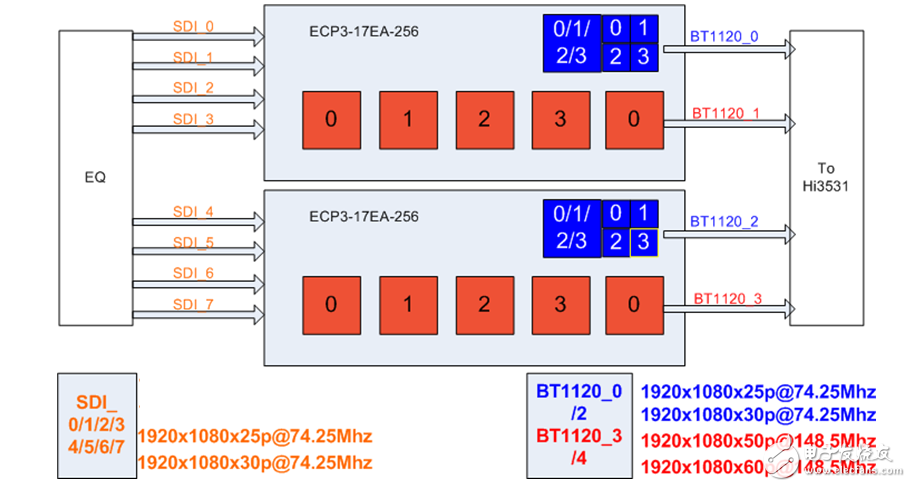

图示(八通道 HD-SDI DVR架构)是一个八通道的HD-SDI系统,通常需要八颗独立的SDI接收芯片、两颗Hi3531完成视频接收处理。这里采用两颗LatticeECP3-17EA FPGA 加一颗Hi3531就完成了HD-SDI到BT1120的桥接功能设计。同时为了降低Hi3531的处理任务,LatticeECP3-17EA FPGA对输入的四路HD-SDI数据进行了预处理。图中BT1120_0、BT1120_2输出的是四路拼接数据或者是四路数据中的某一路数据,该通道称之为实时显示通道,此时输出帧率与输入帧率是相同的,为1080p 25帧/秒或者30帧/秒。BT1120_1、BT1120_3用于录像通道,输出的是四路数据抽取后的数据,按照0、1、2、3、0顺序排列输出。需要注意的是输入的每路数据为1080p 25帧/秒或者30帧/秒,四路共计100帧/秒或者120帧/秒,输出进行了抽帧处理,只有60帧/秒。上述的预处理在不影响视频质量的情况下,满足系统需求同时无疑大大降低了Hi3531的处理任务,有效降低了板级功耗以及发热量。

八通道HD-SDI DVR 架构

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处。

用户评论(0)