。而射频芯片作为小基站的重要组成部分,在测试上也因此面临着不小的挑战。4月20日,在由电子发烧友网举办的2022第三届5G技术创新研讨会上,爱德万测试技术经理孙佳焱为大家了分享了《5G小基站将大量部署,如何面对芯片的量产测试挑战》。 什

2022-04-22 00:16:00 3654

3654 ,然后通过外部物理连接回环TX-->RX测试误码率来验证链路的信号完整性,所以我想进行如下测试:

测试路径: FPGA --> DSP SRIO SerDes -->

2018-06-21 06:25:29

和Camera Link2.支持DDR3-64bit-1600MHz和DDR4-72bit-2400MHz内存接口3.支持PCIe链路速率:PCIe 1.0、PCIe 2.0、PCIe 3.0

2024-03-13 13:59:45

5Gbps高速测试系统的基本技术有哪些?

2021-05-28 07:02:17

系统(SC-FDMA)类似研究人员和工程师在测试5G设备时,面临着创建、分布和生成5G波形的新挑战。工程师需要处理高度复杂且符合标准的上行链路和下行链路信号,而且这些信号的带宽要比以前的信号大得多

2019-08-16 14:03:51

Jitter 、CM Jitter 等)及PeRT3 能够实现的功能及连接示意图: PCIE 3.0 接收端测试抖动源校准连接示意图: 来自于PCIE 3.0 规范的接收机测试的抖动源校准连接图

2018-09-26 17:33:30

代替8b/10b编码,使得编码效率大幅提高;另一个是使用动态均衡技术,来代替先前代的静态均衡技术。 这里聚焦于PCIe 3.0和4.0中的动态均衡技术,介绍其原理、实现及其相关的一致性测试 。这样一种

2020-11-25 06:19:43

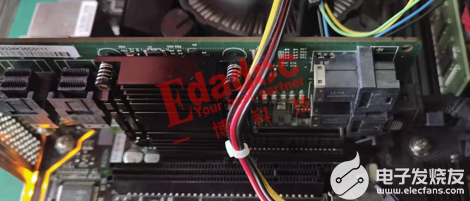

的 16 通道 PCIe Gen3 插槽兼容的 PCIe Gen3 转接卡扩展 PCIe Gen-3 子系统的 PCB 线迹长度提高信号完整性和系统稳健性无缝兼容主板主机与端点卡之间的链路训练经过验证的设计,提供兼容性测试报告

2022-09-21 07:43:27

基于VU9P的双路5Gsps AD 双路6Gsps DA PCIe数据卡一、板卡概述 基于XCVU9P的5Gsps AD DA收发PCIe板卡。该板卡要求符合PCIe 3.0标准,包含一片

2022-01-25 11:36:30

本帖最后由 一只耳朵怪 于 2018-6-25 11:36 编辑

大家新年好!请教个主机重启后的PCIe重新建链问题。我想实现主机重启后,dsp 6670自动恢复PCIe连接,解决方法有以下2

2018-06-25 03:06:56

高速串行总线的特点是什么?测试高速串行总线面临哪些挑战?如何应对这些测试挑战?

2021-05-10 07:00:10

轻松实现高速串行I/OFPGA应用设计者指南输入/输出(I/O)在计算机和工业应用中一直扮演着关键角色。但是,随着信号处理越来越复杂,I/O通信会变得不可靠。在早期的并行I/O总线中,接口的数据对齐

2020-01-02 12:12:28

了SFP+ DAC自动化测试系统。接下来我们将范围进一步扩展到100G QSFP28 DAC产品,该系统支持IEEE802.3bj协议相关参数及指标,被测电缆一次即可自动完成所有参数选项测试并生成测试报告,可为易飞扬的高速电缆产品把好质量关。`

2017-04-18 15:47:04

高速串行链路系统对信号的影响是什么?常用的补偿技术有哪些?

2021-06-10 06:20:34

计算机主板上的典型总线结构有什么共同点?高速串行数据链路一致性测试的难点有哪些,该如何应对?

2021-04-09 06:47:14

及显示屏作为标准配置。倒车事故每年都会造成数百人死亡和数千人受伤,该条例旨在减少这一伤亡数字。这样无疑将提高安全性,提升驾驶体验,但所有这些摄像头的增加也将给汽车系统设计人员带来新的挑战。传送高速视频的链路

2018-09-17 16:10:00

亲爱的大家,我们购买了评估套件AC701,因为我们对使用7系列FPGA和PCIe IF的可能性感兴趣。我们的目标是在板上实现应用,并通过PCIe链路在主机PC上观察此应用的结果。这样我们将通过

2019-09-10 07:56:36

一、产品概述 基于PCIe的一款分布式高速数据采集系统,实现多路AD的数据采集,并通过PCIe传输到存储计算服务器,实现信号的分析、存储。

产品固化FPGA逻辑,适配2路1Gsps/2路

2023-12-11 11:36:40

随着Bluetooth®5的提速,您是否也想要抢占先机,快人一步?现在,工程师可以借助TI针对单模Bluetooth低功耗应用、首款通过全面认证的Bluetooth5协议栈轻松支持高速模式

2019-03-20 06:45:10

工程师和物理布局设计师面临着更大的挑战。很多视频系统都采用多功能FPGA和多传输率SDI集成电路,以支持高性能专业视频在长距离的传输。FPGA需要高密度、细迹线宽度的传输,而高速模拟SDI传输需要阻抗匹配和信号保真。那么FPGA/SDI子系统中的高速板布局挑需要面对哪些挑战?具体该怎么做呢?

2019-08-06 07:23:31

大容量、高速率和低功耗已成为FPGA的发展重点。嵌入式逻辑分析工具无法满足通用性要求,外部测试工具可以把FPGA内部信号与实际电路联合起来观察系统真实运行情况。随着FPGA技术的发展,大容量、高速

2019-08-07 07:50:15

如何证明产品测试与HDMI标准所定义的测试一致?HDMI V1.3物理层一致性测试中面临的挑战有哪些?示波器自带测试软件如何能在保证结果可靠的前提下实现效率的飞跃?以及这些软件如何大幅提高测试的自动化程度?

2021-04-15 06:21:20

Keysight 81250 用于平面显示器链路测试

2019-08-09 11:15:12

随着SerDes芯片集成度,复杂度,传输速率的不断提高,传统的自动化测试系统已经无法满足SerDes测试速率需求。为解决该测试难题,通过Nautilus UDI方案的导入,成功得实现了32 Gbps

2021-05-10 06:58:55

电路连接图进行比对,准确判断故障位置并把故障情况录入数据文件或故障数据库;5.测试诊断结果报告模块,显示、打印或者存储PCB的测试诊断结果。结语基于PLD和多路选择开关ADG732的电路板自动测试仪实现

2012-07-25 19:57:21

本文讨论的是 RFID 通信系统的设计师所面对的测试挑战:监管测试、标准一致性和优化。

2021-04-09 06:49:58

接收端链路均衡测试(Rx LEQ)进入环回模式进行误码率测试

2020-12-02 06:49:35

的环节,位于产业链的上游,对于产品研发和产业化起着非常关键的作用。并且由于 LTE和之前的系统在空中接口上存在很大的不同,对TD-LTE测试仪表的需求已经涵盖了整个产业链的各个阶段。所以测试就提出了一些新的挑战跟要求。

2019-08-08 07:18:41

:https://bbs.elecfans.com/jishu_941738_1_1.html本月任务挑战书:自动视力测试仪任务描述:挑战者需基于上述指定软硬件,在为期三周的时间内制作一个自动视力测试

2016-09-19 10:32:27

的EtherCAT总线运动控制卡,可选6-64轴运动控制,支持8路高速数字输入,8路高速数字输出,可实现多轴同步控制和高速数据传输,集成丰富的运动控制功能,包含多轴点位运动、位置锁存、直线插补,圆弧插补,连续

2024-01-24 09:48:21

,信噪比与误码率,以及EMI/EMC等重要指标。罗德与施瓦茨公司将举办一场在线研讨会,针对电源完整性测试中的相关挑战,介绍最新电源完整性测试方案,讲解如何助力工程师轻松应对和完成相关测试和分析。会议主题

2017-08-11 15:48:10

本文介绍自动化测试的 7 个步骤:改进自动化测试过程,定义需求,验证概念,支持产品的可测试性,具有可延续性的设计( design for sustainability ),有计划的部署和面对成功的挑战。按照以上 7 个步骤,安排你的人员、工具和制定你的自动化测试项目计划,你将会通往一条成功之路。

2019-07-18 07:42:32

),有计划的部署和面对成功的挑战。按照以上 7 个步骤,安排你的人员、工具和制定你的自动化测试项目计划,你将会通往一条成功之路。

2019-07-19 06:12:56

首要关注的焦点。这是特别现实的问题,因为LTE代表了无线接入技术的一个重大变化,其实现和部署都是一个巨大的挑战。从器件到基站到终端用户服务,整个LTE设备供应链对测试的需求非常大。从GSM/UMTS自然

2019-06-03 07:06:26

什么是GaN?如何面对GaN在测试方面的挑战?

2021-05-06 07:52:03

其他单元的仿真测试提供配套的功能。ADLINK公司PCI-9846高分辨率高速数据采集卡在武器数据链测试系统中,以其宽动态范围、板载512MB内存及不受PCI总线速率限制的突出特点,助力武器数据链测试

2019-08-29 06:47:59

使用Keysight E5910A串行链路优化工具测试和优化高速串行链路

2019-10-15 08:49:27

,PTS宣布推出了基于阿里双11全链路压测平台的铂金版。点此查看原文:http://click.aliyun.com/m/41269/阿里云性能测试(Performance Testing Service

2018-01-30 14:13:04

Express 总线的 4 路 10G 双缓冲光纤通道适配器,板卡具有 4 通道 SFP+万兆光纤接口,x8 PCIE 主机接口,具有 2 组 64 位 DDR3 SDRAM 作为高速缓存,可以实现

2017-03-11 14:05:16

描述JESD204B 链路是数据转换器数字接口的最新趋势。这些链路利用高速串行数字技术提供很大的益处(包括增大的信道密度)。此参考设计解决了其中一个采用新接口的挑战:理解并设计链路延迟。一个示例实现

2018-11-21 16:51:43

的损耗,接收端会采用DFE/FFE等方法来进行均衡,一些比较高速率的标准如PCIE 4.0/5.0,SAS4等还会采用FEC来进行纠错,当然接收端还需要CDR来从串行信号里面进行时钟恢复得到同步时钟来对信号进行采样。图1:高速串行链路的基本架构

2019-07-18 06:33:33

一条物理链路的速度从600Mbps到10Gbps,高速I/O的测试和验证更成为传统专注于FPGA内部逻辑设计的设计人员所面临的巨大挑战。这些挑战使设计人员非常容易地将绝大部分设计时间放在调试和检验设计上。

2019-08-29 07:59:05

描述千兆位以太网链路聚合器参考设计采用了 TLK10081 器件,这是一种多速率链路聚合器,用于高速双向点对点数据传输系统,可将低速串行链路多路复用为高速串行链路,从而降低物理链路的数目。此

2018-08-03 08:32:03

FPGAXCKU060-FFVA1156-2-I架构,支持PCIE Gen3 x8模式的高速信号处理板卡,搭配两路40G QSFP+接口,两组64-bit DDR4,每组容量8Gbyte,可稳定运行在2400MT

2022-07-11 11:35:54

如何实现自动重复配置和FPGA测试,将FPGA较快速度的在线配置和快速测试结合起来。

2021-04-08 06:14:46

如何DigRF技术进行测试?DigRF技术生产测试的挑战有哪些?

2021-04-15 06:05:31

嗨,我需要测试PCIE带宽。我可以使用vc707-pcie-rdf0161-14.4.zip进行测试吗?谢谢

2019-09-12 09:23:39

如何克服ACS测试系统和SMU的可靠性测试挑战?

2021-05-11 06:11:18

如何去面对高速高密度PCB设计的新挑战?

2021-04-23 06:18:11

自动化测试系统的设计挑战有哪些?如何去设计新一代自动化测试系统?

2021-05-11 06:52:57

TD-LTE、FDD-LTE和LTE-Advanced(LTE-A)无线技术使用了几种不同的多种输入多路输出(MIMO)技术。鉴于MIMO系统的复杂性正在日益提高,因此相关的测试方法也将更具挑战性。那么,如何选择LTE系统测试方法,存在哪些挑战?

2019-02-28 11:18:42

将带来美好的终端使用者体验,但同时也让5G系统开发工程师面临许多有趣的挑战。怎么面对5G波形的测试挑战?这个问题值得思考。

2019-08-09 06:52:28

如何使用宽频率范围矢量网络分析仪去应对高速互联测试的挑战?

2021-04-30 07:25:40

钥匙式测试解决方案,提供清楚简明的特性分析报告。 PCIe4.0技术提高了数据速率,同时也带来了许多全新的测试挑战,如通道损耗大大提高,总抖动预算缩紧,链路培训和定时要求更加复杂。随着设计裕量缩小

2016-07-07 17:28:56

作者:John Johnson,德州仪器 本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成

2018-09-19 14:23:47

本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成了各种委员会和标准机构,根据其开发标准的目标

2022-11-23 06:59:24

的要求。电子供应链作为电子信息制造业其中的重要的一环,面对产业的发展与结构升级,机会与挑战并存。

从电子产业链的上中下游来看,上游主要是原材料及电子元器件供应商,中游是电子硬件模块的生产与制造,包括

2023-09-15 11:37:37

武器系统其他单元的仿真测试提供配套的功能。ADLINK公司PCI-9846高分辨率高速数据采集卡在武器数据链测试系统中,以其宽动态范围、板载512 MB内存及不受PCI总线速率限制的突出特点,助力武器数据链测试,满足了并行、动态及仿真测试等复杂应用需求,成为测试系统中的技术亮点,提升了测试技术水平。

2019-08-23 07:00:27

之一的毫米波技术已成为目前标准组织及产业链各方研究和讨论的重点,毫米波将会给未来5G终端的实现带来诸多的技术挑战,同时毫米波终端的测试方案也将不同于目前的终端。本文将对毫米波频谱划分近况,毫米波终端技术实现挑战及测试方案进行介绍及分析。

2021-01-08 07:49:38

连接头的质量、施工工艺和现场环境,所以光纤链路测试至关重要。光纤链路测试其主要目的是检测光纤链路的连接质量,减少故障因素以及存在故障时找出光纤的故障点,从而进一步查找故障原因。针对光纤链路的测试

2015-02-12 16:02:07

的 16 通道 PCIe Gen3 插槽兼容的 PCIe Gen3 转接卡扩展 PCIe Gen-3 子系统的 PCB 线迹长度提高信号完整性和系统稳健性无缝兼容主板主机与端点卡之间的链路训练经过验证的设计,提供兼容性测试报告`

2015-05-08 11:31:58

AD8170-EB,用于视频路由和多路复用系统的单路2:1模拟多路复用器评估板。 AD8170评估板经过精心布局和测试,可演示器件的指定高速性能

2020-06-17 16:47:30

开关信号和要执行测试的特点是什么设计自动化测试系统电压开关中的常见挑战

2021-04-09 06:21:00

为了克服测试方法和测试人员给绝缘耐压测试结果带来的误差,提出了一种智能化多路绝缘耐压自动测试系统的设计方法。介绍了该系统的工作原理、硬件组成及软件实现。系统采

2009-03-13 11:25:08 20

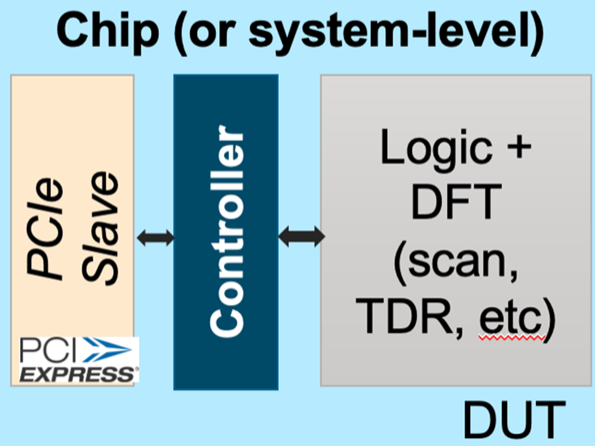

20 芯片间的互连速率已经达到GHz量级,相比较于低速互连,高速互连的测试遇到了新的挑战。本文探讨了高速互连测试的难点,传统互连测试方法的不足,进而介绍了互连内建自测试(I

2010-07-31 17:00:16 15

15 主要内容一、为什么需要做自动测试?二、EMI自动测试系统设计三、EMS自动测试系统设计四、EMC自动测试系统集成实例五、手机EMI自动测试实现

2010-09-21 11:29:23 62

62

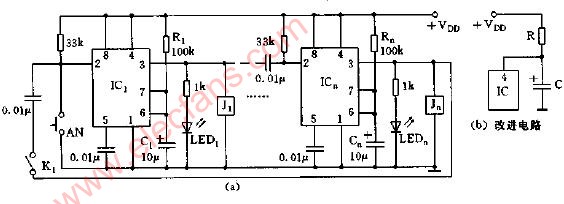

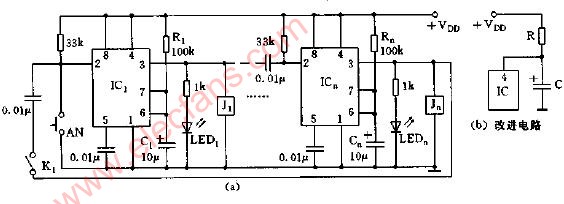

多路温度测试电路图

2009-05-30 13:49:25 474

474

叙述了测试系统的硬件设计思想并给出了完成自动化测试、软件设计方法及组建方案。测试结果表明,该系统能够实现三轴光纤陀螺测试全程自动化,节约了成本,提高了测试效率。

2012-03-01 15:51:10 37

37 主要介绍了 Parlay 应用服务器的 API 接口, 提出了一个简单的基于白盒测试的自动化测试平台实现方案, 并详细介绍了该方案的基本设计思想、总体结构、测试用例的实现方法, 以及该平台的工作机制。

2017-09-08 15:07:51 5

5 本文档内容介绍了高速数字总线技术发展趋势及测试挑战。

2017-09-15 15:36:05 7

7 高性能以太网芯片W5500,实现对阀数据的在线采集、输出、保存及打印。以某种农机专用且已知性能完好的负载敏感多路阀为测试对象,根据测试结果判断测试系统性能及被测负载敏感多路阀具体参数。系统测试结果表明,所设计测试系统稳定可靠,为

2018-03-22 10:24:40 0

0 如何面对这些接口的演进以及验证方面的挑战?12月22号,安立、泰克和GRL三家技术专家联手,与业内工程师共话 PCIe/USB/DP/TBT的演进与测试。

2020-12-28 10:19:12 771

771 PCIE信号的一致性测试从来都是业界的一个重点和难点,本期借着一个电脑主板的debug案例,高速先生向大家介绍下PCIE一致性测试的过程! 相信不少酷爱PCB设计(吃ji游戏)的粉丝们都知道一部

2022-02-14 17:24:23 13519

13519

从事FPGA开发无论是仿真还是上板验证,总少不了各种各样的case遍历,手动执行起来就太麻烦了。尤其像从事FPGA加速行业来说,CPU与FPGA版卡的交互和测试基本基于PCIe来实现,而软件有大量

2022-05-20 14:47:19 2407

2407 网络研讨会 高速接口测试:PCIe5.0测试方案 11月24日 1340 随着处理器技术发展,个人计算机以及工作服务器,在互连网领域对高速数据传输质量要求的与日俱增,采用差分信号进行串行通信

2022-11-15 07:20:09 1664

1664 差分探头是一种常用的测试仪器,在PCIE测试中也有广泛的应用。本文将介绍差分探头在PCIE测试上的应用及其优势。

2023-05-11 10:54:14 451

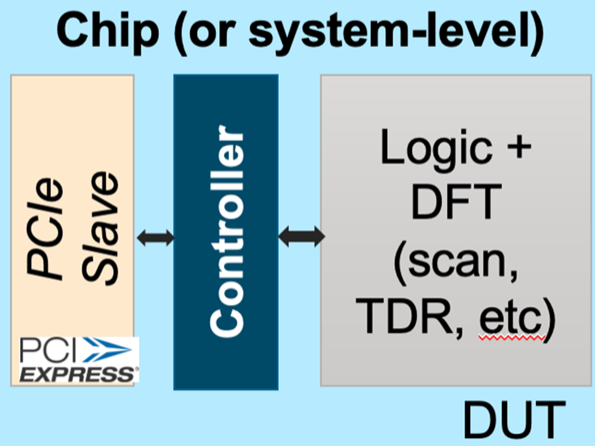

451 更容易处理。得益于 EDA 社区的创新,可测试性设计 (DFT) 和自动测试模式生成 (ATPG) 为 IC 测试 的挑战带来了丰富的方法。

2023-05-24 18:05:06 983

983

装备 (ATE),结合高端 ATE 的高质量资源、砂件设计技水及测试算法开发,不仪可以保证高速信号测试位输的质量,还可以实现对高速信号芯片智能化,自动化的全面性测试评估。图所示的是高速信号从ATE输出端到被测芯片引脚的变化。

2023-06-02 13:43:05 1045

1045

电子发烧友App

电子发烧友App

评论