一、前言 网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线

2020-10-15 04:15:01 20075

20075

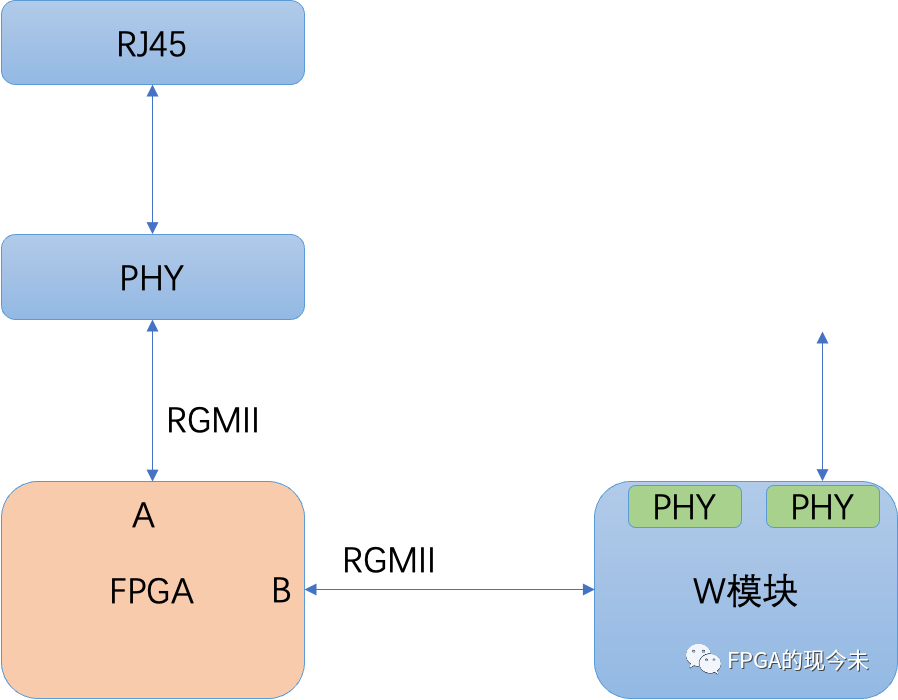

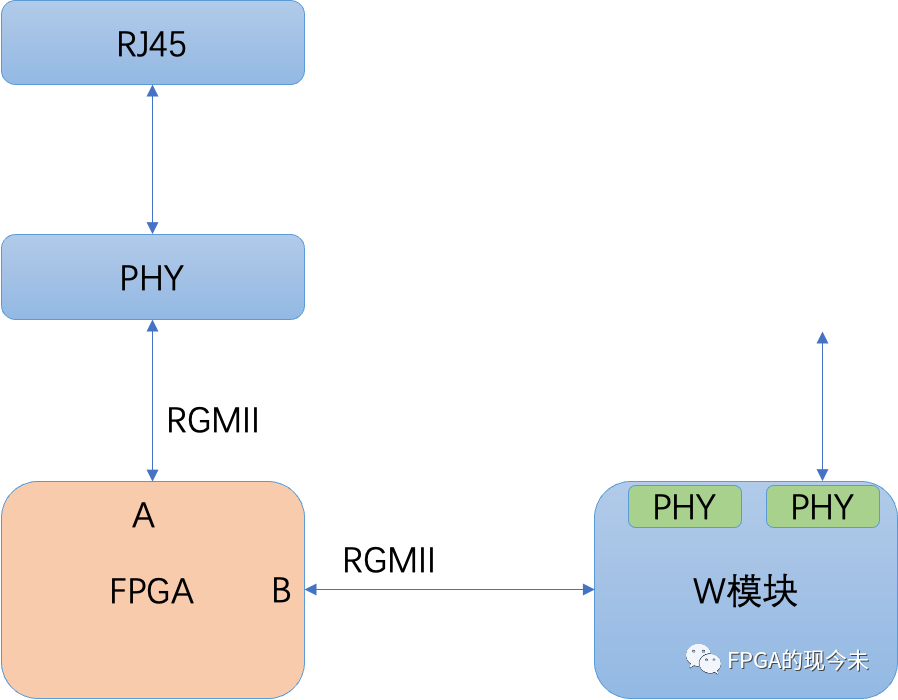

最近项目中,FPGA通过多个RGMII接口与其他设备通信,在通信的过程中,有一个RGMII接口对端设备始终无法驱动,最后通过共享一个PHY,时分复用的形式来“解决”该问题

2023-11-27 16:47:11 3048

3048

[88E1111S 千兆网phy芯片 支持GMII,RGMII,MII等接口 支持光纤接口 具备4个GMII时钟模式 支持自适应功能 超低功耗模式 功率降低模式 MDC/MDIO

2010-05-17 10:28:02

88E1111是一款功能强大的网卡芯片,使用的也非常广泛,前段时间一块板子上用到这一块88E1111,硬件做好了之后,运行网络通信程序就是无法通信,因为是DSP连接88E1111到千兆网口,DSP端

2019-05-22 07:27:38

在做嵌入式开发的时候,经常会用到网络通信。网络通信也是属于进程间的通信的一种方式,他的特点是跨主机通信。 主要的作用:利用网络通信远程控制嵌入式设备(应用例子:智能家居,远程监控,智慧校园,物联网

2021-12-23 06:45:47

网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线位宽小,可以

2023-06-06 15:43:13

一、前言网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线位宽

2021-07-07 08:30:00

一、前言 网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线位

2021-07-29 06:39:30

在LABVIEW中实现网络通信的几种方法1 引言 随着计算机技术、大规模集成电路、通信技术等的飞速发展,仪器系统与计算机软件技术紧密结合,使得传统仪器的概念得以突破,出现了一种全新的仪器概念

2014-12-12 18:02:17

---- FM1@DTSEC3----88E1512地址:0 ---FSL_MDIO0:2.EC2---RGMII----FM1@DTSEC 4-----88E1512 addr:1 ---- FSL_MDIO0

2023-04-03 07:41:34

本次实验使用开发板是美国Marvell公司生产的SOHO级网络通信微处理器芯片88E6218。开发环境是Ubuntu12.04,内核是UCLinux。1.使用串口本次课程主要是了解uart

2021-12-16 07:54:29

本帖最后由 一语奔驰 于 2016-11-25 15:18 编辑

我ZYNQ外接的PHY是88E1512,现在有一个系统,外接的是88E1510的PHY,但是我想使用88E1512来实现光口

2016-11-25 14:21:28

labviewUDP 网络通信

2012-05-25 16:49:40

非常实用的labview TCP网络通信教程 欢迎下载

2021-01-06 17:00:43

labview网络通信

2015-02-17 11:26:21

用labview建立网络通信时,可否只建立labview客户端而不建立labview服务端直接从网络服务器上读取信息?应该怎么实现?

2014-03-01 18:19:38

介绍了该系统的软硬件设计方法。关键词:光纤;千兆网口;DSP;88E1111;C6455引言 遵循IEEE802.3标准的网络通信已经应用到较广泛的场合。其具有连接方便、即插即用的特点。网线物理结构

2019-06-21 05:00:01

,与ENC28J60以太网控制器通过SPI接口相连,在μIP协议栈的基础上实现下位机与远程监控主机的网络通信功能,并在ZigBee协议栈的基础上通过CC2530芯片组建无线传感器网络,通过串口与主控芯片通信。

2019-08-27 07:20:29

我的程序中嵌套了很多while(1)循环, 在每个循环的头部 加入LWIP_Polling(),然后按键通过网络发送参数 ,但是发送不了。感觉103的网络通信不太好用,以前用过107,它的网络通信不需要LWIP_Polling(),实时性非常好。

2019-08-07 01:23:58

W5500网关芯片 随笔最新在使用w5500芯片做 网络通信时 ,遇到一个问题,如果创建两个线程,一个线程 创建一个socket 进行局域网内 的tcp 通信,再创建另一个线程 进行广域网的mqtt

2022-01-13 07:33:02

这些年,关于‘网络通信’的特性描述,听过最多的拟合场景就是:一个人在讲话,哪些人(们)可以听得到?最近有机会进一步的琢磨这些事,这里做个总结。单播、多播、广播:在tcpi/ip四层模型中, 网络层

2021-08-05 07:24:15

本文基于TCP/IP网络协议设计并实现了浮标网络通信系统。

2021-05-28 06:44:08

单片机网络的例程中底层用的接口是RGMII吗?提供的例程中接口被封装成了Lib库,无法识别使用了那种接口。如果不是的话,有什么办法能改成使用RGMII接口呢?

2022-09-15 06:37:21

有一个松下投影仪,控制投影仪的方式有3中,串口232,遥控器红外控制,用电脑通过网口通信。我想我问一下,可以用单片机通过网络通信控制投影仪吗?单片机通过w5500芯片引出了一个网口。对于网络通信方式很陌生,网络通信方式是不是只能在计算机和带有网络通信方式的设备之间进行通信的呀。

2019-03-05 10:10:54

。利用网络通信协议把数据从一个网络或Internet计算机传输到另外一台计算机或网络上是实现远程测控系统通信的最基本方式。但基于DataSocket技术的网络通信可以达到很高的数据传输效率,实时性能相当

2019-04-28 10:04:13

基于NiosII的嵌入式网络通信系统该如何去设计?

2021-06-03 06:41:23

基于TCP/IP的网络通信应用程序(TCP-Server)上一篇文章讲述了在i.MX6UL开发板中,以客户端的角色,使用TCP/IP协议进行网络通信。嵌入式Linux应用程序开发-(7)TCP-IP

2021-12-23 08:12:11

基于TCP/IP的网络通信应用程序(TCP-Client) 不管是嵌入式Linux应用程序,还是物联网IoT应用开发,网络通信一定是一个不可或缺的重要环节。可以说,没有网络支持,整个物联网应用体系将

2021-11-05 09:06:11

基于UDP协议的网络通信应用程序(UDP-Socket)前两篇文章介绍了基于TCP/IP协议的网络通信应用程序。嵌入式Linux应用程序开发-(7)TCP-IP网络通信应用程序(TCP-Client

2021-11-05 08:29:22

请教一下诸位大侠,stm32实现网络通信之后数据上传到上位机上去之后保存在本地PC里。我现在遇到的问题是:我想在宿舍去查看我实验室的电脑里面的数据,请问有没有这类网络通信的解决方案呢?跪求。。。

2019-07-29 23:23:54

如何实现安全网络通信?AES加解密算法的原理是什么?怎样去设计并实现GSM网络报警机制的?

2021-04-08 06:05:24

我们的计划是通过 RGMII 接口将 TC397 连接到 Marvell 88Q5152,以满足我们的应用要求。

过去,在Linux系统上,我们设置了一个固定链接来直接指定速度和双工模式。 我们想

2024-01-26 06:05:54

,与ENC28J60以太网控制器通过SPI接口相连,在μIP协议栈的基础上实现下位机与远程监控主机的网络通信功能,并在ZigBee协议栈的基础上通过CC2530芯片组建无线传感器网络,通过串口与主控芯片通信。

2019-08-28 07:35:33

本文论述一种具有网络通信和多媒体处理功能的嵌入式系统的设计实现方法。

2021-06-07 06:36:24

怎么实现分布式测试系统的一种网络通信设计?

2021-05-08 09:48:22

DSP与网卡的硬件接口技术参考文献有比较详尽的论述,本文主要讨论基于DSP的网络通信程序设计。

2021-05-31 07:00:01

怎么实现微波无线网络通信系统设计?

2021-06-07 07:08:37

怎样去设计一种基于Socket的网络通信程序呢?在LINUX系统与WINDOWS系统之间如何进行基于Socket的网络通信呢?

2021-12-23 08:21:18

MII接口的管脚定义有哪些?怎样通过MII或者RMII接口进行网络通信呢?

2021-10-28 08:03:00

我想学网络通信,我现在不知道应该如何下手,应注意那些技术?需要那些基础知识?或者有木有什么好的入门教材推荐?我之前主要是做嵌入式开发,对硬件、单片机的串并行通信比较熟,网络通信还没接触过,想了解一下。还请高手们指教!

2012-12-16 13:33:17

电力系统的发电、 输电、变电、配电、用电和调度各个环节的发展路 线,强调各个领域电力流、信息流和业务流的融合, 因此,智能电网的框架中各个关键领域的沟通,必 然是由网络通信为桥梁实现的。 2009 年

2013-10-09 11:42:53

求lebview的网络通信关于TCP协议的案例

2015-03-18 19:47:38

C6747芯片对网络通信开发的支持现在能找到的资料都集中在NDK开发包上,但NDK好像是和DSP/BIOS绑定的,请问C6747有不使用操作系统的网络通信开发demo吗?

2018-08-01 07:15:38

求F1单片机程序实现 提供网络通信接口并实现数据的上传。急用

2020-03-20 01:40:51

技术,二是基于DSP的网络通信程序设计。DSP与网卡的硬件接口技术参考文献[1]有比较详尽的论述,以下主要讨论基于DSP的网络通信程序设计。 1 通信协议的制定 协议是用来管理通信的法规,是网络系统

2019-06-20 05:00:04

的网络通信程序设计 如果基于网络操作系统,用户可以利用一些软件对网络操作系统的支持,很容易地编写出优秀的网络通信程序,但这些程序必须依附于网络操作系统。而在DSP环境下,必须深入了解网络接口控制器(NIC

2019-06-20 05:00:05

嵌入式操作系统VxWorks中的网络通信

2009-03-29 12:26:42 18

18 结合工程实例, 基于S3C4510B 微处理器, 构建以DM9161 为以太网物理层接口的低功耗、高速硬件电路;在嵌入式操作系统uCLinux 上实现网络通信的程序编写,对于网络通信在嵌入式设备

2009-05-16 13:29:35 16

16 本文介绍了嵌入式系统芯片S3C2510A 的网络通信接口模块的设计方法。介绍了设计此嵌入式系统以太网通信接口模块所需的以太网控制芯片DM9161 和S3C2510A 嵌入式微控制器。对接口电路

2009-06-04 09:11:40 25

25 作为一种高性能的嵌入式实时操作系统,VxWorks 在嵌入式系统中获得了广泛的应用。本文讨论了VxWorks 中基于socket 的C/S 网络通信原理,并利用这种网络通信原理设计了进程之间通信

2009-08-05 16:32:01 12

12 文章结合工程实例,基于S3C4510B 微处理器构建了以DM9161 为以太网物理层接口的低功耗、高速硬件电路。并且在嵌入式操作系统uCLinux 上实现了网络通信的程序编写,这对于网络通

2009-08-14 12:07:55 34

34 结合工程实例, 基于S 3 C 4 5 1 0 B微处理器, 构建以D M 9 1 6 1为以太网物理层接口的低功耗、高速硬件 电路;在嵌入式操作系统u C L i n u x上实现网络通信的程序编写,对于网络通

2009-12-05 16:25:49 25

25 结合嵌入式实时系统VxWorks实现网络通信系统的实际应用,以其中有连接的TCP、无连接的UDP通信为例,讨论了在VxWorks下实现设备操作和网络通信的关键技术和相应的机制,给出了软

2010-01-11 09:52:21 28

28 本文结合嵌入式实时操作系统VxWorks实现网络通信系统的实际应用,讨论了在VxWorks下实现网络通信的关键技术和相应的机制,并已经在网络测试仪中得到了良好而有效的应用。开发出的

2010-07-14 17:04:53 21

21 为适应工程中各类嵌入式模块接口性能测试的网络化趋势,设计了稳定可靠的通信机制,实现客户机/服务器模式的测试系统。基于解决网络通信问题的套接字网络编程,利用

2010-11-26 15:45:53 25

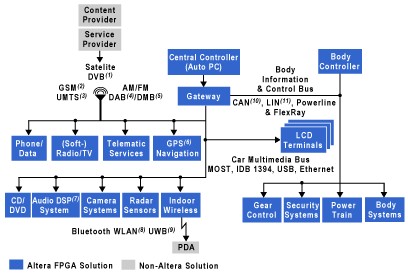

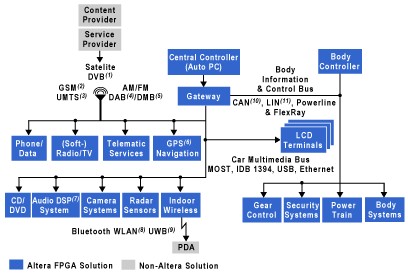

25 什么是汽车的网络通信系统

在保证正常驾驶情况下,网络通信

2010-03-17 13:39:37 3188

3188

什么是网络通信优先级

网络通信优先级在概念上很简单:重要网络通信获得高于次要网络通信的优先权。但这引出了一系列有趣的问

2010-04-03 16:41:38 2887

2887 文章分析了传输层网络通信协议,并在UDP协议之上设计了实时控制协议RCP、应用程序接口层API两个额外的层,提出了实时数据网络通信传输结构。重点阐明了设计实时控制协议RCP解决实

2011-03-31 21:34:04 19

19 网络通信七层,讲解了网络7层定义及理论,很好的学习资料。

2016-03-15 13:49:56 12

12 工业网络通信技术,网络通信学习的好资料,值得下载哦。

2016-03-21 16:56:35 22

22 内存对齐对网络通信程序的影响,网络通信的技术资料,很好很实用。

2016-03-28 10:41:08 12

12 网络通信过程,网络通信的技术资料,很好很实用。

2016-03-28 10:36:39 14

14 网络通信过程研究,网络通信的技术资料,很好很实用。

2016-03-28 10:35:13 7

7 网络通信过程中的故障排除,网络通信的技术资料,很好很实用。

2016-03-28 10:31:45 11

11 网络通信技术对教育影响,网络通信的技术资料,很好很实用。

2016-03-28 10:29:57 9

9 网络通信平台的内存使用,网络通信的技术资料,很好很实用。

2016-03-28 10:25:24 17

17 网络通信系统的控制技术,网络通信的技术资料,很好很实用。

2016-03-28 10:23:28 11

11 一种适于单片机系统的网络通信协议,网络通信的技术资料,很好很实用。

2016-03-28 10:08:37 11

11 TD-SCDMA网络通信,网络通信基础资料,快来学习吧

2016-04-13 16:40:58 14

14 使用JAVA编写网络通信程序,网络通信基础资料,快来学习吧

2016-04-13 16:40:58 15

15 浅谈分析网络通信系统的信息脆性风险评估,很好的网络通信资料,快来学习吧。

2016-04-19 11:30:48 19

19 浅析基于数据加密的网络通信系统的设计与应用,很好的网络通信资料,快来学习吧。

2016-04-19 11:30:48 16

16 基于嵌入式操作系统VxWorks中的网络通信

2017-08-31 15:57:55 3

3 本文档的主要内容详细介绍的是88E1512千兆以太网PHY的设计原理参考原理图资料免费下载。

2019-01-03 08:00:00 517

517 Marvell®阿拉斯加®88E1512千兆以太网(GbE)收发器是包含单个千兆以太网收发器的物理层设备。收发器实现1000Base-T、100Base-TX和10Base-T标准的以太网物理层部分

2019-01-28 08:00:00 279

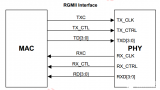

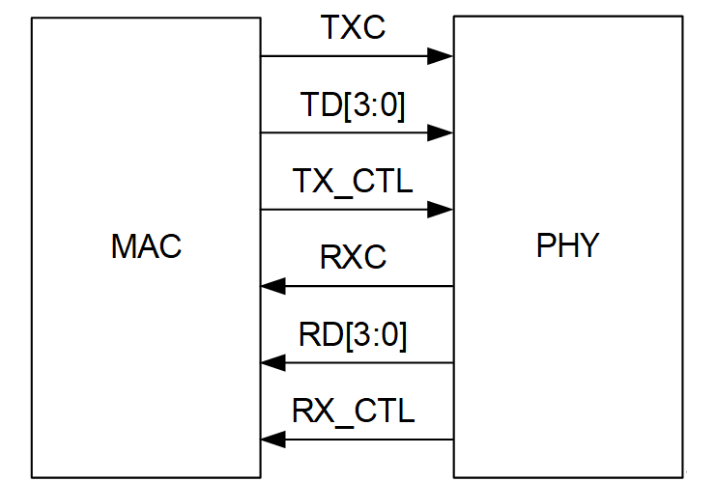

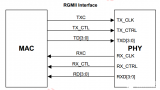

279 RGMII接口,是Reduced Gigabit Media Independent Interface的缩写。IEEE802.3 Clause 35在RS子层和PCS子层之间定义了一组接口GMII,该接口作为MAC和PHY数据交互接口。

2020-09-30 11:26:30 29313

29313

网络通信技术的使用尤为重要,对于网络通信技术,计算机专业的朋友均有所了解。为了增进大家对网络通信技术的了解,本文将对计算机网络通信技术原理予以解释。

2020-12-26 02:13:24 1053

1053 非连续数据网络通信系统设计与实现

2021-06-24 16:08:28 22

22 网络通信中最重要的就是网络通信协议。当今网络协议有很多,局域网中最常用的有三个网络协议:MICROSOFT的NETBEUI、NOVELL的IPX/SPX和TCP/IP协议。应根据需要来选择合适的网络协议。

2023-05-08 15:02:50 1322

1322 网络通信可以分为两大类:客户端准客户端(C/S)和Peer-To-Peer(P2P)网络通信。其中,客户端/服务器式网络通信是指传统的客户端/服务器网络模型,客户端通常指浏览器或其他用户端,服务器则提供网络服务,如文件共享等,用于为客户端提供服务。

2023-05-08 15:12:49 1427

1427 高速传输:网络通信技术具有高速传输的特点,可以实现较快的数据传输速度。随着技术的发展,网络通信技术的传输速度不断提高,可以实现更快速的数据传输。

2023-05-08 15:17:53 695

695 Marvell®Alaska®88E1512千兆以太网(GbE)收发器是种包含单独的千兆以太网收发器的mac层设备。88E1512-A0-NNP2C000收发器实现1000BASE-T

2023-08-09 14:00:48 968

968 Alaska®88E1510/88E1518/88E1512/88E1514设备是个物理层设备,包括一个10/100/1000千兆以太网收发器。88E1512-A0-NNP2I000实现

2023-08-14 13:51:55 2144

2144 本篇博文使用ESP32-S3搭建网络摄像头,相比较局域网摄像头,本篇博文将分享如何搭建外网可以访问的网络摄像头。

2023-09-06 12:48:55 2547

2547

5G网络通信有哪些技术痛点?光耦技术在5G网络通信的应用 5G网络通信的技术痛点: 1. 频谱资源短缺:5G通信需要更高的频谱资源来支持更大的数据传输量和更高的速度,但是目前无线通信频谱资源已经

2024-02-18 17:13:30 362

362

电子发烧友App

电子发烧友App

评论