S2C日前宣布他们已经开发了一种原型验证产品,即TAI Verification Module(专利申请中)。它允许使用者通过一条x4 PCIe Gen2通道到连接FPGA原型中的用户设计和用户的电脑,使得用户能够使用大量

2011-06-16 08:55:48 1785

1785 什么是FPGA原型? FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能

2022-07-19 16:27:29 1735

1735 原型验证过程中的ASIC到FPGA的代码是怎样进行转换的?

2021-05-08 09:16:18

的费用持续上升。一次失败的ASIC流片将会推迟数个月的上市时间。谁愿意承担签字的责任呢? 一些BUG通过仿真和Emulation是抓不到的。传统的验证方法认为设计的功能符合功能定义就是对的。 但功能定义到底对不对呢?唯一的办法就是建立一个真实的硬件:原型。

2019-07-11 08:19:24

。 ASIC在离开生产线后再也无法改变。这就是为什么设计师在大规模量产之前需要完全确保设计正确无误。工程师可以利用FPGA的可重配置这一优势,进行ASIC的原型验证,以便在将设计发送到代工厂之前,可以在

2020-12-01 17:41:49

1ASIC 验证技术.................................................11.1 ASIC 设计流程

2015-09-18 15:26:25

ASIC设计-FPGA原型验证

2020-03-19 16:15:49

FPGA 验证可以说就完成了 ASIC 整套流程的 50~80%。从设计成本来考虑,小批量上 FPGA 占优,大批量时,ASIC 占优。FPGA 本身就是一个芯片,只是你可以通过编程的方式修改内部逻辑连接

2020-09-25 11:34:41

。FPGA本身就是一个芯片,只是你可以通过编程的方式修改内部逻辑连接和配置实现自己想要的功能。实现ASIC,就如从一张白纸开始,你得有代码,之后综合,之后布局,布线,得到GDSII后去流片。比速度相同的工艺

2017-09-02 22:24:53

FPGA原型验证已是当前原型验证的主流且成熟的芯片验证方法——它通过将RTL移植到现场可编程门阵列(FPGA)来验证ASIC的功能,并在芯片的基本功能验证通过后就可以开始驱动的开发,一直到芯片

2020-08-21 05:00:12

ASIC是一种为专门目的而设计的集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。ASIC的特点是面向特定用户的需求,亮点在于运行速度在同等条件下比FPGA快。FPGA作为

2017-06-12 15:56:59

既然是芯片验证,那就需要明确验证芯片的哪些特性(功能、性能等)。验证空间是无穷大的,验证工程师需要在有限的时间内,完成尽可能多的重要verification features的验证

2022-12-30 16:21:57

。这是由于在 FPGA 质量和开发时间上提高了 UVVM 良率。这个开源库和方法具有最广泛的 VHDL 验证支持,让您以非常有效的方式验证真正复杂的 DUT,提供类似于 UVM 的模块化、可重用性

2022-02-13 17:03:49

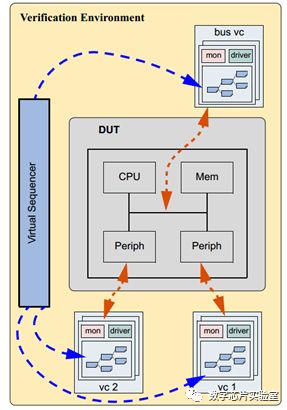

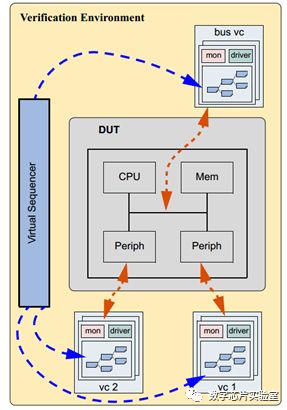

model)。一个简单的验证平台框图:在UVM中,引入了agent和sequence的概念,因此UVM中验证平台的典型框图长这样:通知:本章更新后在更新一篇《IC验证之UVM常用宏汇总(四)》将不

2020-12-02 15:21:34

加入factory机制 上一节《IC验证"一个简单的UVM验证平台"是如何搭建的(五)》给出了一个只有driver、使用UVM搭建的验证平台。严格来说这根本就不算是UVM验证

2020-12-08 12:07:21

的组件,是整个验证平台数据流的源泉。本节以一个简单的DUT为例,说明一个只有driver的UVM验 证平台是如何搭建的。最简单的验证平台,假设有如下的DUT定义:这个DUT的功能非常简单,通过rxd接收

2020-12-04 15:48:19

Verification Methodology),其正式版是在2011年2月由Accellera推出的,得到了Sysnopsys、Mentor和Cadence 的支持。UVM几乎完全继承了OVM,同时又采纳了

2020-12-01 15:09:14

在上一节中,**《IC验证"UVM验证平台加入factory机制"(六)》**虽然输出了“main_phase is called”,但是“data is drived”并没有

2020-12-09 18:28:15

第二章 验证flow验证的Roadmap验证的目标UVM验证方法学ASIC验证分解验证策略和任务的分解AMBA可重用、灵活性、兼容性、广泛支持一.验证的Roadmap1.ASIC芯片项目流程市场需求

2021-11-01 06:28:47

Knowledge of SoC (ASIC/FPGA) design and verification tools. System One to Two

2009-04-10 15:17:03

in ASIC verification.- Needs to have better understanding of Verification methodology and concepts-

2012-08-20 18:35:50

本帖最后由 NvidiaHR 于 2012-7-6 14:28 编辑

ASIC/SOC Verification Engineer:RESPONSIBILITIES:- RTL design

2012-07-06 14:27:07

方法中的漏洞。用于可笑的测试并支持设计人员运行他们自己的验证。加快标准验证流程并支持芯片启动测试开发。等等等等。 这份长达 500 多页的介绍性材料将向读者介绍处理硬件验证需求的主要 Python

2022-11-03 13:07:24

先进的设计与仿真验证方法成为SoC设计成功的关键。一个简单可行的SoC验证平台,可以加快SoC系统的开发与验证过程。FPGA器件的主要开发供应商都针对自己的产品推出了SoC系统的开发验证平台,如

2019-10-11 07:07:07

on design language Verilog/VHDL Good knowledge on SystemVerilog, and verification methodology OVM/UVM Good

2012-04-05 23:26:48

。HAPS-51采用FPGA阵列Xilinx Virtex-5 LX330和板上存储器,加快了ASIC验证的速度。先前的HAPS系统在存储器存取方面采用子板,而最新的HAPS-51则采用位于板上并靠近

2018-11-20 15:49:49

设计。 现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块. 这样的ASIC常被称为SoC(片上系统)。 FPGA是ASIC的近亲,一般通过

2012-02-27 17:46:03

AMD超威半导体上海研发中心招聘 ASIC Design Verification Engineer;请有意向者将简历发送到 Maggie1.Zhang@amd.com 以及

2017-03-13 16:47:03

design3.Familiar with System-Verilog and UVM verification methodology4.Familiar with script languages

2018-09-19 14:15:19

的开发和验证符合这一过程是DO-254.1的目标安森美半导体& DO-254支持安森美半导体的数字ASIC设计流程及其采用的方法完全支持需要获得DO-254认证的商用飞机制造商的严格要求。符合

2018-10-17 15:03:44

大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源?本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构。我们一个

2022-02-14 06:46:33

就以支持AWS的FPGA平台为主要方案。 至此,FPGA AI这样一来设计迭代速度(尤其是配合了Chisel,HLS等敏捷开发流程之后)可以远远快于传统ASIC流程,同时硬件的能效比则远高于传统

2023-03-28 11:14:04

提供的门电路规模足够大,通过编程,就能够实现任意ASIC的逻辑功能。

FPGA开发套件,中间那个是FPGA芯片

我们再看看FPGA的发展历程。

FPGA是在PAL(可编程

2024-01-23 19:08:55

/verifications. 2. Responsible for IPs/SOC design FPGA emulation/verification. 3. Responsible for chip

2015-06-12 12:07:37

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-11 07:59:44

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-15 07:38:34

的验证结构,以及以功能覆盖率为指标的验证流程。在本文中,围绕Synopsys的VMM(Verification Methodology Manual)构建了一个MCU验证环境。

2019-07-01 08:15:47

如何通过视频帧加快视频设备开发和调试速度?

2021-06-03 06:51:58

ASIC验证能够采用的主要技术是什么?如何利用现成FPGA开发板进行ASIC原型开发?

2021-05-08 07:51:04

请教各位大佬,UVM是基于sv的验证方法学,如果采用systemc语言编程,如何实现?

2019-11-07 15:30:16

可编程门阵列FPGA具有可编程特性,用户根据特定的应用定制电路结构,因此其处理速度大大超过通用处理器。与ASIC相比,FPGA的缺点是在提供灵活的可编程同时,则以芯片的面积、功耗和速度做为代价。

2019-09-03 07:44:22

Ctrl-V!)

几点说明:

为了使用UVM库里的函数和宏定义,需要先import uvm_pkg和include uvm_macros。

在testbench的顶层(module tb)里通过

2023-11-03 10:18:58

:外商独资·外企办事处 下属人数:0 企业规模:100-499人 岗位职责Responsibilities:1.FPGA design and verification. Porting ASIC code

2012-03-15 13:55:19

,对黑盒验证,我们只能通过了解其设计文档来了解它的功能。验证就存在着数据比较。通常的做法是使用高级语言为被测设计建立一个参考模型,这个参考模型将模拟被测设计的行为,并给出相应的结果,将这个理想的结果

2021-01-21 15:59:03

会在一定范围内产生,减少无用的激励,提高效率。支持覆盖率驱动模式,根据当前覆盖率的情况,验证工程师可以决定下一步的验证内容,当覆盖率达到了一定的要求时,就可以宣告验证工作的完成。uvm验证平台,它具有很高的可重用性

2021-01-21 16:00:16

大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源? 本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构

2021-01-22 15:32:04

大家好,我是一哥,上章一个典型的uvm验证平台应该是什么样子的?从本章开始就正式进入uvm知识的学习。先一步一步搭建一个简单的可运行的测试平台。 本章首先来介绍一下构成uvm测试平台的主要组件

2021-01-22 15:33:26

the UniversalVerification Methodology(UVM)》,后来的第二版我很喜欢,里面配有大量实际验证中的例子,很有价值。这本身出版后反映不错,所以有了后来的另一

2015-03-11 16:24:35

浮点是最优选的数据类型,可确保算法建模和仿真的高精度计算。传统上,当您想要将这种浮点算法部署到FPGA或ASIC硬件时,您唯一的选择是将算法中的每种数据类型转换为定点,以节省硬件资源并加快计算速度

2018-09-11 21:59:16

失败的原因不是时序或者功率的问题,而是逻辑或功能错误。为此,功能验证已经成为ASIC开发周期中一个最关键的环节,通常最耗费时间。越来越多的ASIC设计人员发现通过采用FPGA进行功能原型设计能够最好

2019-07-15 07:00:39

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法。本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。1、RFID芯片的FPGA

2019-05-29 08:03:31

that dominates time scales. This book defines a methodology that helps minimize the time necessary to meet the verification requirements. It also takes

2009-07-22 14:39:21 37

37 that dominates time scales. This book defines a methodology that helps minimize the time necessary to meet the verification requirements. It also takes

2009-07-22 14:41:06 13

13 在现在复杂的ASIC 设计中,校验(Verification)是最大的瓶颈。随着先进的半导体工艺技术不断前进,随之带来的是ASIC 设计规模和设计复杂度的飞速增长,这使得传统的软件仿真工具

2009-11-24 12:20:02 24

24 a means of Mentor’s advanced verification methodology (AVM) basedunified verification platform solution.The continuing growth o

2010-07-04 11:39:45 17

17 Open Verification Methodology(OVM)是Mentor Graphics 和Cadence 共同推出的,业界第一个基于SystemVerilog、通用开放的验证方法学;其基于事务交易级的方法学,基于Factory Pattern 的对象生

2010-07-04 11:43:22 7

7 FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。由于FPGA与ASIC在结构、性能上各不相同,ASIC是基于标准单元库,FPGA用的

2010-09-10 17:22:26 989

989 对ASIC设计进行FPGA原型验证时,由于物理结构不同,ASIC的代码必须进行一定的转换后才能作为FPGA的输入。 现代集成电路设计中,芯片的规模和复杂度正呈指数增加。尤其在ASIC设计流程中

2011-03-25 15:16:20 108

108 MathWorks 近日宣布推出 HDL Coder,该产品 支持MATLAB 自动生成 HDL 代码,允许工程师利用广泛应用的 MATLAB 语言实现 FPGA 和 ASIC 设计。

2012-03-07 09:27:18 2033

2033

本文描述ASIC验证方法和过程,有助于ASIC设计者对验证的认识。模拟是验证ASIC并产生测试矢量的唯一途径,设计者可以对ASIC芯片或者在ASIC应用系统中进行功能和时序模拟。

2012-05-24 09:32:47 23

23 本文描述ASIC验证方法和过程,有助于ASIC设计者对验证的认识。模拟是验证ASIC并产生测试矢量的唯一途径,设计者可以对ASIC芯片或者在ASIC应用系统中进行功能和时序模拟。

2012-05-24 09:32:47 27

27 彻底地验证其片上系统(SoC)是否符合HDMI 2.0规范,从而加速批量生产的准备时间。这款用于HDMI 2.0的Cadence VIP支持各种主流逻辑模拟器、验证语言及包括UVM(Universal Verification Methodology)在内的方法学。

2013-09-27 16:19:08 857

857 基于UVM的CPU卡芯片验证平台_钱一文

2017-01-07 19:00:39 4

4 基于UVM的验证平台设计研究_王国军

2017-01-07 19:00:39 4

4 基于UVM的CAN模块自验证方法_熊涛

2017-01-08 14:47:53 3

3 一种基于UVM的混合信号验证环境_耿睿

2017-01-07 21:39:44 1

1 7200 万个 ASIC 门的容量。 FPGA 原型设计系统通过添加多达 3 个附加电路板,可使用 Aldec 背板 (HES7-BPx4) 扩展至 28800 万个 ASIC 门。 了解更多 »

2017-02-09 06:27:08 327

327 FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。

2017-02-11 12:46:11 2975

2975 的连接、驱动器、监视器、仿真序列以及功能覆盖率的建立。 本文呈现出了一种使用UVM验证方法学构建基于高可配置性的高级微处理器总线架构(AMBA)的IP验证环境,其中会使用到Synopsys公司的AMBA VIP和Ruby脚本。该验证环境可以支持通过使用AMBA设计参数进行自

2017-09-15 14:37:34 6

6 。 本文所聚焦的技术手段是让一个已有的UVM验证平台通过改变需求去执行硬件加速。如果这些点在UVM环境开发过程中被考虑到,那么之后将环境迁移到硬件加速器作为一个性能选项将是一件较容易的事情。本文所提议的建议将会使你的UVM验证

2017-09-15 17:08:11 14

14 近年来,ASIC设计规模的增大带来了前所未有的芯片原型验证问题,单颗大容量的FPGA通常已不足以容下千万门级、甚至上亿门级的逻辑设计。现今,将整个验证设计分割到多个采用最新工艺大容量FPGA中,FPGA通过高速总线互联,成为大规模ASIC或SOC原型验证的极佳选择。

2018-07-02 08:20:00 1695

1695 采用fpga原型技术验证asic设计,首先需要把asic设计转化为fpga设计。但asic是基于标准单元库,fpga则是基于查找表,asic和fpga物理结构上的不同,决定了asic代码需要一定

2019-07-23 08:07:00 1923

1923

ASIC芯片一旦流片功能就无法改变,基本专片专用。而FPGA可配置特性就可以应用在功能会改变的场合,例如,原型验证,ASIC设计过程中会使用到FPGA来进行原型验证;功能升级,在产品中采用FPGA实现一些业内暂时还没成熟的解决方案,可以在后续功能变动时方便升级。

2019-08-25 10:40:01 10934

10934

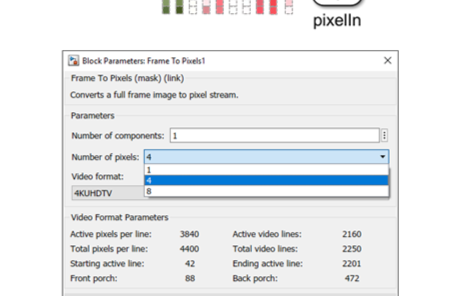

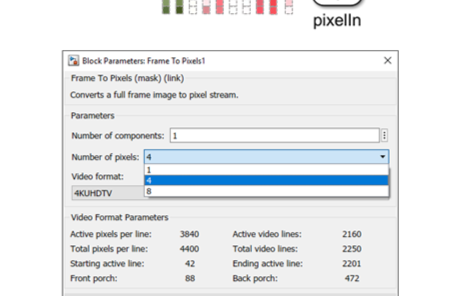

上处理高帧率 (HFR) 和高分辨率视频的原生多像素流处理支持。视频、图像处理和 FPGA 设计工程师在处理 240fps 或更高分辨率的 4k 或 8k 视频时可以加快权衡表现和实现的探索和仿真速度。

2020-03-01 12:40:38 725

725 MathWorks宣布,HDLVerifier从现已上市的Release2019b开始提供对UniversalVerificationMethodology(UVM)的支持。

2020-03-07 14:29:17 815

815 MathWorks宣布,随着 2019b 发行版的 MATLAB 和 Simulink 产品系列最近上市,Vision HDL Toolbox提供对在 FPGA 上处理高帧率 (HFR) 和高分辨率视频的原生多像素流处理支持。

2020-05-09 10:55:41 331

331

本周美国海关及边境保卫局宣布将在更多机场中实行“简化到达”计划,即通过人脸识别验证乘客身份,加快安检速度和防止非法入境。

2020-10-15 09:52:43 547

547 Express 5.0的物理层和电气接口。 新思科技CXL验证IP基于新一代SystemVerilog的 Universal Verification Methodology(UVM)架构,使验证IP的集成

2020-12-26 11:04:10 2458

2458 本文是本人对xilinx XC7V系列FPGA用于ASIC前端验证遇到问题的总结,为自己记录并分享给大家,如果有歧义或错误请大家在评论里指出。

2021-01-12 17:31:44 9

9 大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源?本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构。我们

2021-12-09 13:36:13 7

7 需要门级验证:FPGA 和 ASIC 一样需要设计级验证。但是,FPGA 在门级不是细粒度的,因此它们不需要门级验证。您将每个门都放置在 ASIC 设计中,因此您需要验证每个门。

2022-06-20 16:13:05 2184

2184

ASIC设计服务暨IP研发销售厂商智原科技(Faraday Technology Corporation,TWSE:3035)今日发布FPGA-Go-ASIC验证平台。

2022-07-29 10:08:16 784

784 利用Systemverilog+UVM搭建soc验证环境

2022-08-08 14:35:05 5

5 百度百科对UVM的释义如下:通用验证方法学(Universal Verification Methodology, UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境。

2022-11-30 12:47:00 1061

1061 因为DUT是一个静态的内容,所以testbench理应也是静态的,其作为uvm验证环境和DUT的全局根结点。

2023-03-21 11:33:02 982

982 FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 本文使用Easier UVM Code Generator生成包含多个agent和interface的uvm验证环境。

2023-06-06 09:13:02 584

584 UVM提供了实现 **覆盖驱动验证(coverage-driven verification ,CDV)** 的框架。 CDV结合了自动测试向量生成,自检查和覆盖率收集,显著地缩短了用于验证设计时间。

2023-06-25 11:38:58 861

861

FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2024-01-12 16:13:01 220

220 FPGA验证和UVM验证在芯片设计和验证过程中都扮演着重要的角色,但它们之间存在明显的区别。

2024-03-15 15:00:41 94

94

电子发烧友App

电子发烧友App

评论