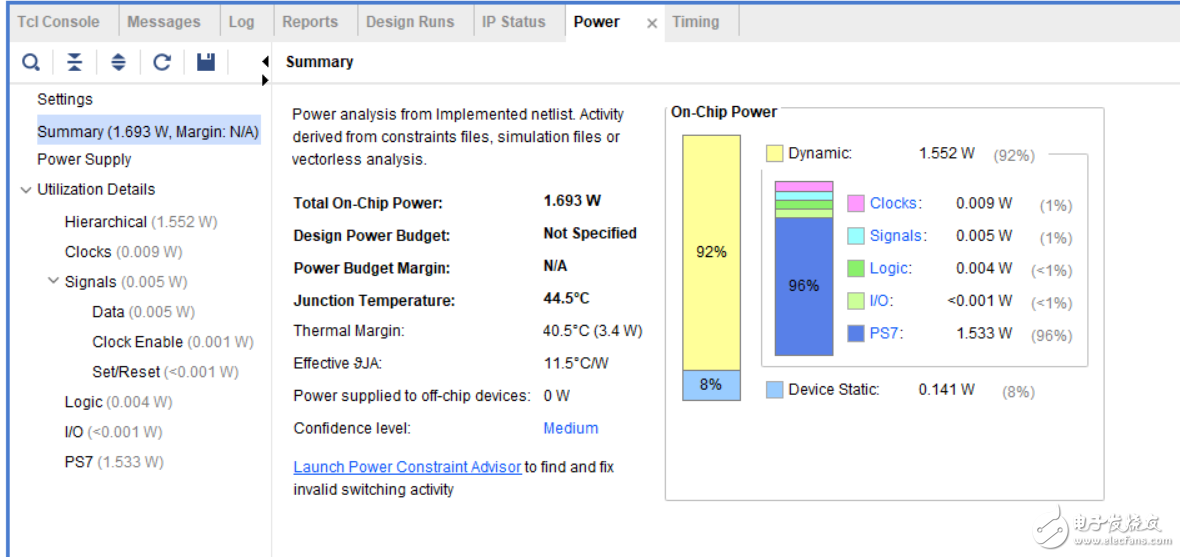

先给大家简单快速地介绍一下 Vivado 集成设计环境,即 IDE。当打开 Vivado 工程后,会有一个工程概要,向您介绍工程的设置、警告和错误信息以及工程的一般状态。

2012-04-25 09:00:43 6408

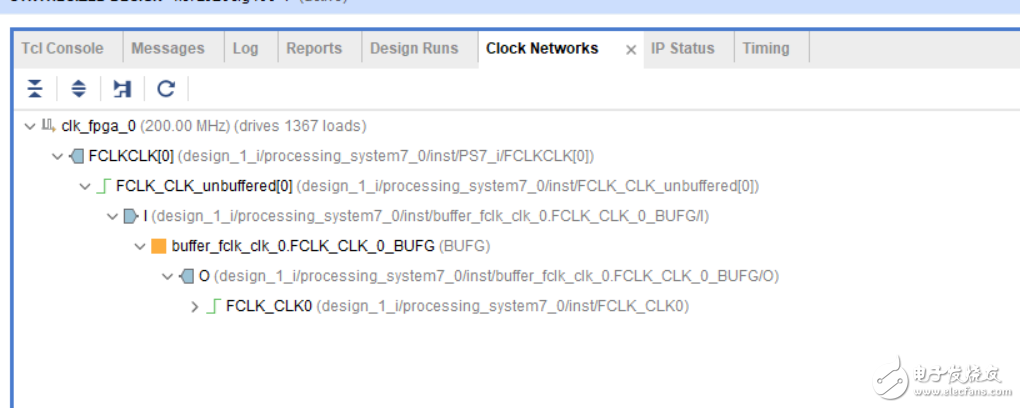

6408 路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 7410

7410 时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

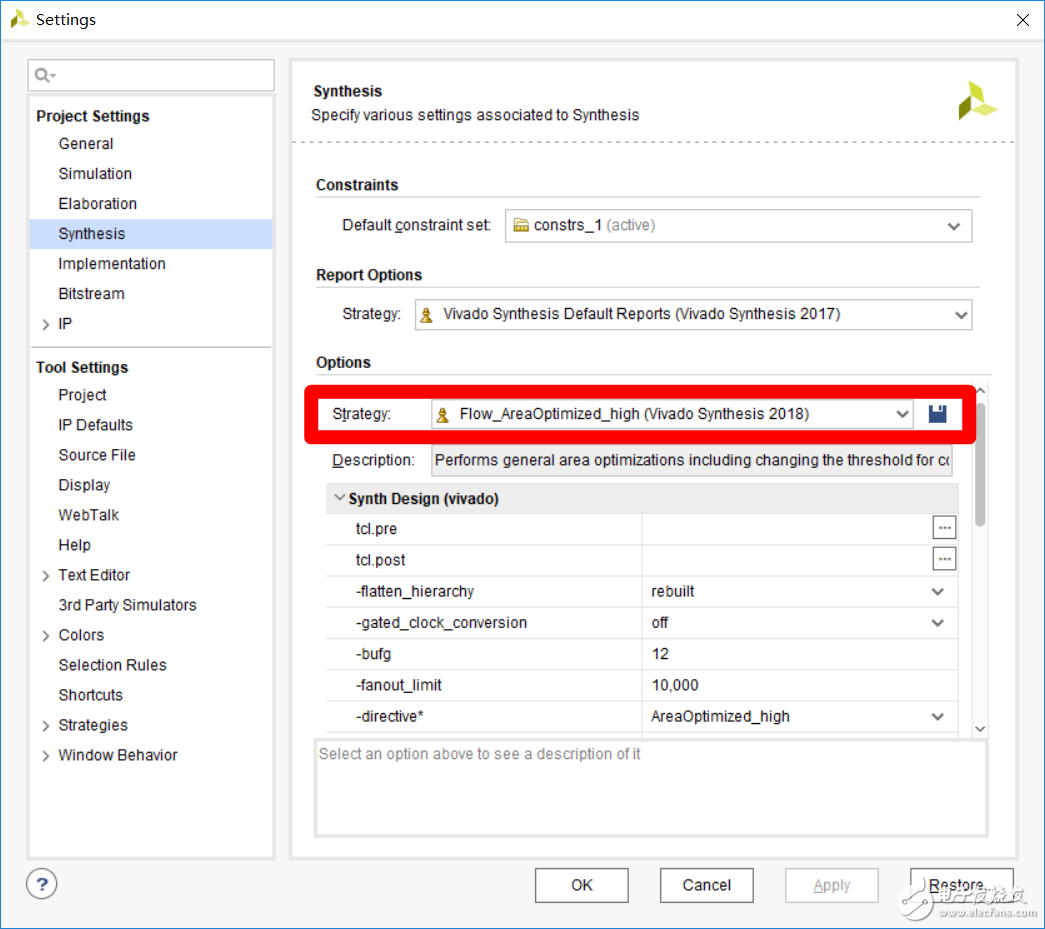

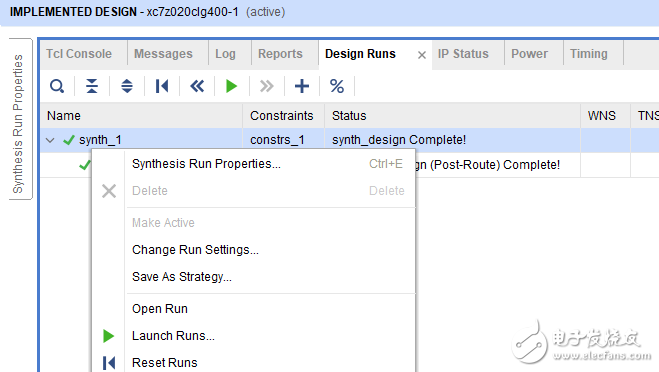

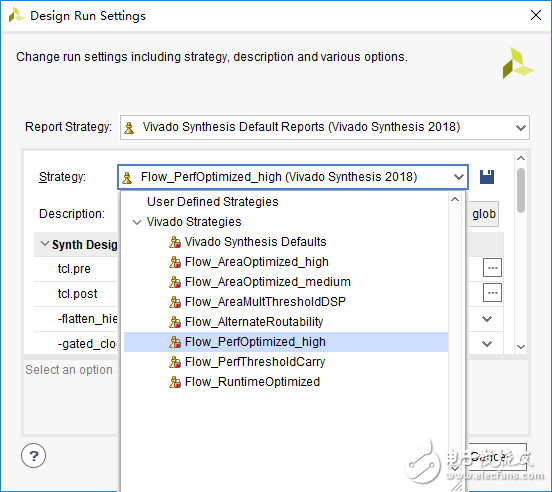

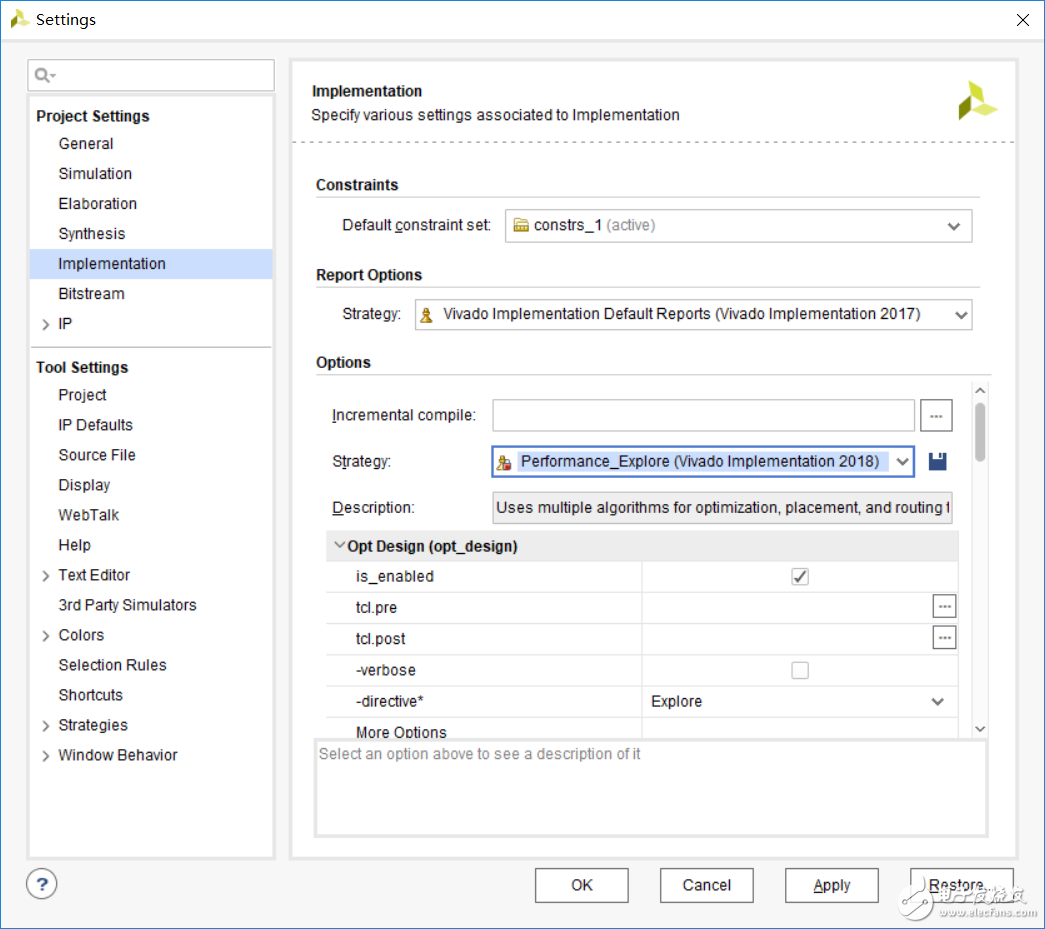

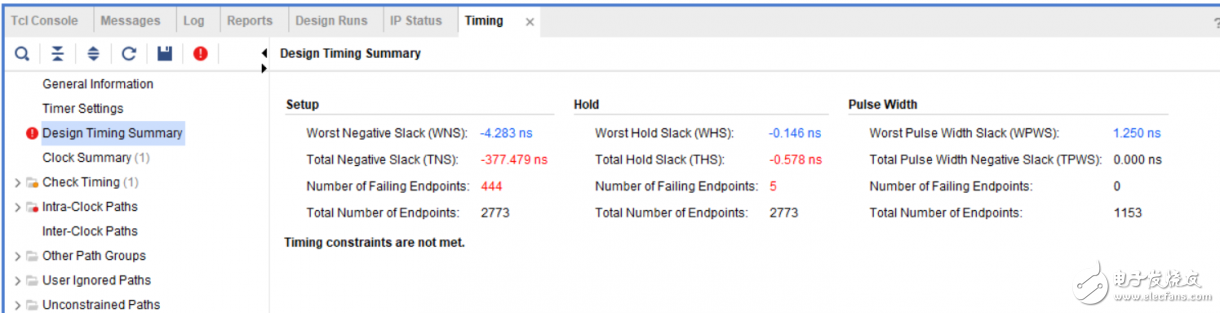

8731 在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分析

2022-08-02 08:03:38 1016

1016

时序分析是FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-10-21 09:28:58 1284

1284 学习。个人学习的时候可以根据实际情况选择最高至Vivado2019.1。(从Vivado2019.2开始,PS开发使用Vitis,没有SDK了)第1章 FPGA技术分析 / 11.1 FPGA内部结构

2020-10-21 18:24:48

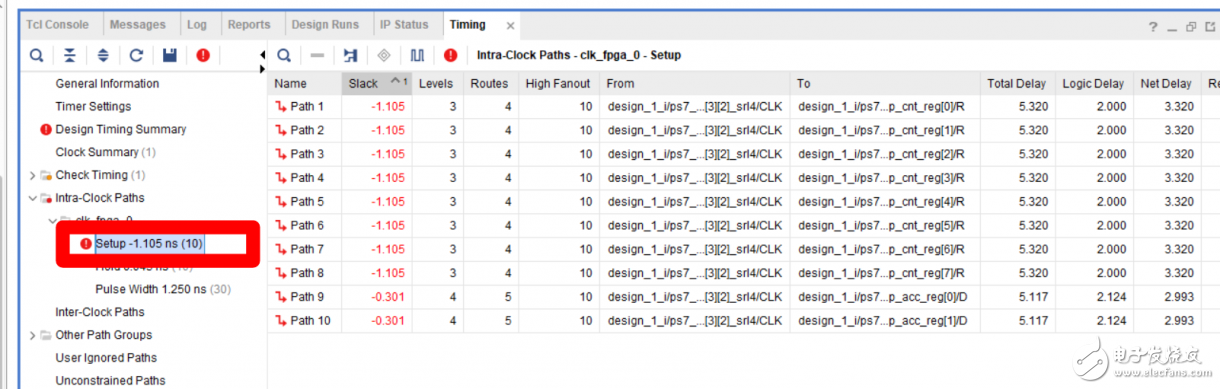

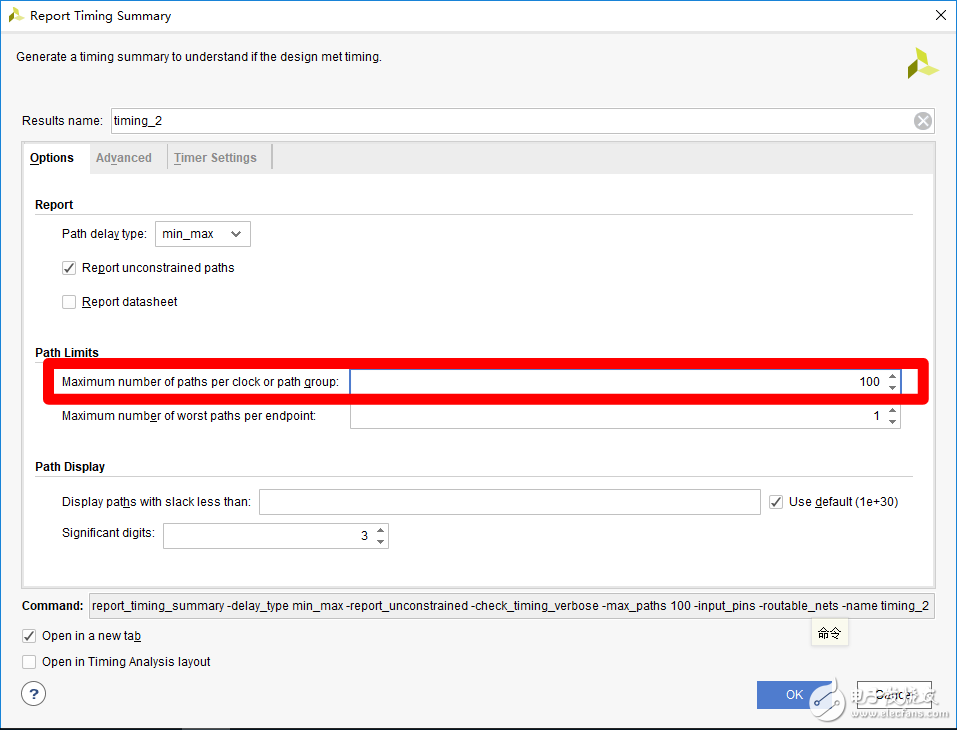

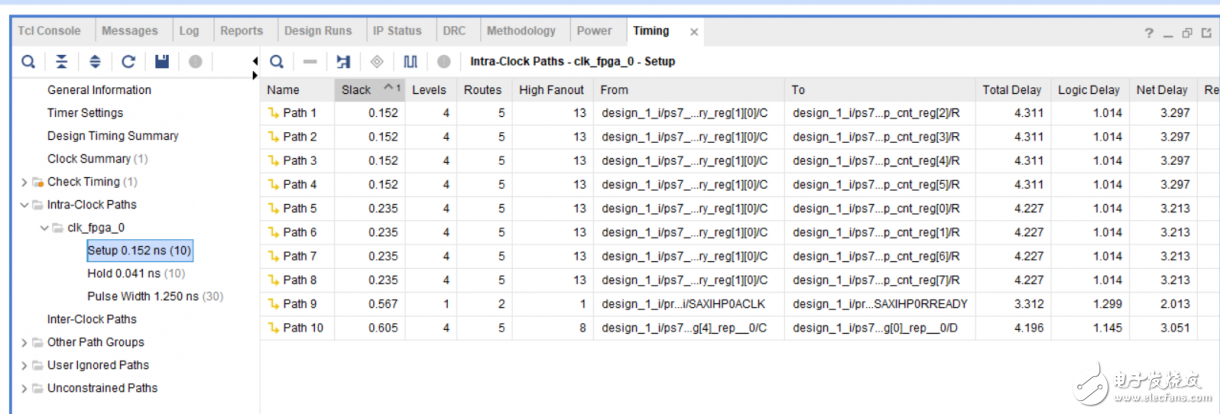

Vivado运行Report Timing Summary时,只显示各个子项目最差的十条路径,很可能并不包含你最关心的路近,这个时候显示指定路径的时序报告就显得很重要了,下面就简单介绍一下

2021-01-15 16:57:55

的。来获取关于原始的 ISE 设计套件以及 Xilinx 在 Vivado 中对这些开发工具做改进的理由的讨论。值得重申的是,Vivado 支持 7 系列和 Zynq-7000 以及之后的设备,但是

2021-01-08 17:07:20

嗨,您能告诉我与vivado时序分析相关的用户指南吗?谢谢

2020-03-16 08:14:45

vivado软件的安装教程以及license

2023-12-21 19:50:00

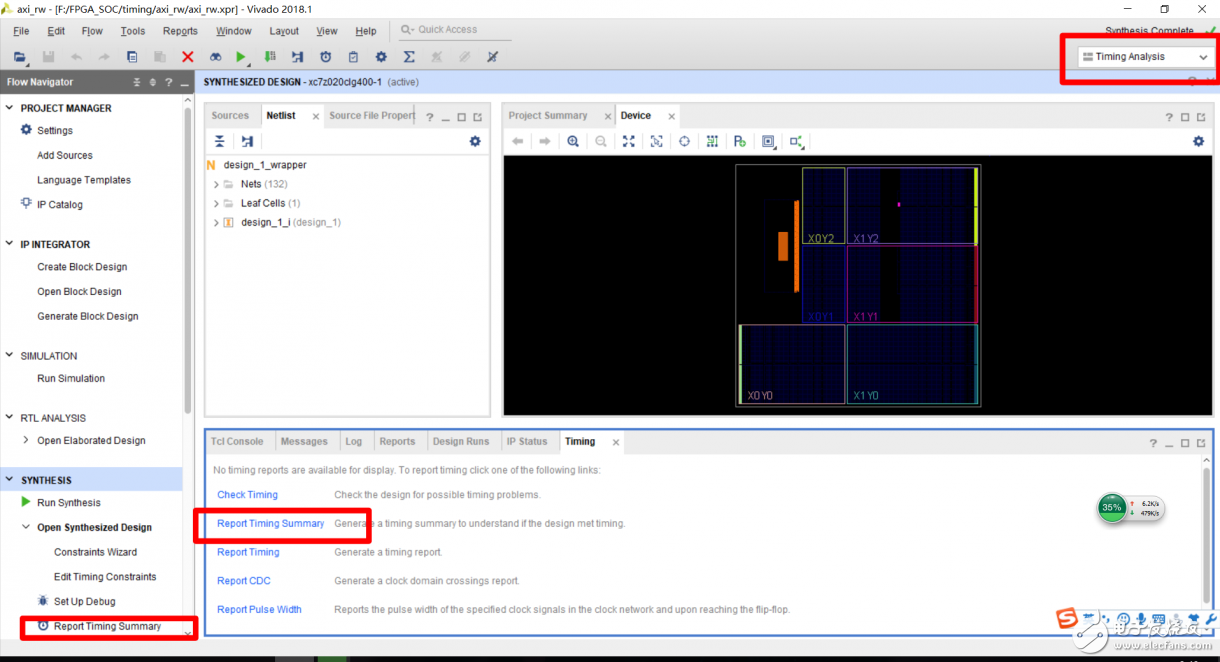

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

1、FPGA中的时序约束--从原理到实例 基本概念 建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。 电路中的建立时间和保持时间其实跟生活中的红绿灯很像

2022-11-15 15:19:27

关于静态分析和时序约束的文章

2014-07-17 12:12:35

设计的验证平台,以此来提高工作效率。论文介绍了FF-DX地址计算部件的时序建模和静态时序分析方法。在静态时序分析之后,将SDF文件中的延时信息反标到逻辑网表中,通过动态时序验证进一步保证设计的时序收敛

2011-12-07 17:40:14

关于车载信息中心电路保护措施的介绍与分析

2021-05-14 07:12:04

关于时序逻辑等效性的RTL设计和验证流程介绍。

2021-04-28 06:13:14

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

FPGA时序相关的资料。都看完看懂时序就没问题了。分了三个附件:第一个是通过一些例子教你如何搞定时序分析。第二个附件是网上各种大神们对时序的理解,主要是他们的博客链接以及网站链接。第三个是其他的一些零散的关于时序的资料。

2012-11-12 17:45:28

FPGA中几个基本的重要的时序分析参数介绍(fmax\tsu\th\tco\tpd)今天无聊,翻开书偶看到介绍时序部分的东西,觉得其中几个参数缩写所代表的含义应该记住,故写如下文章……FPGA中

2012-04-09 09:41:41

约束文件(XDC文件),它包含用于时序分析的“create_clock”和“set_input_jitter”约束。在ISE 14.7和Spartan-3 FPGA中,我可以使用称为“时钟向导”的IP来

2019-08-02 09:54:40

本手册通过一个示例工程,讲解了使用 TD 和 Vivado 下时序约束的对比,详细对比了时序约束的命令、时序约束结果的展示以及部分时序路径。

2022-10-27 06:21:47

嗨,我们正在尝试使用Vivado工具链手动路由FPGA,并想知道应该使用什么工具来手动路由Virtex 7 FPGA。还可以在Vivado时序分析器工具中指定温度和电压值来估算设计时序吗?我们将如

2018-10-25 15:20:50

`基于 FPAGxilinx vivado 仿真模式介绍本文介绍一下xilinx的开发软件 vivado 的仿真模式, vivado的仿真暂分为五种仿真模式。分别为:1. run

2018-01-24 11:06:12

FPGA外部的芯片,可能是FPGA内部的硬核。对于FPGA design来说,必须要关注在指定要求下,它能否正常工作。这个正常工作包括同步时序电路的工作频率,以及输入输出设备的时序要求。在FPGA

2019-07-09 09:14:48

静态时序分析STA是什么?静态时序分析STA的优点以及缺点分别有哪些呢?

2021-11-02 07:51:00

关于多参数土壤分析仪的参数详细介绍【云唐科器】土壤是植物生长的基础,养分含量决定了作物的产量和质量。在农业生产过程中,有必要做好土壤养分的检测。传统的测试方法

2021-03-15 16:29:36

Cadence高速PCB的时序分析:列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的时序分析 1.引言 时序分析,也许是 SI 分析中难度最大的一部分。我怀着满腔的期许给 Cadence 的资深工程师发了一封 e-mail,希望能够得到一份时序分析的案

2010-04-05 06:37:13 0

0 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 在讨论时序逻辑电路的分析与设计之前,让我们先回顾一下在第四章中介绍过的时序电路结构框图和一些相关术语。时序电路的结构框图如图5.1所示.。

2010-08-13 15:24:35 69

69 跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这

2010-09-15 10:48:06 1461

1461

介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 讨论了静态时序分析算法及其在IC 设计中的应用。首先,文章讨论了静态时序分析中的伪路径问题以及路径敏化算法,分析了影响逻辑门和互连线延时的因素。最后通过一个完整的IC 设计

2011-12-20 11:03:16 95

95 DDR_SDRAM介绍和时序图,DDR_SDRAM介绍和时序图

2016-02-23 11:58:38 6

6 静态时序分析基础及应用

2017-01-24 16:54:24 7

7 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

高速数字电路互连时序模型与布线长度分析 高速电路设计领域,关于布线有一种几乎是公理的认识,即等长走线,认为走线只要等长就一定满足时序需求,就不会存在时序问题。本文对常用高速器件的互连时序建立模型

2017-10-15 10:24:53 1

1 过程必须以满足XDC中的约束为目标来进行。那么: 如何验证实现后的设计有没有满足时序要求? 如何在开始布局布线前判断某些约束有没有成功设置? 如何验证约束的优先级? 这些都需要用到Vivado中的静态时序分析工具。

2017-11-17 18:03:55 34003

34003

时序分析基本概念介绍——STA概述,动态时序分析,主要是通过输入向量作为激励,来验证整个设计的时序功能。动态时序分析的精确与否取决于输入激励的覆盖率,它最大的缺点就是速度非常慢,通常百万门的设计想全部覆盖测试的话,时间就是按月来计算了。

2017-12-14 17:01:32 27851

27851

时序分析基本概念介绍——时序库Lib。用于描述物理单元的时序和功耗信息的重要库文件。lib库是最基本的时序库,通常文件很大,分为两个部分。

2017-12-15 17:11:43 10427

10427

时序分析基本概念介绍——Timing Arc

2018-01-02 09:29:04 23487

23487

在实际工程中,如何利用好这一工具仍值得考究。本文将介绍使用Vivado HLS时的几个误区。

2018-01-10 14:33:02 19813

19813

本文介绍一下xilinx的开发软件 vivado 的仿真模式, vivado的仿真暂分为五种仿真模式。 分别为: 1. run behavioral simulation-----行为级仿真,行为

2018-05-29 13:46:52 7674

7674 来维持吗? 1、Vivado基本操作流程 2、时序基本概念 3、时序基本约束和流程 4、Baselining时序约束 5、CDC时序约束 6、I/O时序 7、例外时序约束 8、时序收敛优化技术

2018-08-06 15:08:02 400

400 今天我们要介绍的时序分析概念是ETM。全称extracted timing model。这是在层次化设计中必须要使用的一个时序模型文件。由block owner产生,在顶层设计使用。

2018-09-24 19:30:00 16300

16300

平时用得可能比较少,是PT产生的一个spice信息文件,可以用来和HSPICE做correlation。我们平时使用PT做得是gate level的时序分析,如果想做transistor level的时序分析,那可以采用HSPICE做电路仿真。

2018-09-23 16:52:00 6170

6170 了解Vivado设计套件中的一些广泛的设计分析功能,旨在识别可能影响性能的设计中的问题区域。

2018-11-27 07:10:00 4613

4613 了解report_design_analysis,这是一个新的Vivado报告命令,可以独特地了解时序和复杂性特征,这些特性对于分析时序收敛问题很有价值。

2018-11-26 07:01:00 3314

3314 今天我们要介绍的时序分析概念是Combinational logic. 中文名组合逻辑单元。这是逻辑单元的基本组成器件。比如我们常见的and, or, not, nand,nor等门电路。

2019-05-14 17:27:07 5391

5391

时序分析是以分析时间序列的发展过程、方向和趋势,预测将来时域可能达到的目标的方法。此方法运用概率统计中时间序列分析原理和技术,利用时序系统的数据相关性,建立相应的数学模型,描述系统的时序状态,以预测未来。

2019-11-15 07:02:00 2570

2570

关于Vivado Dashboard的功能可阅读这篇文章(Vivado 2018.3这个Gadget你用了吗)Vivado 2019.1的Dashboard功能进一步增强。

2019-06-12 14:49:24 7677

7677

此次研讨会为该系列的第一期,旨在深入剖析 Vivado 高速时序收敛技术。另外我们还将总结高速设计面临的挑战,介绍设计分析、设计向导以及设计复杂性和拥塞的分析方法。

2019-07-31 17:54:28 2093

2093 交互式时钟域的交叉分析:该功能支持设计人员在设计早期阶段调试CDC问题。结合Vivado设计套件的交互式时序分析和交叉探测特性,CDC分析功能可提供强大的时序分析和调试功能,并加速产品上市进程。

2019-08-01 09:14:54 1862

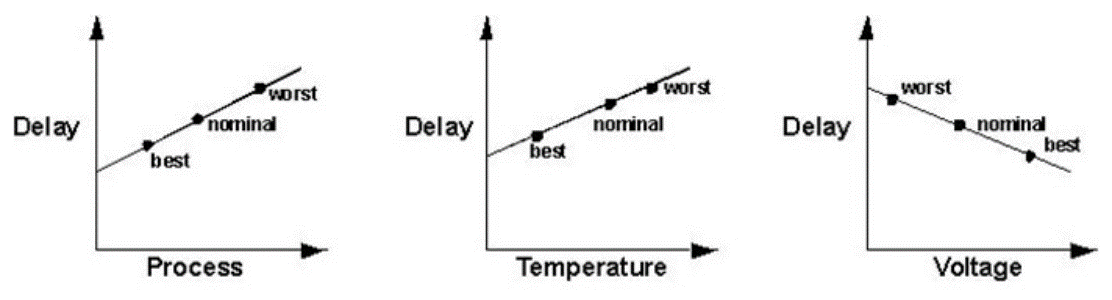

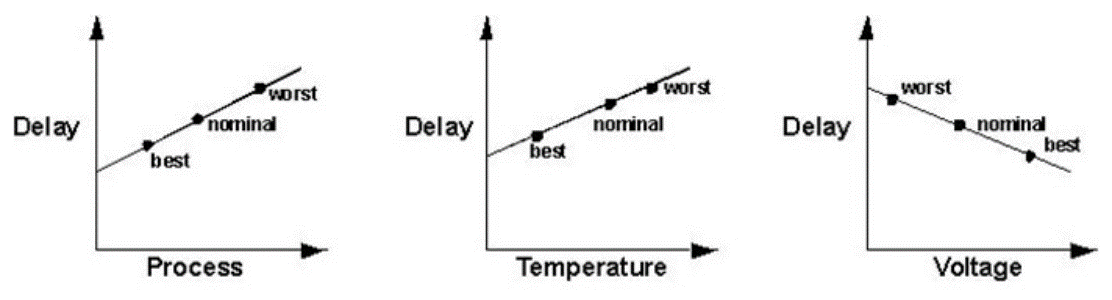

1862 即便是同一种FF,在同一个芯片上不同操作条件下的延时都不尽相同,我们称这种现象为OCV(on-chip variation)。OCV表示的是芯片内部的时序偏差,虽然很细小,但是也必须严格考虑到时序分析中去。

2019-07-25 11:22:30 4462

4462

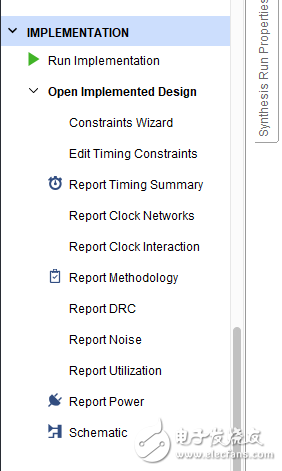

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

2020-03-08 17:17:00 19067

19067

BY Hemang Divyakant Parikh 有多种类型的时序违例可归类为脉冲宽度违例。 - 最大偏差违例(详见 此处 ) - 最小周期违例(本文详解之重点)。 - 最大周期违例

2020-11-19 13:48:45 4673

4673

1 I/O延迟约束介绍 要在设计中精确建模外部时序,必须为输入和输出端口提供时序信息。Xilinx Vivado集成设计环境(IDE)仅在FPGA边界内识别时序,因此必须使用以下命令指定超出这些边界

2020-11-29 10:01:16 4315

4315 静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 本文档的主要内容详细介绍的是时序分析的静态分析基础教程。

2021-01-14 16:04:00 14

14 本文档的主要内容详细介绍的是时序分析的Timequest教程免费下载。

2021-01-14 16:04:00 3

3 本文档的主要内容详细介绍的是时序分析的Timequest教程免费下载。

2021-01-14 16:04:00 15

15 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 17

17 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 19

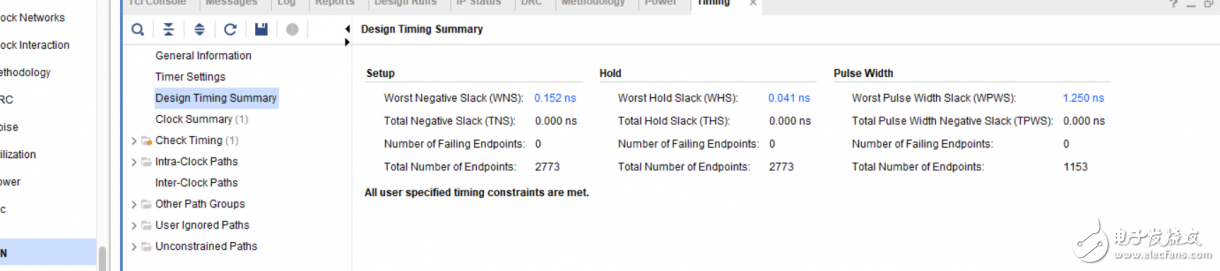

19 在Vivado中分析时序问题的原因(不在本篇中详细讨论), 并根据时序失败的原因调整Vivado各个步骤的选项。有时我们也需要调整Vivad

2021-07-28 10:12:47 1758

1758

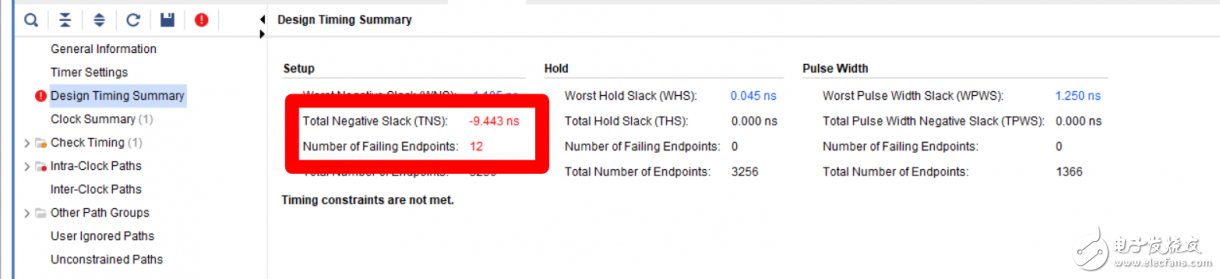

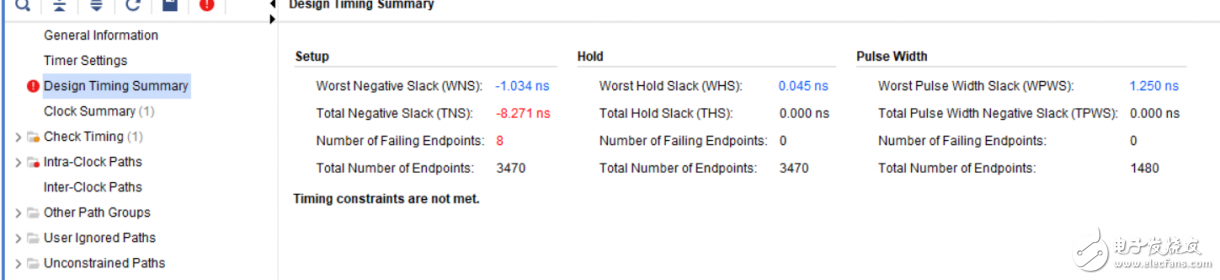

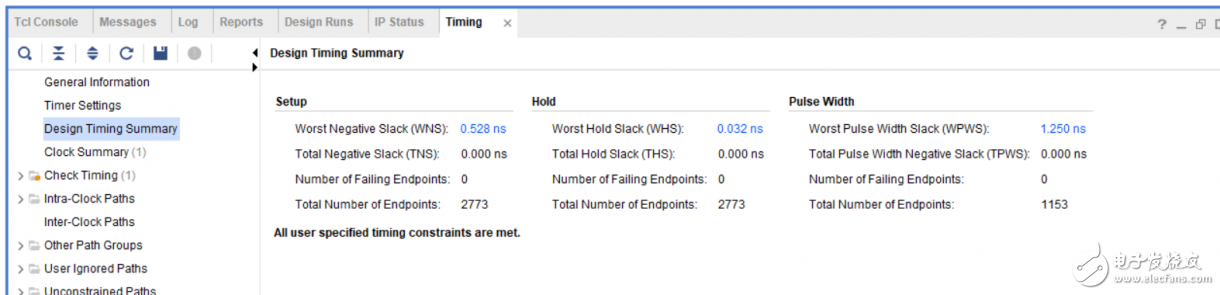

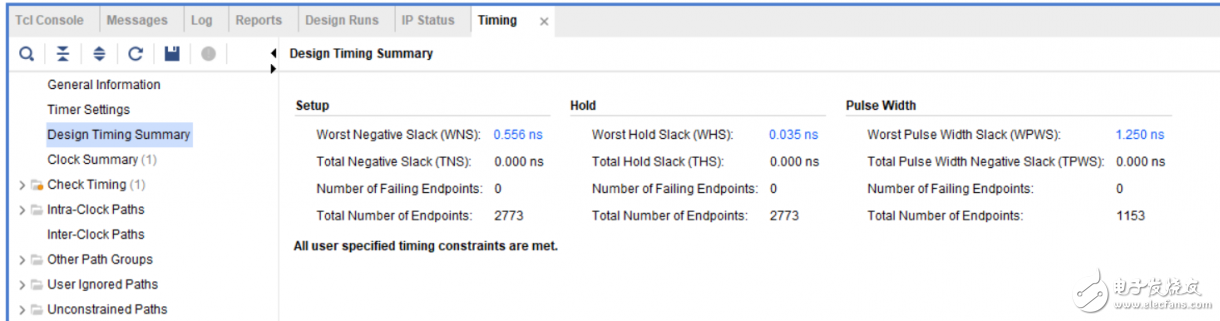

VIVADO中时序报告中WNS,WHS,TNS,THS含义运行“report_timing”或“report_timing_summary”命令后,会注意到 WNS、TNS、WHS 和 THS

2021-10-21 14:32:35 18650

18650

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 关于红外通信原理时序图介绍,帮助单片机写代码程序

2022-06-26 09:25:11 0

0 要从时序分析删除一组路径,如果您确定这些路径不会影响时序性能(False 路径),可用FROM-TO 约束以及时序忽略 (TIG) 关键字。

2022-08-02 08:57:26 517

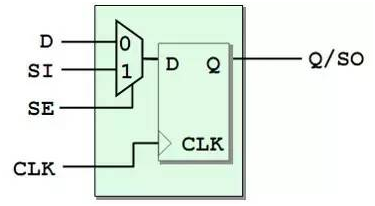

517 组合逻辑和时序逻辑电路是数字系统设计的奠基石,其中组合电路包括多路复用器、解复用器、编码器、解码器等,而时序电路包括锁存器、触发器、计数器、寄存器等。 在本文中,小编简单介绍关于时序电路的类型和特点等相关内容。

2022-09-12 16:44:00 7234

7234

前言 在上篇文章里《时序分析基本概念(一)——建立时间》,我们向大家介绍了建立时间的基本概念和计算方法。

2022-10-09 11:59:45 2696

2696 。在【时序分析的原理】章节中,我们介绍了很多原理性的东西,而在本章节,我们将为大家介绍在解决具体问题时该如何向时序分析工具表述清楚我们的意图,从而启动其强大的逻辑锥求解功能来得出我们所关心的时序分析报告。

2022-12-28 15:18:38 1893

1893 对 FPGA 设计的实现过程必须以满足 XDC 中的约束为目标进行。那我们如何验证实现后的设计有没有满足时序要求?又如何在开始布局布线前判断某些约束有没有成功设置?或是验证约束的优先级?这些都要用到 Vivado 中的静态时序分析工具。

2023-05-04 11:20:31 2368

2368

前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

2023-06-23 17:44:00 1260

1260

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-23 17:44:00 531

531

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-26 15:29:05 531

531

向量和动态仿真 。本文将介绍静态时序分析的基本概念和方法,包括时序约束,时序路径,时序裕量,setup检查和hold检查等。 时序路径 同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最

2023-06-28 09:38:57 714

714

今天要介绍的时序分析基本概念是lookup table。中文全称时序查找表。

2023-07-03 14:30:34 667

667

今天我们要介绍的时序分析概念是 **min pulse width** ,全称为最小脉冲宽度检查。这也是一种非常重要的timing arc check,经常用在时序器件或者memory上面。

2023-07-03 14:54:11 1198

1198

今天我们要介绍的时序分析概念是clock gate。 clock gate cell是用data signal控制clock信号的cell,它被频繁地用在多周期的时钟path,可以节省功耗。

2023-07-03 15:06:03 1484

1484

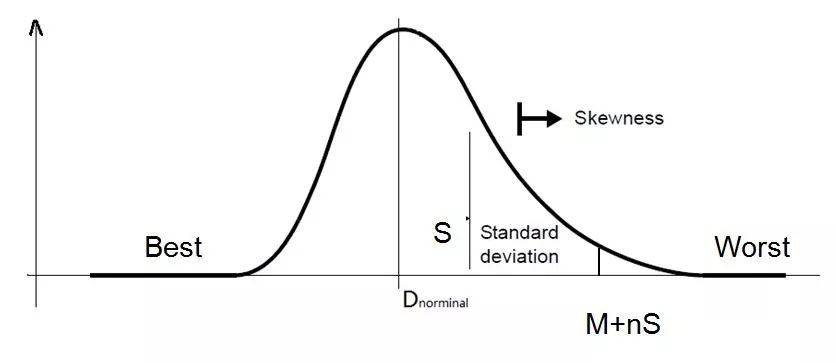

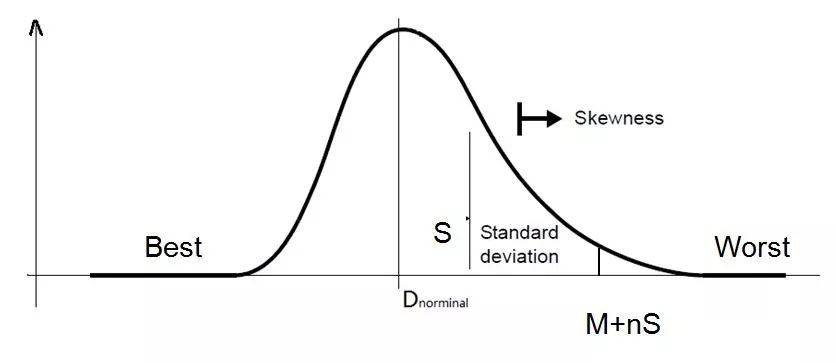

今天我们介绍的时序分析概念是 **SOCV** 。也被叫作POCV,全称为 **Statistic OCV** . 这是一种比AOCV更加先进的分析模式。

2023-07-03 15:19:00 1347

1347

今天我们要介绍的时序分析概念是 **AOCV** 。全称Stage Based Advanced OCV。我们知道,在OCV分析过程中,我们会给data path,clock path上设定单一的timing derate值。

2023-07-03 16:29:05 1164

1164

本文主要介绍了静态时序分析 STA。

2023-07-04 14:40:06 528

528

今天我们要介绍的时序分析基本概念是MMMC分析(MCMM)。全称是multi-mode, multi-corner, 多模式多端角分析模式。这是在先进工艺下必须要使用的一种时序分析模式。

2023-07-04 15:40:13 1461

1461

今天要介绍的时序分析基本概念是skew,我们称为偏差。

2023-07-05 10:29:37 2120

2120

今天要介绍的时序分析基本概念是Slew,信号转换时间,也被称为transition time。

2023-07-05 14:50:53 1530

1530

今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 985

985

今天我们要介绍的时序基本概念是Timing arc,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分时序信息都以Timing arc呈现。

2023-07-06 15:00:02 1397

1397

今天主要介绍的时序概念是时序库lib,全称liberty library format(以• lib结尾),

2023-07-07 17:15:00 1645

1645

今天要介绍的时序基本概念是Mode(模式). 这是Multiple Scenario环境下Sign off的一个重要概念。芯片的设计模式包括最基本的功能function模式,以及各种各样相关的测试模式。

2023-07-10 17:21:38 1721

1721

本文详细介绍了vivado软件和modelsim软件的安装,以及vivado中配置modelsim仿真设置,每一步都加文字说明和图片。

2023-08-07 15:48:00 1478

1478

有些时候在写完代码之后呢,Vivado时序报红,Timing一栏有很多时序问题。

2024-01-05 10:18:36 291

291

电子发烧友App

电子发烧友App

评论