xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同,图一可以说明在7系列里面器件类型和支持的收发器类型以及

2020-11-20 12:08:15 17712

17712

针对PHS系统对手机的新技术需求,锐迪科微电子(RDA)公司开发出基于全新RF收发结构的单芯片收发器及集成天线开关的高效率功放模块。本文介绍RDA PHS射频收发器芯片的设计方法。

2011-12-06 16:52:34 2091

2091

5V RS232 / RS485多协议收发器参考设计,用于全双工RS232(双通道)线路收发器,具有基于LTC1387的SLEW和终端控制5V RS232 / RS485多协议收发器

2020-06-12 07:07:28

5V RS232 / RS485多协议收发器参考设计使用LTC1387 5V RS232 / RS485多协议收发器

2020-06-12 07:42:20

LTC1387:5V RS232 / RS485多协议收发器参考设计,使用基于LTC1387 5V RS232 / RS485多协议收发器的半双工RS232(1通道)线路收发器

2020-06-11 16:13:24

你好我将使用7系列trasnceiver IP来生成我的测试用例。在7系列收发器IP向导中,设置逗号对齐11_0111_1100。在下面,当txdata_in [19:0] = 5'h0037C

2020-08-24 10:07:29

串行异步收发器(UART).51 芯片的串口可以工作在几个不同的工作模式下,其工作模式的设置就是使用SCON 寄存器。它的各个位的具体定义如下:SM0 SM1 SM2 REN TB8 RB8 TI

2021-11-18 06:02:06

和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。

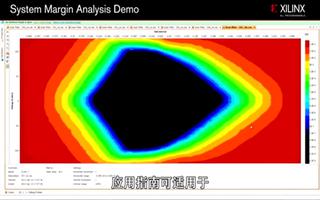

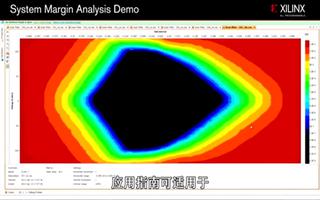

IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT可以获取误码率

2023-06-21 11:23:12

LTC1546是一款带有片上电缆终端的 3 驱动器 / 3 接收器多协议收发器。当与 LTC1544 配合使用时,该芯片组组成了一套完整的软件可选择 DTE或 DCE接口,这支持 RS232

2021-04-15 06:14:36

亲爱的先生,我正在使用Vivado 2015.4。我想在收发器向导中使用通道绑定,但CB在手册中是灰色的。另外,我找不到在收发器向导中启用8b / 10b编码器的方法。如果你能给我一些建议,我将不胜感激。问候,泰迪王

2020-08-04 08:32:57

已知杂散去相关方法实现杂散去相关的收发器功能测量结果

2020-12-21 07:15:38

在CAN通信中,收发器起到了十分相当特别的作用。目前市面的收发器型号也是不计其数,本文则是根据收发器的发展,简单介绍几款收发器的特点。很多年前,NXP的CAN收发器几乎在每一个CAN节点上都看的到,当时最常见的型号就是PCA82C250。

2019-09-03 06:04:44

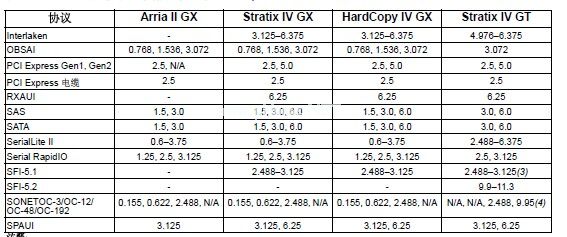

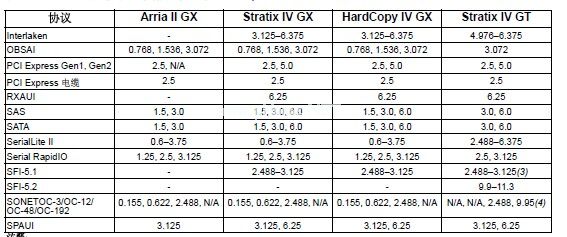

在低成本的 FPGA 中,Cyclone® IV GX 器件内嵌多达八个全双工收发器,运行在 600Mbps 到 3.125 Gbps 的串行数据速率上。 表 1-1 列出了 Cyclone IV GX 收发器通道所支持的串行协议信息。

2017-11-14 10:54:41

微电子(RDA)公司开发出基于全新RF收发结构的单芯片收发器及集成天线开关的高效率功放模块。本文介绍RDA PHS射频收发器芯片的设计方法。

2019-09-20 07:46:19

EM4094是一个集成的收发器芯片,它可用于构建RFID读卡器的模拟前端模块。该芯片的数据传输及接收链路允许传送和解码任何通信协议,因此EM4094支持所有EM公司的13.56MHz收发器芯片

2015-12-22 11:00:31

FPGA高速收发器设计原则高速FPGA设计收发器选择需要考虑的因素

2021-04-09 06:53:02

高速收发器(SERDES)的运用范围十分广泛,包括通讯、计算机、工业和储存,以及必须在芯片与芯片/模块之间、或在背板/电缆上传输大量数据的系统。但普通高速收发器的并行总线设计已无法满足现在的要求。将收发器整合在FPGA中,成为解决这一问题的选择办法。FPGA高速收发器设计时,我们需要注意哪些事项呢?

2019-08-07 06:26:42

嗨,我们计划在不同线路速率的高速收发器线路上接收数据,最低为400Mbps。接收器规范提供的最小线速率为500 Mbps。有没有办法使用400Mbps流使用收发器(例如通过过采样,减少时钟分频器)?目前我们在收发器外使用过采样,但这阻止我们使用内部8b10b解码器和逗号对齐逻辑。谢谢,马蒂亚斯

2020-08-12 06:39:36

LTC1387:5V RS232 / RS485多协议收发器参考设计,使用基于LTC1387 5V RS232 / RS485多协议收发器的半双工RS232(1通道)线路收发器

2020-06-12 14:15:18

nRF51822 蓝牙智能收发器 SoCNordic Semiconductors nRF51822 是 2.4GHz 多协议射频收发器 SoC,用于蓝牙智能和 Nordic Gazell 协议

2019-12-07 15:14:44

RFW102收发器芯片相关资料分享

2021-05-20 07:03:07

EXAR拥有业内唯一的单芯片多协议解决方案和最快的数据速率(高达52Mbps).多协议串行收发器支持业内流行的串行协议-V.10,V.11,V.28(RS232),V.35,V.36(RS-449

2014-09-01 10:22:03

RocketIO收发器怎么实现高速通信?

2021-05-26 06:28:57

我需要能够使用SFP收发器。我想使用收发器向导,但我不知道选择哪些选项。我不确定我的转账率是多少。我知道我需要使用的时钟大约是600MHz。我还需要能够从此收发器恢复时钟。收发器是否有输出时钟?谢谢你的帮助。

2020-04-07 14:39:32

Semtech 的 137-1050 MHz 超低功耗长距离收发器(SX1276 Long Range Transceiver)SX1276 收发器采用 LoRa® 长距离调制解调器,可实现超长

2018-11-26 09:48:37

TI cc1020 低功耗高频收发器CC1020是一种理想的超高频单片收发器芯片。主要用于ISM(工业、科研及医疗)频带和在426/429/433/868/915MHz频带的SRD(Short

2016-03-24 17:07:12

TSS721A是什么?TSS721ADR单芯片收发器有哪些特性?TSS721ADR单芯片收发器有哪些功能?

2021-11-04 06:14:05

这是一mt6169 40nm CMOS多模多频段收发器。射频收发器功能是完全集成的。本文描述了射频宏被嵌入到整个产品中的性能目标。MT6169主要特征区别MT6169是第一个M联ATEK射频收发器1

2018-08-28 19:00:04

?注意:合成频率将在FPGA内部用于读取fifo,但也通过oddr转发到外部芯片。我对在FPGA内部实现dpll的其他方法持开放态度。谢谢。

2020-07-31 10:19:37

亲爱的社区,我开始设计和使用在使用ISE 14.5实现ip-core时提供的GTX收发器示例。我使用带有FM-S14适配器的Kintex Evalboard KC705(为我提供了4个额外的SFP

2020-07-15 09:10:15

嗨,我有2个静态配置的GTX收发器用于HD-SDI操作。我可以使用一个收发器的Txoutclk为两个收发器配备Txusrclock吗?通过这种方式,我可以只用1个Txusrclock为FPGA逻辑

2020-08-19 07:43:50

的 AFCT-5805AZ/AFCT-5805xxZ 单模光纤收发器是符合成本效益的高性能光收发模块,特别适合数据传输速率达 155Mb/s 的串行光纤数据通信应用。这些收发器模块为具有 +3.3V 或 +5.0V

2013-12-24 12:01:48

单模光纤收发器与多模的区别什么是光纤收发器光纤收发器是一种将短距离的双绞线电信号和长距离的光信号进行互换的以太网传输媒体转换单元,在很多地方也被称之为光电转换器或光纤转换器(Fiber

2012-10-15 16:37:06

单模光纤收发器与多模的区别什么是光纤收发器光纤收发器是一种将短距离的双绞线电信号和长距离的光信号进行互换的以太网传输媒体转换单元,在很多地方也被称之为光电转换器或光纤转换器(Fiber

2012-11-21 16:37:43

方案都可以进行正确处理。那么,如何FPGA中利用低频源同步时钟实现低压差分信号(LVDS)接收字对齐呢?

2019-07-29 07:03:50

5V RS232 / RS485多协议收发器参考设计使用LTC1387,用于基于LTC1387的半双工RS485(1通道)线路收发器5V RS232 / RS485多协议收发器

2020-06-11 16:13:24

功能(主要是在线卡上)来实现产品差异化。由于这些串行收发器是专为支持大多数串行背板标准协议而设计的,因此FPGA是实现定制特性的理想平台。串行收发器和交换接口一起允许实现符合标准的设计,并具有增值功能

2019-04-16 07:00:07

高电平。4 结束语实现多协议串口通信的方法很多,不同厂家提供有功能各不相同的串口芯片。设计者可根据自己的需求来选择。当设计一个支持各种物理层协议的复杂DTE/DCE模式时,和使用许多分立的元器件相比,选择一个单片多协议串行收发器将会简化配置,同时所设计的电路也会更灵活、方便和简单。

2019-06-13 05:00:09

如何利用直接变频收发器MAX2837实现WiBro设计?

2021-04-21 06:43:57

如何利用软件模拟的方法去实现串口收发的功能呢?串口收发有哪几种通讯方式呢?

2021-12-14 06:31:49

如何利用集成收发器简化AISG控制系统设计?

2021-05-25 06:12:43

光纤收发器的优势如何区分单纤收发器与双纤收发器?

2021-01-14 07:26:53

嗨,有没有办法在V5的GTP收发器中进行串行环回模式?手册提供了4种环回模式,但它们都涉及解串器之后的路径,我需要通过接收器循环串行数据并在CDR之后将其路由到发送器,而不通过重新锁定的并行路径。这可能吗?谢谢,戴夫

2020-05-27 17:17:02

嗨,大家好,我正在尝试在我的vhdl设计中实现GTP收发器。该设计应该用作两个定制硬件板之间的连接测试。它使用线性反馈移位寄存器来生成比特流,该比特流被打包到数据帧中。在通过链路发送帧之前,发送对齐

2019-07-24 14:10:28

Zarlink Semiconductor公司针对起搏器、神经刺激器、药泵以及其他此类植入式应用医疗设备的一款超低功率RF收发器芯片,其数据传输率高、功耗低,具有独特的唤醒电路。 本文讨论了如何采用这款RF收发器实现体内通信系统的设计。

2021-05-31 06:31:36

Zarlink Semiconductor公司针对起搏器、神经刺激器、药泵以及其他此类植入式应用医疗设备的一款超低功率RF收发器芯片,其数据传输率高、功耗低,具有独特的唤醒电路。本文讨论了如何采用这款RF收发器实现体内通信系统的设计。

2019-07-26 07:22:07

实现了基于FPGA的星形交换接口的10GbE线卡示例。该FPGA例示了一个XAUI LogICORE IP核,并利用4个串行收发器连接至16通道XAUI交换结构卡。此外,该FPGA还具备一个

2019-05-05 09:29:30

/ GTH收发器。我们的目标数据速率为6.25 Gbps。这是更好的方法吗?因为大多数设计实例都有专用的板载时钟振荡器,用于GPS参考时钟。请提供建议以获得更好的性能。

2020-03-18 09:53:15

现代微微蜂窝和微蜂窝无线通信网络需要使用相当多的分立器件,常常超过功耗预算和尺寸限制。典型的微微蜂窝基站RF 收发器除功率放大器(PA)外,还包括6 到8 个有源器件,而微蜂窝基站的器件数量很容易

2019-06-27 06:24:15

永磁交流伺服电机的工作原理是什么?更换新编码器后的常规零位校正方法是什么?永磁交流伺服电机的编码器相位为何要与转子磁极相位对齐?

2021-09-27 08:06:54

求助FPGA高速串行收发器,输出12.5Gbps的信号要用什么电平输出28.5Gbps的信号要用什么电平?

2014-11-10 09:12:51

的相位对齐关系,以此方法可以将传感器的上述信号边沿或过零点对齐到-30度电角度相位; 2) 以阻值范围适当的三个等值电阻构成星形,接入永磁伺服电机的UVW动力线,以示波器观察U相动力线与星形等值电阻

2018-10-25 10:09:31

如何把故障保护偏置应用于闲置总线?老式收发器与新式收发器的区别在哪里?

2021-05-24 07:03:57

项目中使用周期性脉冲信号作为AD9912芯片的IO_UPDATE管脚的输入,可以使AD9912芯片输出的正弦波信号在每个脉冲信号来时重新加载寄存器,实现生成的正弦波信号的初相位与周期脉冲信号对齐,在

2018-12-18 09:06:36

从FPGA1中的GTP传输到FPGA2中的GTP。每个FPGA都有自己的本地收发器参考振荡器。我有两个目标,我想要实现:频率匹配FPGA1和FPGA2上的TXOUTCLK,和即使在重新编程FPGA之后

2020-08-28 06:22:25

标准库3.5实现:《嵌入式-STM32开发指南》第二部分 基础篇 - 第6章串口通信6.1串口简介通用同步异步收发器(USART)提供了一种灵活的方法与使用工业标准NRZ异步串行数据格式的外部设备

2021-08-20 07:37:06

UART是什么?USART又是什么?通用异步收发器与通用同步异步串行接收/发送器有哪些差异呢?

2021-12-10 06:45:46

5V RS232 / RS485多协议收发器参考设计使用LTC1387,用于基于LTC1387的半双工RS485(1通道)线路收发器5V RS232 / RS485多协议收发器

2020-06-12 12:06:32

5V RS232 / RS485多协议收发器参考设计使用LTC1387实现全双工RS485 / RS422(双通道)线路收发器,具有基于LTC1387的SLEW和终端控制5V RS232 / RS485多协议收发器

2020-06-12 09:27:27

集成式RF采样收发器支持快速跳频、多频带和多模式操作

2021-01-15 06:16:48

最新的直接无线射频(RF) - 采样收发器 – 包括德州仪器的AFE7444和AFE7422设备,分别支持四个和两个天线信道 – 提供多种强大功能,使得多种先进的系统特性,如多频带和多模式操作,以及变频和快速跳频成为可能

2019-09-18 06:50:38

本文主要阐述了在某雷达系统中为实现伪码对齐,所采用的滑动控制方法的原理及在FPGA芯片上的实现。

2010-03-02 16:04:22 13

13 介绍了基于CPLD的异步串行收发器的设计方案,着重叙述了用混合输入(包括原理图和VHDL)实现该设计的思想,阐述了在系统可编程(ISP)开发软件的应用方法与

2010-07-19 16:54:19 20

20 介绍了非对称数字用户环路收发器片上系统芯片的组织结构, 对其硬件实现给出了具体描述!

2010-07-22 15:35:28 32

32 采用带有收发器的全系列40-nm FPGA和ASIC实现创新设计

人们对宽带服务的带宽要求越来越高,促使芯片供应商使用更多的高速串行收发器。因此,下一代应用采

2010-02-04 11:06:19 879

879

通用串行总线收发器MIC2550及其应用

摘要:MIC2550是Micrel公司推出的新型单片通用串行总线收发器集成电路。该芯片符合通用串行总线(USB)规

2010-03-03 19:45:05 1493

1493

单芯片RS-232/RS-485/RS-422串行收发器SP336

Exar公司发布了下一代单芯片RS-232/

2010-04-14 16:37:50 1994

1994 近日,多协议串行收发器解决方案领导厂商-Exar公司为其单芯片RS-232/RS-485/RS-422串行收发器再添一款多功能新品- SP337

2010-12-31 09:25:21 964

964 Exar公司为其单芯片RS-232/RS-485/RS-422串行收发器产品家族再添一款多功能产品-SP339。

2011-11-24 09:19:25 1665

1665 了解如何在您的 UltraScale™ FPGA 设计中部署串行收发器。了解并利用串行收发器模块的特性,如 8B/10B 和 64B/66B 编码、通道绑定、时钟校正和逗点检测。其它专题

2017-02-09 08:04:41 327

327 电角度相位对齐的基本方法:1.波形观察法,2.转子定向法

2017-02-10 11:57:52 3233

3233 赛灵思Virtex UltraScale架构全可编程器件的很多特色中的一个是它具有20到60个可用的并且可配置的32.75Gbps GTY双向串行收发器。下面是一些能够匹配使用这些收发器的常用的高速串行接口标准:

2017-02-11 10:07:50 2793

2793

赛灵思(Xilinx)公司FPGA器件的高速串行收发器类别如下

2017-02-11 11:11:30 5958

5958

自动纠偏

2017-08-08 09:26:49 0

0 Martin Gilpatric教您处理在调试收发器设计时常见的一个串行链接问题,

2018-06-01 15:50:00 3284

3284

Join Dave和Bob在短片中介绍两种关键串行接口协议的相似性和差异:控制器局域网(CAN)与RS-485。利用Maxim的一款RS-485接口收发器和最新的CAN收发器,在示波器上观察这两种

2018-10-11 10:26:00 8045

8045 通过Virtex-7 2000T FPGA中的GTX收发器实现高速串行性能。

2018-11-22 06:27:00 3461

3461 以示波器直接观察UV线反电势波形过零点与传感器的U相信号上升沿/Z信号、或Sin信号过零点、或Sin包络信号过零点的相位对齐关系,以此方法可以将传感器的上述信号边沿或过零点对齐到-30度电角度相位。

2019-02-05 11:09:00 8107

8107 UART(Universal Asynchronous Receiver Transmitter通用异步收发器)是一种应用广泛的短距离串行传输接口。常常用于短距离、低速、低成本的通讯中。

2019-08-12 17:46:18 722

722

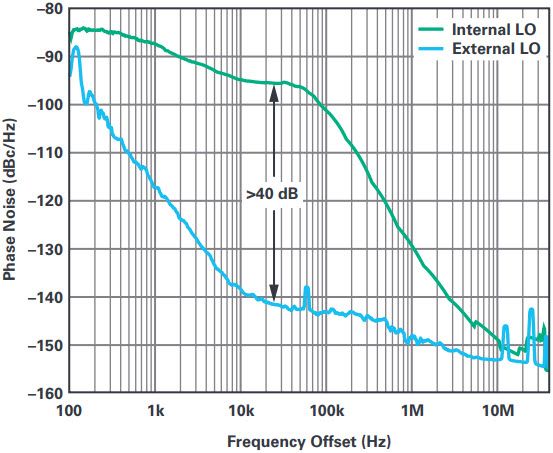

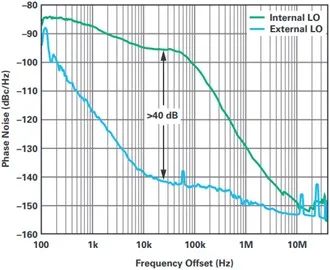

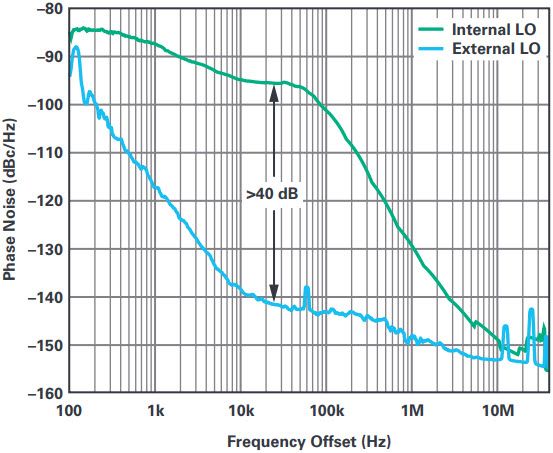

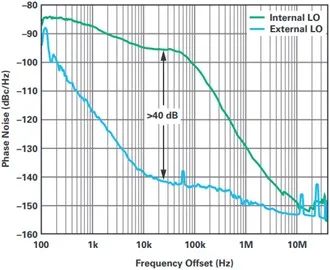

ADI公司ADRV9009收发器使用外部本振(LO)时的测量表明,使用低噪声LO时,相位噪声可以显著改善。收发器架构是从相位噪声贡献的角度提出的。通过一系列测量,残余或加性相位噪声被提取为DAC输出

2022-12-21 11:40:26 1115

1115

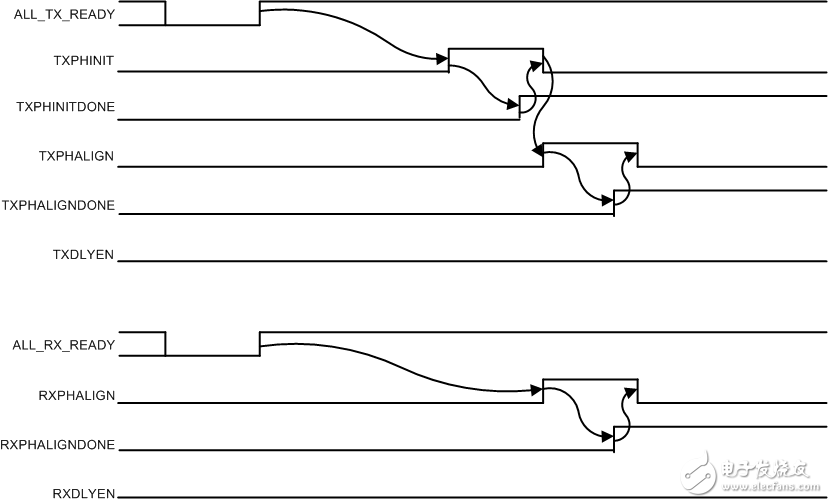

当TX Buffer被使能时,可以通过TXBUFSTATUS的Bit0(Half Full)的状态和TXPIPPM的调整实现TX通道同步。上电后TX通道间的相位和TXBUFSTATUS都处于随机状态,相位超前与延迟以及超前和延迟的UI数量都是不确定的

2023-02-02 10:00:03 1310

1310 使用外部本振(LO)时对ADI公司 ADRV9009 收发器进行测量表明,当使用低噪声LO时,可显著改善相位噪声。从相位噪声贡献角度来分析收发器架构。通过一系列测量,残余或加性相位噪声被提取

2023-03-16 14:33:51 738

738

串行端口收发器是一种用于串行通信的设备,它的作用是将并行数据转换为串行数据,并将串行数据转换为并行数据。它在计算机和通信领域中起着重要的作用。

2023-08-19 10:51:46 307

307 电子发烧友网站提供《2.5Gbps收发器中相位锁定检测电路的设计与仿真.pdf》资料免费下载

2023-11-07 09:43:00 0

0

电子发烧友App

电子发烧友App

评论