赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

2013-07-23 09:25:53 19707

19707

针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2013-11-28 18:49:00 12149

12149

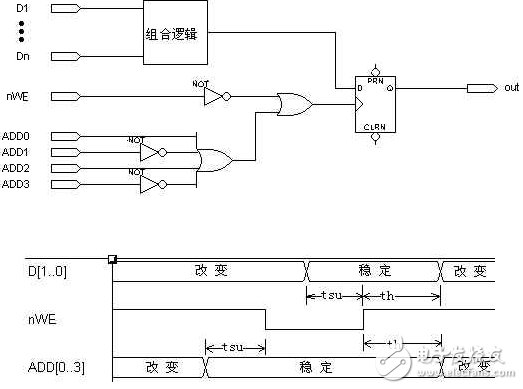

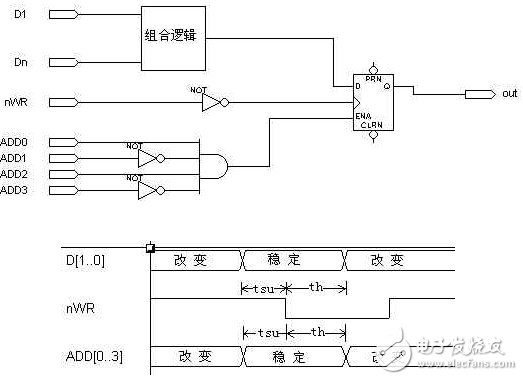

介绍3种跨时钟域处理的方法,这3种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这3招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。 本文介绍的3种方法跨时钟域处理方法如下:

2020-11-21 11:13:01 3278

3278

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期

2020-11-23 13:08:24 3565

3565

,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。赛灵思现有的FPGA中没有一款同时包含这四种资源(见表1)。 这四大类中的每一种都针对特定的应用。例如,数字时钟管理器(DCM)适用于实现延迟锁相环(DLL)、数字频率综合器、数字移相器或数字

2021-02-13 17:02:00 2014

2014

7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 IC测试座常用的封装类型有很多种,以下是一些常见的类型:

2023-06-01 14:05:54 760

760

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功能的时钟缓冲器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 400

400

工作,由于配置时间很短,不会影响系统正常工作。也有少数FPGA采用反熔丝或Flash工艺,对这种FPGA,就不需要外加专用的配置芯片。

四、其他类型的FPGA和PLD

随着技术的发展,在

2023-11-03 11:18:38

欢迎。经过了十几年的发展,许多公司都开发出了多种可编程逻辑器件。比较典型的就是 Altera 公司和Xilinx 公司的 CPLD 器件系列和 FPGA 器件系列,它们开发较早,占用了较大的 PLD

2009-03-28 14:57:08

PLD是小规模集成电路,主要是替代TTL集成电路的可编程逻辑电路FPGA 是大规模集成电路,它是在PLD、PAL、GAL 、CPLD等可编程器件的基础上进一步发展而成的。或者说是经过了几代的升级产品

2018-08-28 09:15:53

FPGA设计重利用方法(Design Reuse Methodology)SRAM工艺FPGA的加密技术大规模FPGA设计中的多点综合技术定点乘法器设计(中文)你的PLD是亚稳态吗_设计异步多时钟系统的综合以及描述技巧使用retiming提高FPGA性能

2014-04-30 23:57:42

1.PLD/FPGA/CPLDPLD(Programmable Logic Device):可编程逻辑器件,数字集成电路半成品,芯片上按照一定的排列方式集成了大量的门和触发器等基本逻辑元件,使用者

2021-07-30 07:26:19

`PLD/FPGA的分类和使用 在PLD/FPGA开发软件中完成设计以后,软件会产生一个最终的编程文件(如 .pof )。如何将编程文件烧到PLD芯片中去呢? 1.对于基于乘积项

2012-02-27 10:42:53

PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相

2009-06-20 10:38:05

,足以满足设计一般的数字系统的需要。目前常用EEPROM,CPLD,FPGA。 PLA,PAL,GAL是早期的可编程器件,已经淘汰。可编程逻辑器件PLD(Programmable Logic Dev...

2021-07-22 09:05:48

作者:张宇清可编程逻辑器件(PLD)的两种主要类型是现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)。根据半导体行业协会提供的数据,PLD现在是半导体行业中增长最快的领域之一,高性能

2019-07-29 08:07:20

可编程逻辑器件(PLD)的两种主要类型是现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)。根据半导体行业协会提供的数据,PLD现在是半导体行业中增长最快的领域之一,高性能PLD现在已经从

2019-07-17 07:19:16

可编程逻辑器件(PLD)的两种主要类型是现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)。根据半导体行业协会提供的数据,PLD现在是半导体行业中增长最快的领域之一,高性能PLD现在已经从

2019-07-22 06:51:56

网友们好象没人提过PLD的话题,我感觉是对这个东西不太熟,其实PLD是大有用武之地的,其优势在于:1、可以很灵活的实现各种“与、或、非”逻辑功能;2、任何复杂的逻辑运算都是一步完成,避免产生额外

2012-11-19 20:41:23

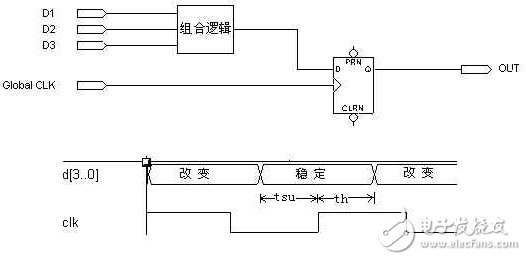

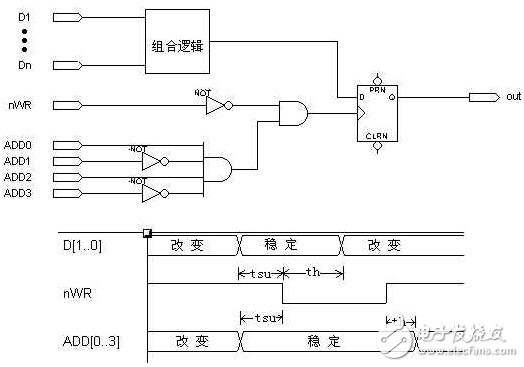

很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。1.全局时钟对于一个设计项目

2012-12-14 16:02:37

.其他类型的FPGA和PLD 随着技术的发展,在2004年以后,一些厂家推出了一些新的PLD和FPGA,这些产品模糊了PLD和FPGA的区别。例如Altera

2008-05-20 09:46:10

单片机的开发过程是怎样的?常用的单片机类型有哪些?

2021-09-27 06:12:32

时钟元件是什么?时钟元件的原理是什么?有哪些类型?

2021-06-08 06:21:38

请问PCBA基板有哪些常用的类型有哪些?

2020-03-13 15:38:59

/FPGA产品60%以上是由Altera和Xilinx提供的。可以讲Altera和Xilinx共同决定了PLD技术的发展方向。当然还有许多其它类型器件,如:Lattice,Vantis,Actel

2012-02-27 11:52:00

从FPGA或PLD转换到门阵会遇到哪些时序问题?如何去避免这些问题的发生?

2021-04-30 06:54:18

,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。赛灵思现有的FPGA中没有一款同时包含这四种资源(见表1)。 这四大类中的每一种都针对特定的应用。例如,数字时钟管理器

2020-04-25 07:00:00

)两类功能,瞬时逻辑主要是指与、或、非及其混合运算,输出结果对输入条件能即时响应;延时逻辑一般由时钟信号驱动,主要实现寄存器、计数器以及与十序有关的逻辑功能。 最简单的PLD器件一般有8个专用输入端和8

2012-10-30 23:39:54

在分析电路时常用的定理有哪些

2021-03-11 06:33:09

作者:Altera公司 Tam Do

从便携媒体播放器和手机,到视频游戏控制台,消费类视频应用的迅速增长需要大量不同的接口和适配器,以使用户在其电脑和各种娱乐信息设备间相互传输视频数据。

常用

2018-12-28 07:00:06

的进化。之后,SPLD、CPLD和FPGA在20世纪80年代早期发展起来。表9.2 PLD分类PLD分类如表9.2所示。以下是用于理解现场可编程设备的关键术语。PAL是一种密度相对较小的现场可编程

2022-10-27 16:43:59

可编程逻辑器件(PLD)的两种主要类型是现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)。根据半导体行业协会提供的数据,PLD现在是半导体行业中增长最快的领域之一,高性能PLD现在已经从

2019-09-24 06:58:39

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。

2019-09-18 08:26:21

什么叫电源?电源有哪些分类?常用的电源类型?

2021-03-16 14:40:58

请问一下平时在工程设计中Xilinx的FPGA常用,还是使用Altera的FPGA 常用?

2021-06-23 06:30:20

Multiple Clock System Design PLD设计技巧—多时钟系统设计

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 用单片机配置FPGA—PLD设计技巧

Configuration/Program Method for Altera Device

Configure the FLEX Device

You

2008-09-11 09:36:56 23

23 基于PLD及FPGA的频率与相位测量系统设计与实现:摘 要:本测量系统由频率相位测量仪和DDS 双路移相信号发生器两部分组成。频率相位测量由Altera EPM7128S84 CPLD 完成,双路移相信号

2009-09-25 15:50:03 30

30 影响FPGA设计中时钟因素的探讨:时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时

2009-11-01 14:58:33 26

26 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 FPGA,CPLD和其它类型PLD的结构各有其特点和长处,但概括起来,它们是由三大部分组成的:(1)一个二维的逻辑块阵列,构成了PLD器件的逻辑组成核心;(2)输入/输出块;(3)连

2009-12-02 15:19:40 24

24 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 提出了一种基于FPGA的时钟跟踪环路的设计方案,该方案简化了时钟跟踪环路的结构,降低了时钟调整电路的复杂度。实际电路测试结果表明,该方案能够使接收机时钟快速准确地跟踪发

2010-11-19 14:46:54 31

31 PLD/FPGA新手入门知识

PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相

2009-06-20 10:31:05 896

896

什么是PLD(可编程逻辑器件)

PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)

2009-06-20 10:32:32 14283

14283

大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 645

645

理解不同类型的时钟抖动

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误

2010-01-06 11:48:11 1608

1608

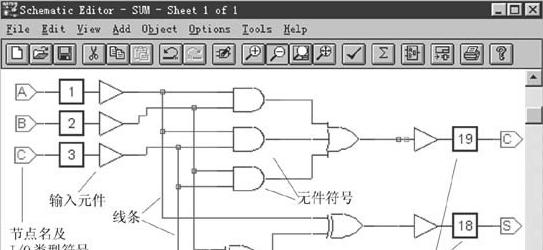

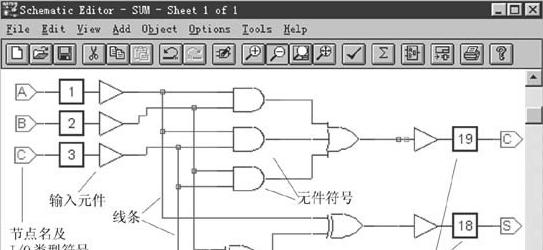

PLD设计方法及步骤 1、PLD器件的设计步骤

1.电路逻辑功能描述

PLD器件的逻辑功能描述一

2010-09-18 09:08:30 4151

4151

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 3472

3472

在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进行了功能验证. 由于数字时钟的通用

2011-11-29 16:51:43 178

178 PLD、FPGA优秀设计的十条戒律, 该文浅显易懂的介绍了一个优秀设计必须考虑的问题,给出了设计方法和建议。仔细阅读和消化本文,对提高PLD/FPGA设计水平大有裨益

2012-01-17 10:32:59 61

61 今天我们将带领大家完成你的第一个PLD设计,即使你从没有接触过PLD,也可以让你可以在十分种之内初步学会PLD设计! 不信? 呵呵 我们慢慢往下看。 实验目的 我们分别采用VHDL、Verilog

2012-05-18 16:29:52 1124

1124 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1100

1100

电子发烧友网整理: 本文主要描述可编程逻辑器件的类型及其优点,希望能给初学者们一点帮助。可编程逻辑器件的英文全称为:programmable logic device 即PLD。PLD是做为一种通用集成电路

2012-06-08 11:14:11 5037

5037 。PLD可分为简单PLD和复杂PLD,其中复杂PLD又包括CPLD和FPGA。在本专题我们将主要介绍CPLD和FPGA的相关技术知识。

2012-06-16 22:13:38

DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 HL配套C实验例程100例之定时器定时常用参数,配合开发板学习效果更好。

2016-04-11 16:09:41 3

3 常用的FPGA代码,VHDL语言编写。需要请下载

2016-05-26 11:36:16 16

16 基于FPGA的数字时钟设计,可实现闹钟的功能,可校时。

2016-06-23 17:15:59 64

64 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚,不能用N类型管脚等等。

2017-02-11 03:48:34 10684

10684

PLD(Programmable Logic Device)是可编程逻辑器件的总称。早期的PLD多属于EEPROM或乘积项(Product Term)结构。FPGA(Field

2017-06-19 09:59:13 3996

3996 介绍3种跨时钟域处理的方法,这3种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这3招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。 本文介绍的3种方法跨时钟域处理方法如下:打两拍;异步双口RAM;格雷码转换。

2017-11-15 20:08:11 13066

13066 PLD/FPGA 常用开发软件maxplus2crack。 Altera公司的免费PLD开发软件Altera公司的免费PLD开发软件,界面与标准版的MaxplusII完全一样,只支持MAX7000

2017-11-26 11:19:26 4

4 PLD/FPGA 常用开发软件System Generator 9.10。 业内领先的高级系统级FPGA开发高度并行系统。

2017-11-26 11:34:56 12

12 关键词:FPGA , PLD 讲过了独立按键检测,理所当然应该讲讲FPGA中矩阵键盘的应用了。这个思维和电路在FPGA中有所不同,在此,在此做详细解释,Bingo用自己设计的成熟的代码作为案例,希望

2018-09-26 07:54:02 225

225 跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 2854

2854 时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18 5065

5065

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 2550

2550 跨时钟域处理的方法,这三种方法可以说是 FPGA 界最常用也最实用的方法,这三种方法包含了单 bit 和多 bit 数据的跨时钟域处理,学会这三招之后,对于 FPGA 相关的跨时钟域数据处理便可以手到擒来。 这里介绍的三种方法跨时钟域处理方法如下: 打两

2022-12-05 16:41:28 1324

1324 对于 FPGA 来说,要尽可能避免异步设计,尽可能采用同步设计。 同步设计的第一个关键,也是关键中的关键,就是时钟树。 一个糟糕的时钟树,对 FPGA 设计来说,是一场无法弥补的灾难,是一个没有打好地基的楼,崩溃是必然的。

2020-11-11 09:45:54 3656

3656 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 是最佳的,然后通过使用适当的I/O和时钟缓冲器来访问这些时钟路由资源。该章节包括: 时钟缓冲选择考虑 时钟输入管脚 1.时钟缓冲器选择考虑 7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求

2021-03-22 10:16:18 4353

4353

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 常用OP电路的类型介绍。

2021-05-31 10:46:38 24

24 编程数据存储单元以阵列形式分布在FPGA中,一般把所有超过某一集成度PLD器件都称为CPLD。 编程数据流由开发软件自动生成,数据以串行方式移入移位寄存器围绕一个可编程互连矩阵构成,对于可编程逻辑器件PLD能完成任何数字器件的功能。

2021-10-01 09:17:00 6160

6160 减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2021-09-23 16:39:54 2763

2763 (10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 (08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA时钟设计原则1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟设计原则5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 (29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:48 10

10 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 今天浩道跟大家分享硬核网络故障排错干货,主要针对网络丢包时常用的排错思路。让你遇到网络丢包时,不再迷茫!

2022-10-24 09:20:47 1090

1090 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 686

686

PLD(Programmable Logic Device)是一种由用户根据需要而自行构造逻辑功能的数字集成电路。目前主要有两大类型:CPLD(Complex PLD)和FPGA(Field Programmable Gate Array)。

2023-04-29 16:46:00 1118

1118 FPGA多bit跨时钟域适合将计数器信号转换为格雷码。

2023-05-25 15:21:31 1953

1953

常用直线模组的类型

2023-07-29 17:45:32 902

902

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2023-08-23 16:10:01 336

336 FPGA输入的时钟信号必须是方波么?正弦波会有影响么? FPGA是一种可编程逻辑器件,通常用于实现数字电路。输入时钟信号是FPGA中非常重要的时序信号,对整个系统的稳定性和性能都有很大

2024-01-31 11:31:42 1244

1244

电子发烧友App

电子发烧友App

评论