为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 14342

14342

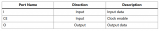

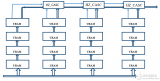

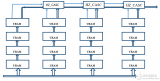

针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2013-11-28 18:49:00 12149

12149

引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。

2022-07-14 09:15:35 1538

1538 )是最常用的时钟布线资源。这些真正的全局时钟可以连接到器件的任何位置。但是在某些情况下,出于性能、功能或时钟资源可用性的原因,使用备用时钟缓冲器更为有利。最好在以下情况下使用BUFG:

2022-07-22 09:40:25 2475

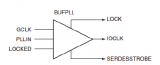

2475 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 EFX_GBUFCE既可以让GPIO走全局时钟网络也可以用于为时钟添加使能控制,当并不是随时需要该时钟时可以把时钟禁止以节省功耗。

2023-05-12 09:53:38 562

562

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

XILINX FPGA/CPLD ISE下载教程 第一章 XILINX FPGA/CPLD ISE下载教程——下载.bit文件第二章 XILINX FPGA/CPLD ISE下载教程——烧录Flash 图文详细资料!

2019-08-15 00:32:31

Xilinx原语使用方法

2021-02-22 06:55:53

Xilinx_fpga_设计:全局时序约束及试验总结

2012-08-05 21:17:05

我看到别人写的项目 程序中用了很多原语,比如输入时钟要设置一个IBUFG,有一些输出信号接一个OBUFG,那么原语的好处是什么?如何知道什么时候要使用原语!

2017-07-13 19:59:37

找到任何关于算法类型和基元类型的约束。如果有,我将使用更少的BRAM资源。Xilinx是否具有用于推断RAM的算法类型和原语类型?我使用的是Vivado 2014.4和Kintex-7设备。 谢谢大家。

2020-03-31 07:45:01

`[tr=transparent]BUFMUX原语是2输入1选择1输出,现在我想改成2位位宽的s选择信号,达到一个四输入的BUFMUX,请问有什么办法可以实现,如果级联?图片最下面这个控制信号是2位的[/tr]`

2018-03-23 15:18:46

`BUFMUX原语是2输入1选择1输出,现在我想改成2位位宽的s选择信号,达到一个四输入的BUFMUX,请问有什么办法可以实现,如果级联?图片最下面这个控制信号是2位的`

2018-03-23 15:12:31

全局时钟资源怎么使用?全局时钟资源的例化方法有哪几种?

2021-05-06 07:28:18

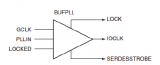

个数字时钟管理模块(DCM)。与全局时钟资源相关的原语常用的与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等。

2019-10-22 06:01:34

设计的要求,一般在FPGA 设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部

2014-11-24 17:58:10

延迟锁相环(DLL)的数目不断增加,最新的Virtex II器件最多可以提供16个全局时钟输入端口和8个数字时钟管理模块(DCM)。与全局时钟资源相关的原语常用的与全局时钟资源相关的Xilinx器件

2015-03-09 19:48:54

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

,这个时间差过大是很要命的。因此,FPGA器件内部设计了一些称之为“全局时钟网络”的走线池。通过这种专用时钟网络走线,同一时钟到达不同寄存器的时间差可以被控制到很小的范围内。而我们又如何能保证输入的时钟

2019-04-12 01:15:50

用于xilinx ML507的Xilinx顶点XC5VFX70TFFG1136 FPGA如何将xilinx LUT作为移位寄存器?什么是xilinx ML507的Xilinx顶点XC5VFX70TFFG1136 FPGA的CLB结构。这个FPGA上有哪些额外的原语?

2020-06-16 16:48:59

FPGA的全局时钟是什么?什么是第二全局时钟?在FPGA的主配置模式中,CCLK信号是如何产生的?

2021-11-01 07:26:34

(30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2022-02-23 06:32:02

(29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2022-02-23 07:27:45

FPGA时钟问题 2010-06-11 15:55:39分类: 嵌入式1.FPGA的全局时钟是什么?FPGA的全局时钟应该是从晶振分出来的,最原始的频率。其他需要的各种频率都是在这个基础上利用PLL或者其他分频手段得到的。

2021-07-29 09:25:57

寄存器资源的使用。如果某个寄存器是用Xilinx的硬件原语指定的,那么就不会被删除。默认为使能。【Register Balancing】:寄存器配平。该参数仅对FPGA有效,用于指定是否允许平衡寄存器

2012-02-24 10:44:57

本文档介绍了时钟资源的功能、原语定义及使用方法。

2022-09-28 08:08:02

SelectIO接口使用IDDR原语执行4x异步过采样。时钟由MMCM或PLL原语生成,并通过BUFG时钟网络路由,并可使用器件内任何选定的输入对单端或差分信号进行操作。XAPP523是由MMCM

2020-08-11 10:59:59

有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;第二类是长线资源,用以完成芯片Bank 间的高速信号

2012-03-08 11:03:49

原语只用用全局时钟处理,不能作为接口使用。也不知道有什么办法可以解决??(2)在用计数器分频后的信号做为下级的时钟信号时间好像也会有警告 生成了 门控时钟,这个问题好像在与计数器分频后的信号不能在做分支同时给于下面几级做时钟信号,这样可能会在级点上产生逻辑门电路吧。

2015-06-16 19:34:01

613.10.2 例化核生成器模块613.11 属性和约束623.12 全局时钟缓冲643.13 高级时钟管理663.14 专用的全局置位/复位资源703.15 隐含编码703.16 输入和输出的实现

2012-04-24 09:18:46

中断向量表里全局中断是什么意思,能解释下吗

2017-04-07 21:36:27

我需要在Spartan6器件中实现一些从1到256的可编程时钟分频器。我的第一个想法是通过一个简单的过程(基本上是一个二进制计数器)实现一个从2到256的分频器,然后使用aBUFGMUX来选择输入时钟

2019-07-31 10:10:31

我有一个关于多个Xilinx芯片时钟的问题。我正在审查另一位数字工程师的设计。有多个机箱,每个机箱都有自己的Xilinx芯片(XC9500)。一些Xilinx芯片正在与其他芯片进行交互。但是,每个

2019-01-09 10:41:26

。 在深思设计实现细节时,把这些通常用法记在心里,有助于理清时钟选择的思路。对于长期产品发展规划而言,在制定合适的时钟策略时,应考虑各个器件系列之间的兼容性。下面让我们深入了解一下这些时钟资源。 您可

2020-04-25 07:00:00

= PERIOD "clk" 20 ns HIGH 50%;2.通过 CLOCKwizard IP输出的时钟,就是全局时钟吗?假设我把问题1的时钟当作输入时钟,请问

2017-08-03 09:54:26

嗨,在post place and route genererated .vhd文件中有一个组件实例化X_FF。我已经搜索到了描述X_FF的等效xilinx原语(触发器),但发现了很多。我想xilinx原始X_FF描述IN VIRTEX 7 BO ??谢谢Manasa Thoonoli

2020-04-06 17:34:42

嗨,我是FPGA编程的新手。我在Xilinx ISE中使用VHDL进行设计。我的综合结果包括:FF,LUT,内存LUT,I / O,BRAM,DSP48,BUFG。我非常感谢能够帮助我解释每个资源

2020-03-24 10:14:15

亲爱的大家,Virtex中的许多原语在Spartan 6中找不到,例如BUFIO,BUFR,IDELAY,IDDR。如何使用Spartan原语实现类似的功能?非常感谢你!箱子以上来自于谷歌翻译以下

2019-06-03 10:31:21

大家好,我想从我的Zynq xc7z020clg400的一个结构时钟FCLKn获得一个2V5 LVDS时钟(P和N)。通过约束(pcb布局)的引脚P和N是球G19和G20。我已经检查了Xilinx库指南,但我找不到具有单端时钟输入和LVDS时钟输出的时钟原语。是否可以获得LVDS时钟输出?提前致谢!

2020-08-04 10:00:45

= VC1/N:15;VC3源:VC2;VC3除法器:100。的VC3作为timer8时钟;但为了使用UART模块,我必须得到19200的波特率,我必须设置全局资源如下:SYSCLK:24mhz;VC3来源

2019-03-21 15:39:43

嗨, 我想得到一些关于k7原语的详细信息(更具体的oserdes和iserdes)。我发现了一个关于v6 hdl原语的UG。 k7有类似的UG吗?我没找到它。谢谢。

2020-08-24 09:48:20

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2010-11-03 16:24:44 121

121 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的

2010-09-10 17:25:27 2175

2175 为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时

2011-01-04 11:26:35 1991

1991 sprintf函数详细解释.

2012-04-16 14:18:47 59

59 xilinx原语的使用,建议有一定经验的参考。

2016-12-17 11:58:56 13

13 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 谈到数字逻辑,谈到FPGA设计,每位工程师都离不开时钟。这里我们简单介绍一下xilinx 7 系列中的时钟资源。时钟设计的好坏,直接影响到布局布线时间、timing的收敛情况,FPGA的时钟

2017-02-08 05:33:31 561

561

时钟设施提供了一系列的低电容、低抖动的互联线,这些互联线非常适合于传输高频信号、最大量减小时钟抖动。这些连线资源可以和DCM、PLL等实现连接。 每一种Spartan-6芯片提供16个高速、低抖动的全局时钟资源用于优化性能。

2018-07-14 07:07:00 6504

6504

1. Xilinx 时钟资源 xilinx 时钟资源分为两种:全局时钟和第二全局时钟。 1. 全局时钟资源 Xilinx 全局时钟采用全铜工艺实现,并设计了专用时钟缓冲与驱动结构,可以到达芯片内部

2017-02-09 08:43:41 1315

1315 除了全局时钟缓冲器外,Spartan-6还包含驱动高速I/O时钟区域的时钟缓冲器。

2017-02-11 08:39:11 1198

1198

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-02-11 11:34:11 4223

4223 在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。

2017-02-11 11:46:19 876

876

IBUFGDS输入全局时钟及DCM分频使用

2017-02-11 16:16:11 4629

4629 xilinx 原语使用方法

2017-10-17 08:57:42 11

11 xilinx原语使用方法

2017-10-19 08:50:39 15

15 uboot移植详细解释

2017-10-26 10:08:08 28

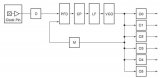

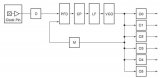

28 在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8891

8891

是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;第二类是长线资源,用以完成芯片Bank间的高速信号和第二全局时钟信号的布线;第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;第四类是分布式的布线资源,用于

2017-12-05 11:48:44 8

8 详细讲解了xilinx的时序约束实现方法和意义。包括:初级时钟,衍生时钟,异步时终域,多时终周期的讲解

2018-01-25 09:53:12 6

6 目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动

2018-03-26 11:43:57 11

11 Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。

2018-12-16 11:31:21 12305

12305

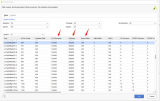

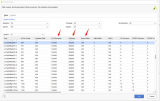

工程的时候选择器件的时候就可以看到这些资源的多少。如下图所示。 这里面的LUT资源是所有的LUT资源,包括SLICEL和SLICEM里面,如果大家想获得其中SLICEM的LUT资源多少,需要查看相关器件手册。

2019-09-15 12:21:00 4826

4826

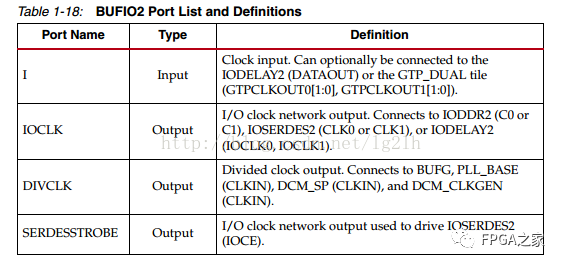

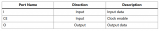

项目中主要用到的原语与IO端口有关,所以基本在Input/Output Functions 和IO两类中。下面着重介绍实际中所用到的几个原语,芯片A7系列。

2019-01-06 11:23:11 15706

15706

UltraRAM 原语(也称为 URAM)可在 Xilinx UltraScale +™ 架构中使用,而且可用来高效地实现大容量深存储器。

2019-07-13 11:08:09 6669

6669

区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 本文档的主要内容详细介绍的是FPGA的RAM存储资源详细资料说明包括了:1、 FPGA存储资源简介,2、 不同厂家的 Block RAM 布局,3、 块 RAM 和分布式 RAM 资源,4、 Xilinx Block RAM 架构及应用

2020-12-09 15:31:00 10

10 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 15

15 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

8 Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

2022-02-08 14:01:49 1092

1092

引言:本文我们介绍区域时钟资源。区域时钟网络是独立于全局时钟的时钟网络。不像全局时钟,一个区域时钟信号(BUFR)的跨度被限制在一个时钟区域,一个I/O时钟信号驱动一个单一的Bank。这些网络对于

2021-03-22 09:47:30 4631

4631

引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们

2021-03-22 10:09:58 11527

11527

引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 4353

4353

和前几代FPGA差异,总结7系列FPGA中的时钟连接。有关7系列FPGA时钟资源使用的详细信息,请关注后续文章。 时钟资源架构概述 7系列FPGA与前一代FPGA时钟资源差异 时钟资源连接概述 1.时钟资源架构概述 1.1 时钟资源概述 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管

2021-03-22 10:25:27 4326

4326 Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

2021-03-24 06:14:29 3

3 对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。只要可能就应尽量在设计项目中采用全局时钟。FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

2021-04-24 09:39:07 5827

5827

(29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:48 10

10 Xilinx SelectI IP是一个VHDL/Veilog封装文件,根据用户配置生成实例化的I/O逻辑,满足了输入SERDES、输出SERDES和延迟模块的应用要求。另外,它也可以例化生成所需的I/O时钟原语,将它连接到I/O引脚。

2022-06-06 09:46:43 1557

1557 HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

2022-06-13 10:07:26 1481

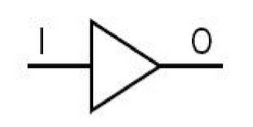

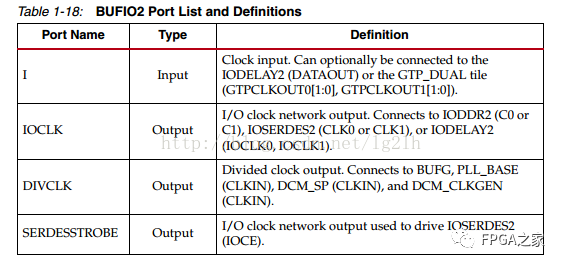

1481 BUFIO是用来驱动I/O列内的专用时钟网络,这个专用的时钟网络独立于全局时钟资源,适合采集源同步数据。BUFIO只能由位于同一时钟区域的Clock-Capable I/O驱动。一个时钟区域

2023-05-11 16:16:36 1530

1530

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

电子发烧友App

电子发烧友App

评论