本帖最后由 xie0517 于 2016-8-8 08:52 编辑

FIR是有限冲击响应;IIR是无限冲击响应。 FIR和IIR滤波器的一个主要区别:FIR是线性相位,IIR为非线性

2016-08-08 08:49:32

;FIR 滤波器的系统函数为多项式;FIR 滤波器具有线性相位。实现同样参数的滤波器,FIR比IIR需要的阶数高,因此计算量大。目前,FIR 数字滤波器的设计方法主要是建立在对理想滤波器频率特性做某种近似的基础上。设计方法有窗函数法,等波纹设计法(Equiripple)和最小二乘法 (Least

2021-08-17 06:19:17

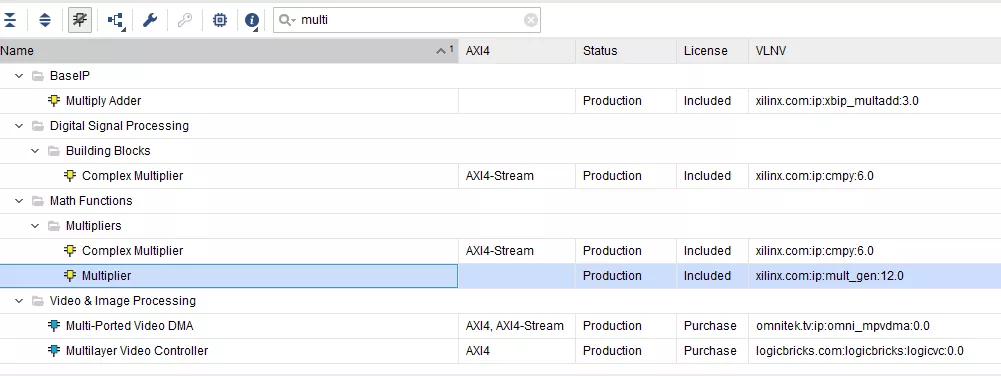

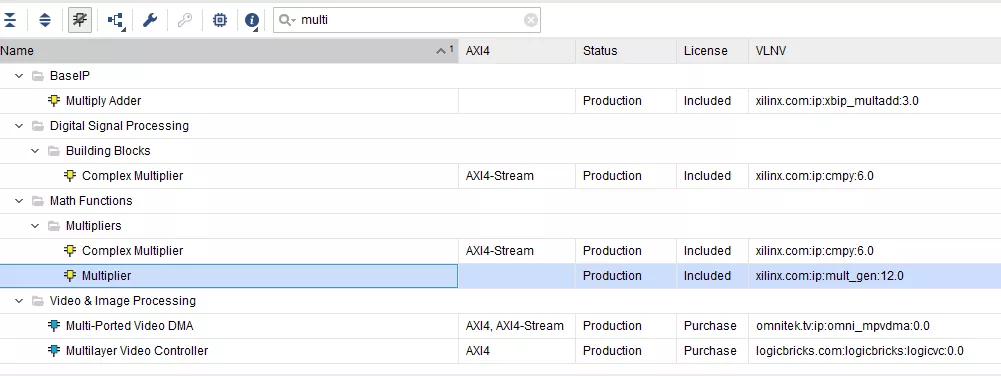

刚接触学习FPGA,懂得verilog HDL的基础语法,有一块带XILINX的ZYNQ xc7z020的开发板,开发软件用的是vivado;现在要设计一个16位的乘法器,功能已经实现。但需要考查

2018-02-25 16:03:46

的乘法器,功能已经实现。但需要考查性能指标:功耗、速度、吞吐量、覆盖率。但对这几个概念没有太大的了解①请问对于一个乘法器而言这几个方面指的是什么?②在Project Summary中有一个

2018-02-25 21:12:01

fpga中定点乘法器设计(中文)目录声明 ………………………………………………………………………………………… 10、 约定

2012-08-12 11:59:01

怎样做一个乘法器电路

2013-01-09 18:26:48

请问TI有没有类似AD835这样的乘法器??

2018-06-21 02:36:06

乘法器和混频器的区别 表面上看,都是做“乘法”了,其实区别很大。 乘法器,一般叫模拟乘法器,是用于

2009-11-13 16:37:25

请问关于乘法器的Verilog 程序中,移位累加具体每一步是怎么走的,自己琢磨了一番,感觉不是太懂,求高手解释。(明白二进制乘法的计算过程)

2015-10-17 23:08:02

主要任务:1.熟悉低通滤波器的原理及应用2.熟悉FPGA的硬件描述3.FPGA如何实现小数分频器4.用MATLAB对低通滤波器的验证预期成果或目标:FPGA对低通滤波器的Verilog(或VHDL

2013-04-04 22:16:11

Altera的FPGA内置的乘法器为何是18位的?

2023-10-18 07:01:41

信号 doutO29滤波器输出信号 dout_vldO1输出数据有效指示信号我们可以把工程划分成三个模块,分别是FIR滤波器模块和加法器模块和乘法器模块。1.FIR滤波器模块具有线性相位的半串行FIR

2017-08-02 17:35:24

3.3 累加运算3.3.1 累加原理3.3.2 顺序累加器3.3.3 滑动累加器3.4 乘法运算3.4.1 乘法原理3.4.2 基于移位相加的乘法器3.4.3 基于ROM的乘法器3.4.4 与固定

2012-04-24 09:33:23

问题:专用乘法器不适用于FPGA而是模拟工作正常。我试过的:在我的一个设计中,我使用10x10bit乘法器。原来我只是使用w6 = Vout * Vout。在模拟中,这似乎适用于我的设备利用率总结它

2019-05-29 06:12:17

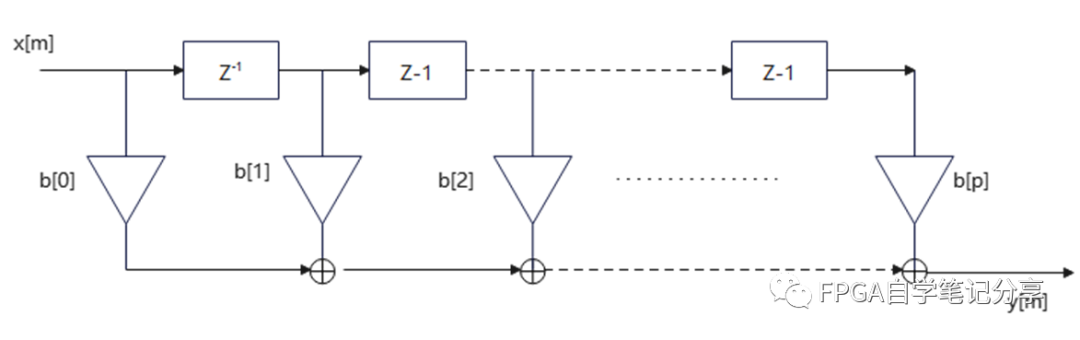

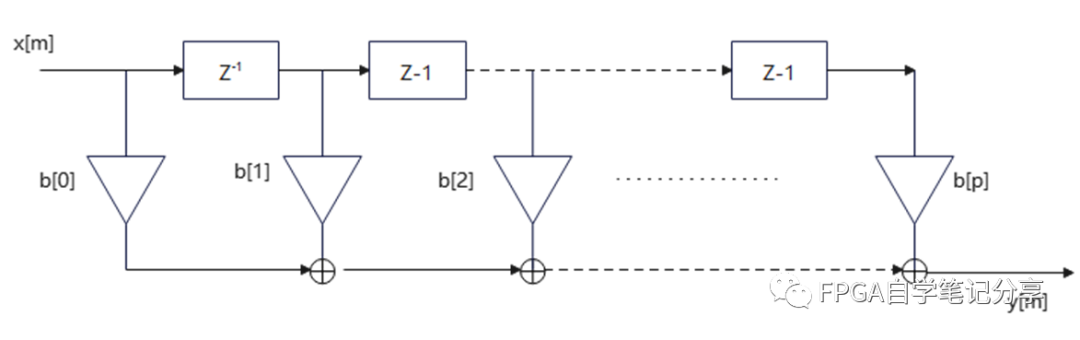

结构。本案例实现了具有线性相位的半串行结构的FIR滤波器。所谓串行结构,即串行实现滤波器的累加运算,将每级延时单元与相应系数的乘积结果进行累加后输出,因此整个滤波器实际上只需要一个乘法器运算单元。串行

2017-04-14 15:20:31

有关于乘法器的相关知识和代码。最近看到别人做乘法器, 自己也想试一试,上网找到特权同学的乘法器的视频讲解,但是对于我等初学者,还是搞不懂。经过一天的分析和整理,终于明白了,想分享给那些和我一样的菜鸟

2016-04-02 00:28:19

本帖最后由 eehome 于 2013-1-5 10:07 编辑

fpga中定点乘法器设计(中文)

2012-08-24 00:55:37

/devkits/HW-SPAR3A-SK-UNI-G.htm它有两个模拟输入和fpga,有20个乘法器但是我想要更多的输入和更多的乘法器块,是否能够满足这些功能的任何板?

2019-08-23 07:03:09

基于FPGA的FIR滤波器IP仿真实例 AT7_Xilinx开发板(USB3.0+LVDS)资料共享 腾讯链接:https://share.weiyun.com/5GQyKKc 百度网盘链接

2019-07-16 17:24:22

本帖最后由 eehome 于 2013-1-5 09:50 编辑

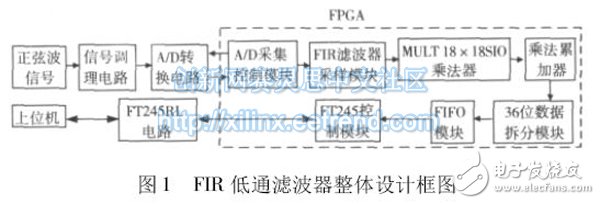

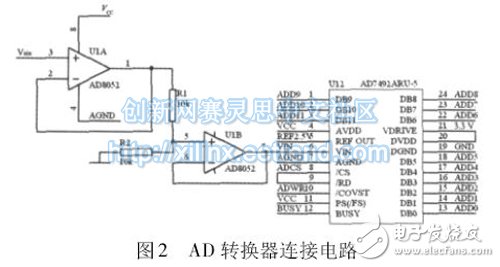

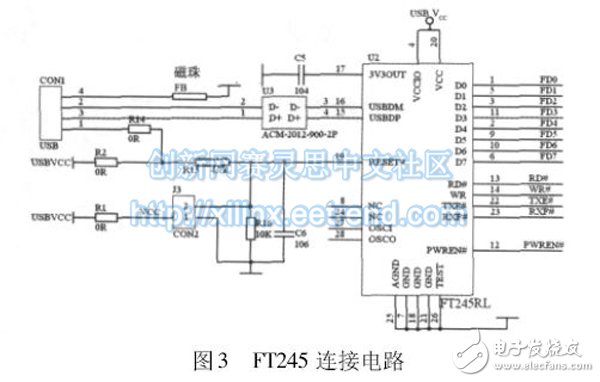

基于FPGA的FIR滤波器设计与实现 文章研究基于FPGA、采用分布式算法实现FIR滤波器的原理和方法,用

2012-08-11 15:32:34

基于FPGA的fir滤波器实现

2017-08-28 19:57:36

Programmable Gate Array,现场可编程门阵列)基于查找表的结构和全硬件并行执行的特性,如何用FPGA 来实现高速FIR 数字滤波器成了近年来数字信号处理领域研究的热点。目前,全球两大PLD 器件供应商都提供了加速FPGA 开发的IP(IntelligentProperty,知识产权)核。

2019-09-05 07:21:15

我正在研究一种适用于Vedic Maths算法的乘法器。我想对传统乘法器和vedic乘法器的时序延迟进行比较分析。我有spartan 3e和Xilinx 12.1时序分析器。请任何人都可以指导我

2019-07-04 06:36:45

相位,简单可扩展到多速率情况,以及充足的硬件支持除了其他原因之外。此示例展示了DSP System Toolbox™中用于设计具有各种特性的低通FIR滤波器的功能。内容获得低通FIR滤波器系数最小阶低通滤波器

2018-08-23 10:00:16

变频控制和乘法器的基本原理分别是什么?乘法器在变频控制中有什么作用?

2021-04-13 06:40:36

以LTE无线通信系统为例,提出了一种完整的降采样FIR滤波器的设计和硬件实现方案。该方案在利用FDAtool得到滤波器系数之后再进行定点化,并将各系数拆分成2的幂次方相加减的形式,以便进行移位

2021-04-14 06:56:15

阵列实现。FPGA进行实现时,依靠内嵌的DSP模块完成乘法器和加法器/累加器运算,为了节约FPGA的有限的DSP模块资源,设计面临的最大挑战是克服需要大量乘法器的弊端。如果将FIR抽取滤波器分解成

2009-10-23 10:26:53

大家好,如果这是错误的论坛,请道歉,如果有人指向正确的论坛,我将不胜感激。免责声明:我是VHDL的新手。我正在寻求为FIR滤波器实现无乘法器的乘法器。我想尽可能地做到一般,所以我不想硬编码我的组件

2019-04-19 07:02:48

型、频率取样型、格型四种。其中最适合FPGA实现的是直接型。“直接”是指直接由卷积公式得到:由上图可知,n阶FIR滤波器就需要n个乘法器。如果设计的是线性相位FIR,则h(n)是对称的,利用对称性可以

2020-09-25 17:44:38

并行流水结构FIR的原理是什么基于并行流水线结构的可重配FIR滤波器的FPGA实现

2021-04-29 06:30:54

目前FIR滤波器的硬件实现的方式有哪几种?怎么在FPGA上实现FIR滤波器的设计?

2021-05-07 06:03:13

在数字信号处理中,乘法器是整个硬件电路时序的关键路径。速度和面积的优化是乘法器设计过程的两个主要考虑因素。由于现代可编程逻辑芯片FPGA的集成度越来越高,及其相对于ASIC设计难度较低和产品设计

2019-09-03 07:16:34

模拟乘法器为何没输出信号我在仿真analog 的乘法器。我使用的是 Multisim 自带的库文件。器件用的 AD834。我画好设计图后,接上虚拟示波器。可是,信号发生器里有信号,乘法器后没有。请问各位高人,我哪里画错了。还是,multisim自带的库文件就不行

2022-04-01 16:48:04

什么是奈奎斯特定理?什么是模拟低通滤波器?什么是数字有限脉冲响应 (FIR) 滤波器?模拟低通滤波器和数字有限脉冲响应滤波器有何不同?

2021-07-29 07:27:13

说明:求fpga乘法器,要求快的,不是一个一个的加,而是像乘法竖式一样的,如:10111000111000 *1011111 =10111000111000*1011111

2012-08-16 14:08:36

最近在做乘法器,我想问下用VHDL做软乘法器,有点不懂软乘法器,求大神带!

2015-07-30 11:10:55

求浮点数乘除计算程序,求用硬件乘法器计算浮点数的程序

2015-11-03 22:32:47

硬件乘法器是怎么实现的

2023-09-22 06:53:57

乘法器大大提高 了 MSP430 单片机的数据处理能力,其支持的运算如下:硬件乘法器是外围设备,不是MSP430 CPU的一部分。这意味着,它的活动不会干扰CPU活动。乘法器寄存器是通过CPU指令加载和读取的外围寄存器。如果一个中断发生在写入OP1之后,而在写入OP2之前,使用乘法器对该中断进行..

2021-12-09 07:05:15

转dsp系列教程 本章节讲解FIR滤波器的低通,高通,带通和带阻滤波器的实现。 37.1 FIR滤波器介绍 37.2 Matlab工具箱生成C头文件 37.3 FIR低通滤波器设计 37.4 FIR

2016-09-29 08:32:34

AD9361的FIR滤波器是否可以配置成RRC滤波器?只能用作低通滤波器吗?另外,FIR滤波器的2/4倍插值是对原信号进行补0吗?

2019-01-07 11:31:53

过程首先根据所需要的功能,列出工程顶层的输入输出信号列表。 我们可以把工程划分成三个模块,分别是FIR滤波器模块和加法器模块和乘法器模块。1.FIR滤波器模块具有线性相位的半串行FIR滤波器结构图:在

2017-05-23 10:11:26

本文介绍了能高效实现固定常数乘法的分布式算法原理,给出了在FPGA 中用查找表实现FIR滤波器的算法设计,并以一个16 阶低通滤波器为例说明了设计过程。该设计通过Altera 公司的EP

2009-09-02 10:10:02 10

10 本文设计了适用于 SOC(System On Chip)的快速乘法器内核。通过增加一位符号位,可以支持24×24 无符号和有符号乘法。在乘法器的设计中,采用了改进的Booth 算法来减少部分积的数目

2009-09-21 10:40:42 20

20 基于FPGA对称型FIR滤波器的设计与实现:在基于FPGA的对称型FIR数字滤波器设计中,为了提高速度和运行效率,提出了使用线性I相位结构和加法树乘法器的方法,并利用Altera公I司的FPG

2009-09-25 15:38:38 30

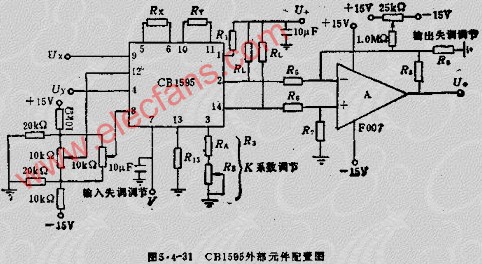

30 模拟乘法器AD834的原理与应用:AD834是美国ADI公司推出的宽频宽、四象限、高性能的模拟乘法器。它工作稳定,计算误差小,并具有低失真和微功耗的特点,本文介绍了AD834模拟乘法器

2009-09-29 10:49:21 183

183 应用分布式算法在FPGA平台实现FIR低通滤波器李明纬 黄世震(福州大学 福建省微电子集成电路重点实验室福州 350002)摘要:在利用FPGA实现数字信号处理方面,分布式算法发挥

2009-12-14 11:09:08 29

29 设计了一个基于FPGA的单精度浮点数乘法器.设计中采用改进的带偏移量的冗余Booth3算法和跳跃式Wallace树型结构,并提出对Wallace树产生的2个伪和采用部分相加的方式,提高了乘法器的运

2010-09-29 16:46:56 44

44 摘要: 针对在FPGA中实现FIR滤波器的关键--乘法运算的高效实现进行了研究,给了了将乘法化为查表的DA算法,并采用这一算法设计了FIR滤波器。通过FPGA仿零点验证

2009-06-20 14:09:36 677

677

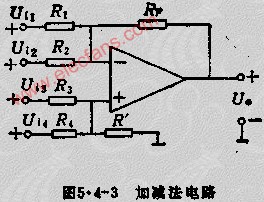

什么是数字滤波器

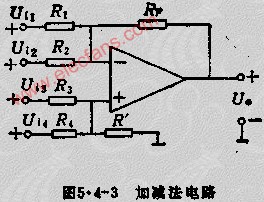

数字滤波器(digital filter)是由数字乘法器、加法器

2009-06-30 12:37:24 3698

3698

乘法器对数运算电路应用

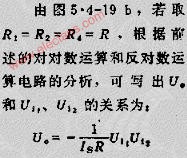

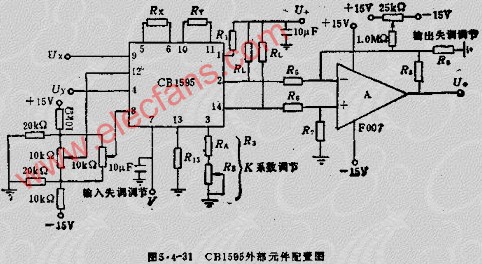

由对数电路实现乘法运算的数学原理是:UO=EXP(INU11+INU12)=U11+U12

图5.4-19示出了满足上式的乘法器的方框

2010-04-24 16:03:19 2273

2273

乘法器的基本概念

乘法器是一种完成两个互不相关的模拟信号相乘作用的电子器件。理想乘法器的输出特性方程可由下式表示:

UO

2010-05-18 14:03:59 13355

13355

1/4平方乘法器

这种乘法器是根据数学关系设计而成的,因此称为1/4平方乘法电路,或称1/4平方乘法器。其

2010-05-18 14:08:10 1777

1777

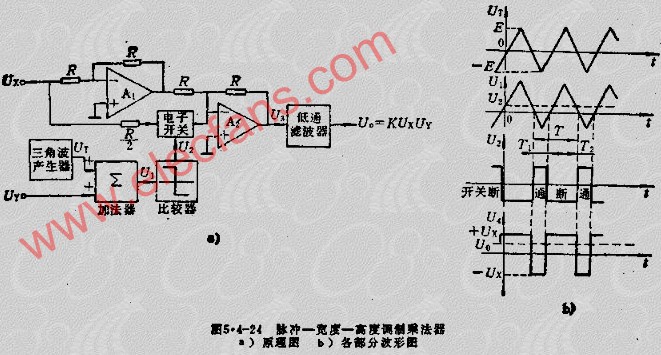

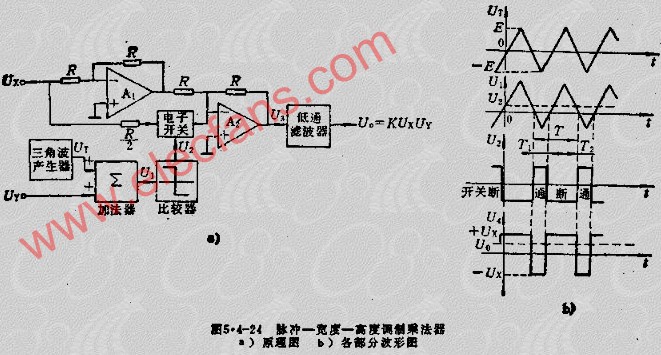

脉冲-宽度-高度调制乘法器

脉冲-宽度-高度调制乘法器双称为时间分割乘法器。这类乘法器电路原理图如图5.4-24A所示。图中,三角波电压UT和模拟输入电压UY

2010-05-18 14:23:53 1782

1782

变跨导乘法器的基本原理

图5.4-25为变跨导乘法器原理图。它利用V1、V2管的跨导GM正比于恒流源电流IO,而IO又受另一个输入电压控制,而实

2010-05-18 14:48:28 2947

2947

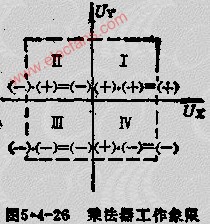

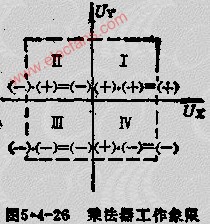

N象限变跨导乘法器

为了克服图5.4-25所示的乘法器的缺点,在基电路的基础上,采用了双重差分放大式结构,设计出如图5.4-27所示的N象限变跨导乘法器。

2010-05-18 15:24:08 1545

1545

可变跨导乘法器的品种

模拟乘法器就基单片结构的形式来说,基本上分为两大类,即用于处理交流小信号的如图5.4-27所示的基本电路,以及适用于模拟运算

2010-05-18 15:51:40 1736

1736

变跨导乘法器

这种乘法器现在已经成为一种工业上的标准方法,是应用极为广泛的优质乘法器。

2010-05-18 16:00:55 1087

1087 乘法器在模拟运算电路中的应用

相乘运算

2010-05-18 16:48:06 1879

1879 乘法器在通信电路中的应用

普通振幅调制

2010-05-18 17:46:47 1268

1268 实验目的 1、熟悉Xilinx的ISE 软件的使用和设计流程; 2、掌握Modelsim仿真软件的使用方法; 3、用乘法运算符实现一个16*16 乘法器模块; 4、用IP核实现一个16*16 乘法器模块; 5、用例化语

2011-05-20 17:00:14 66

66 充分利用有限冲击响应数字滤波器(Finite Impulse Response digital filter ,FIR)系数的对称特性,借助于MATLAB语言和现场可编程门阵列(FPGA)实现了一种高效的 低通滤波器 。设计过程中通过

2011-08-05 14:23:07 82

82 基于多速率信号处理原理,设计了用于下变频的CIC抽取滤波器,由于CIC滤波器结构只用到加法器和延迟器,没有乘法器,很适合用FPGA来实现,所以本文分析了CIC滤波器的原理,性能及影

2011-08-26 15:12:11 160

160 本文着重介绍了一种基于WALLACETREE优化算法的改进型乘法器架构。根据FPGA内部标准独特slice单元,有必要对WALLACE TREE部分单元加以研究优化,从而让在FPGA的乘法器设计中的关键路径时延

2011-11-17 10:50:18 4936

4936

设计了一种支持IEEE754浮点标准的32位高速流水线结构浮点乘法器。该乘法器采用新型的基4布思算法,改进的4:2压缩结构和部分积求和电路,完成Carry Save形式的部分积压缩,再由Carry Lo

2012-02-29 11:20:45 3269

3269 本文提出了一种高频四象限电流乘法器。该乘法器电路结构对称。提出的乘法器电路工作在±1.18 V的电源电压下。由于从输人端到地的低寄生电容,该电路可以工作在高频条件下,实验

2012-03-07 10:52:52 3516

3516

描述了基于FPGA的FIR滤波器设计。根据FIR的原理及严格线性相位滤波器具有偶对称的性质给出了FIR滤波器的4种结构,即直接乘加结构、乘法器复用结构、乘累加结构、DA算法。在本文中给

2012-11-09 17:32:37 121

121 基于FPGA的FIR滤波器设计与实现,下来看看

2016-05-10 11:49:02 38

38 8乘8乘法器verilog源代码,有需要的下来看看

2016-05-23 18:21:16 24

24 基于AD835的乘法器原理图及PCB设计

2016-06-08 16:46:10 0

0 华清远见FPGA代码-FPGA片上硬件乘法器的使用

2016-10-27 18:07:54 10

10 一个自己写的八位数的乘法器

2016-12-01 15:45:23 15

15 高速双域乘法器设计及其应用_郑朝霞

2017-01-07 18:39:17 0

0 模拟乘法器作用及电路

2017-10-23 09:22:40 28

28 乘法器,求模运算部分利用Barrett约减运算,用硬件描述语言进行FPGA设计与实现,避免了除法运算。对于192位的操作数,完成Barrett模乘需要约186个时钟周期,计算速率可以达到269.17 Mb/s。

2017-11-08 15:18:19 32

32 虽然许多有关调制的描述都将其描绘成一种乘法过程,但实际情况更为复杂。 首先,为清晰起见,若信号Acos(t)和未调制的载波cos(t)施加于理想乘法器的两路输入,则我们将得到一个调制器。这是因为两个

2017-11-15 14:45:18 15

15 分布式算法是一种适合FPGA设计的乘加运算,由于FPGA中硬件乘法器资源有限,直接应运乘法会消耗大量的资源。本文利用了丰富的存储器资源进行查找表运算,设计了一种基于分布式算法低通FIR滤波器;利用

2017-11-24 15:17:27 2942

2942 要的乘法器数量只有相同长度FIR滤波器的r约)一半,并且没有相位失真,因而线性相位FIR滤波器在无线通信,图像处理,语音处理等领域有非常广泛的应用。在设计线性相位FIR滤波器时,通常需要给出通带和阻带的区间以及相应误差范围r如通带起

2017-12-21 14:24:51 5

5 用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2018-04-28 11:50:00 1073

1073

实值数字有限脉冲响应(FIR)滤波器是许多数字信号处理(DSP)应用的基础。这些滤波器在TMS320C55xxE DSP家族中的高效实现需要专门的算法结构,其可以利用双片上硬件乘法器单元。该应用程序报告最适合于块FIR和单样本FIR滤波器的简单化还提供了示例汇编代码。

2018-05-04 14:31:45 5

5 MSP430硬件乘法器是一种外围设备,并不构成MSP430 CPU的一部分。它允许进行签名和无符号数的乘法运算。还支持乘法和累加(MAC)操作,这对于实现诸如有限脉冲响应(FIR)滤波器的数字信号处理(DSP)任务是有用的。

2018-05-07 09:38:18 8

8 硬件乘法器是现代计算机中必不可少的一部分,其基础是加法器结构。

2018-05-11 10:52:45 8533

8533 在做项目的过程中,经常遇到乘法计算,乘法器的设计就尤为重要。乘法器决定了最终电路功能能否实现,资源使用量多少以及时序性能优劣等。

2018-07-04 09:41:45 8885

8885 本文在设计实现乘法器时,采用了4-2和5-2混合压缩器对部分积进行压缩,减少了乘法器的延时和资源占 用率;经XilinxISE和QuartusII两种集成开发环境下的综合仿真测试

2018-12-19 13:30:25 10461

10461

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。

2019-11-28 07:06:00 3062

3062 用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2020-09-25 10:44:00 3

3 作者:猫叔 FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者

2020-09-27 15:12:52 8952

8952

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。乘法器不仅作为

2021-02-18 15:08:01 24395

24395

本设计以16位乘法器的设计为基础,从而掌握现代大规模集成数字逻辑电路的应用设计方法,进一步掌握电子仪器的正确使用方法,以及掌握利用计算机进行电子设计自动化(EDA)的基本方法。由16位加法器构成

2021-06-01 09:43:56 26

26 本文是本系列的第五篇,本文主要介绍FPGA常用运算模块-复数乘法器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:23:28 1204

1204

在数字信号处理中为了保证时延稳定性以及节省乘法器,通常使用对称系数的滤波器。

2023-06-02 12:35:18 742

742

电子发烧友App

电子发烧友App

评论