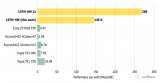

由于FPGA技术和ARM技术应用越来越广泛,通过设计并行总线接口来实现两者之间的数据交换,可以较容易地解决快速传输数据的需求,因此设计满足系统要求的FPGA并行总线显得尤为重要。本文设计的FPGA的ARM外部并行总线接口,满足了总线的时序要求,并在某航空机载雷达应答机中进行了应用.

2013-08-15 10:44:19 7204

7204

高速、高精度优势的同时也使得工程师避免了编写FPGA硬件代码的繁琐。科梁结合OPAL-RT先进的解算器和模型及科梁的工程经验,为客户提供从功能验证到系统测试电机模型和测试解决方案。

2017-08-09 10:52:21 2930

2930

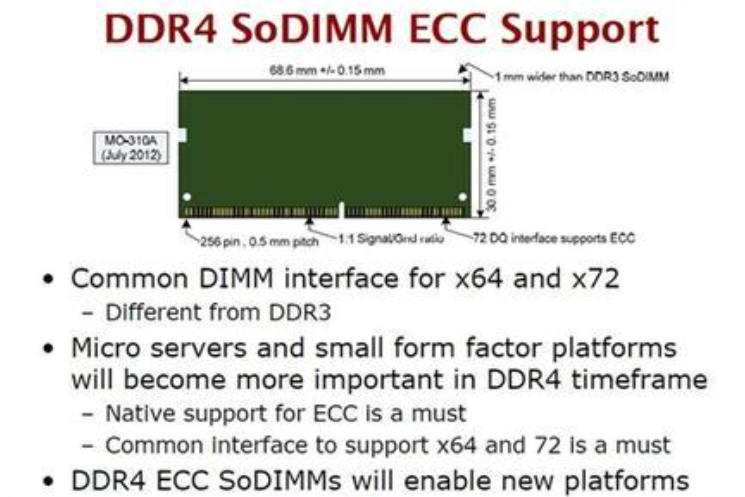

7 系列 FPGA 帧 ECC 逻辑可检查配置帧数据的单位或双位错误。它可使用基于帧数据( BitGen 生成)计算的 13 位汉明码校验值

2017-09-28 06:04:00 7316

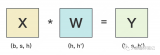

7316 图像处理算法在各种场景中都有广泛应用,借助于FPGA并行计算的优势可以将算法性能有效提升,但为了提升系统整体性能,仅仅提升某一部分的性能是不够的,一个好的方法是在FPGA内实现全部视频输入输出接口

2020-11-04 12:07:05 3073

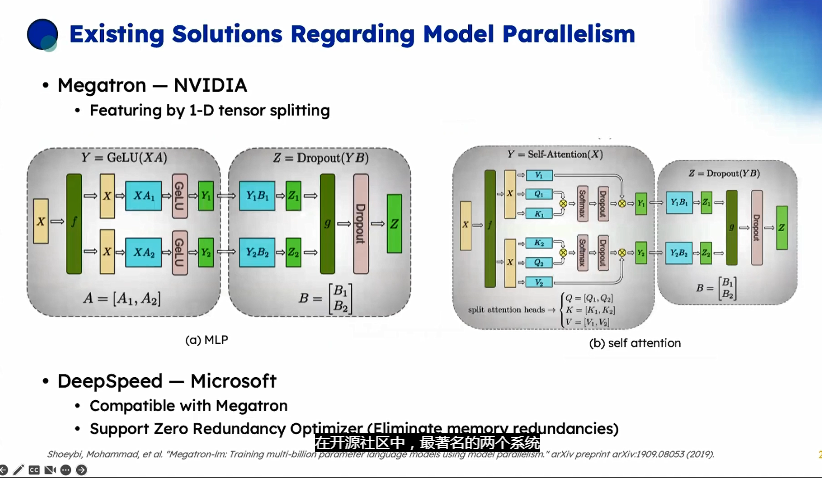

3073 在之前的内容中,我们已经介绍过流水线并行、数据并行(DP,DDP和ZeRO)。 今天我们将要介绍最重要,也是目前基于Transformer做大模型预训练最基本的并行范式:来自NVIDIA的张量模型

2023-05-31 14:38:23 1605

1605

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。

2024-02-22 16:15:03 1624

1624

在2410的NAND控制器里有硬件ECC模块,看2410的手册中是这么介绍的:ECC generator block executes the followings:1. When MCU

2019-05-20 02:32:08

嵌入式MCU存储器ECC工作原理注:摘自汽车电子 expert 成长之路公众号来简单聊一聊ECC,ECC 是“Error Correcting Code”的简写,中文名称是“错误检查和纠正”。ECC

2021-11-03 08:26:19

并行测试的实现途径分为软件方式和硬件方式。用软件方式实现并行测试,关键是对测试任务的分解和调度,但可能会产生竞争或者死锁现象。因此,在测试资源有限并且任务分解和调度算法不成熟的情况下,用软件实现并行

2019-08-16 06:50:47

不要花多大的心思。(3)硬件协议以下是PC上的DB25打印接口。其中的2到9引脚为8bit数据的传输通道。在EPP模式下,这个8bit通道是双向的。其他比较重要的引脚有。17 地址选通 PC到FPGA

2019-08-06 05:00:00

最佳情况的电源系统是有好处的,因为在许多方面仍有太多的不确定性,比如在硬件设计完成和功耗可以测量之前,静态小电流状态与全速工作状态之间的动态负载要求将如何波动。 采用并行工程(CE)技术,可以为在项目

2018-10-08 15:17:52

FPGA的并行多通道激励信号产生模块FPGA的并行多通道激励信号产生模块.docx

2012-08-11 10:35:50

输出。这两个芯片的管脚虽然很多,但大多数都是与硬件设计有关。其实几乎所有的并行ADC和并行DAC与FPGA之间的接口只有一条时钟线与一组数据总线,数据总线的位宽即为ADC/DAC的位数。每个时钟周期

2020-09-27 09:40:08

`fpga基础篇(二):三大并行结构最近小编比较忙,所以这期给大家介绍一个基础篇,比较简单,但却是FPGA编程的基础。我们知道FPGA与单片机最大的区别就是FPGA是并行执行的,而单片机是串行的,说

2017-04-13 10:23:27

并行编程模型是并行计算,尤其是并行软件的基础,也是并行硬件系统的导向,在面临多核新挑战的情况下,什么样的并行编程模型在未来能成为主流,还很难说。至少到目前,还处于百家争鸣的时代,很多模型提出,很多在应用,下面我们简单介绍一下当前的并行编程模型现状。

2019-07-11 08:03:33

本帖最后由 zyplabview 于 2015-5-23 17:52 编辑

模型二硬件仿真

2015-05-23 17:51:30

本文档介绍了 STM32H7 系列微控制器上纠错码(ECC)的管理和实现。本应用笔记针对保护内部存储器内容的 ECC 机制,描述了与之相关的硬件、软件信息。除此之外,也可使用外部存储器进行 ECC

2023-09-08 07:31:20

安路 EG4X FPGA 器件支持多种程序加载模式。本手册主要介绍从动并行(SP)加载模式以及从动并行级联加载模式的使用。内容包括使用从动并行加载模式的软件配置,使用从动并行加载模式和从动并行级联加载模式的硬件电路连接,另外包括 MCU 作为控制 FPGA 从动并行加载的主控器件时的软件工作流程。

2022-10-27 07:31:16

《无线通信FPGA设计》分布式FIR的并行改写,结果与matlab仿真结果基本吻合

2017-02-26 09:09:47

并行计算。在进行FFT 这类并行运算为主的算法时,采用FPGA的优势不言而喻。用FPGA实现FFT算法进行谐波检测成为了一大热点。 以往FPGA的设计主要依靠硬件描述语言来完成。Xilinx公司推出了专门

2019-06-21 06:25:23

多核体系结构的硬件仿真平台FPGA资源消耗随计算核数目成线性增加。这里提出的对称多核体系结构FPGA仿真模型,解耦合计算核数目与系统硬件开销的线性关系,其核心设计思想是:在构建仿真系统时,使用一个与目标系统中单个计算

2019-08-23 07:06:56

等串行总线接口只能实现FPGA 和ARM 之间的低速通信 ;当传输的数据量较大.要求高速传输时,就需要用并行总线来进行两者之间的高速数据传输.

2019-09-17 06:21:10

的。多核控制器可以很好地满足这种需求,然而对于最终的并行处理而言,它的性能很难超过FPGA。FPGA为自动化测试系统提供了无与伦比的性能和可靠性,是目前并行化编程计算硬件中的佼佼者。LabVIEW

2014-12-12 16:02:30

ARM周期模型工具提供了一个集成环境,该环境将系统验证与硬件开发流程并行。

周期模型编译器采用RTL硬件模型并创建一个高性能的可链接对象,称为周期模型,它是周期和寄存器准确的。

周期模型编译器提供了与验证环境交互的API:

2023-08-16 06:30:07

ARM周期模型工具提供了一个集成环境,该环境将系统验证与硬件开发流程并行,如图1.1所示。

周期模型编译器采用RTL硬件模型并创建一个高性能的可链接对象,称为周期模型,即准确的周期和寄存器。

周期模型提供了与验证环境交互的API。

2023-08-12 06:46:25

并行测试的实现途径分为软件方式和硬件方式。用软件方式实现并行测试,关键是对测试任务的分解和调度,但可能会产生竞争或者死锁现象。因此,在测试资源有限并且任务分解和调度算法不成熟的情况下,用软件实现并行测试会很困难。那么,为什么说对多通道并行激励信号的需求也是影响并行测试的关键因素呢?

2019-08-13 08:08:41

)、离散余弦变换(DCT)、小波变换、数字滤波器(有限脉冲响应(FIR)、无限脉冲响应(IIR)和自适应滤波器)以及数字上下变频器。这些算法中,每一种都有一些结构性的元件可以用并行方法实现。而FPGA

2021-12-15 06:30:00

DSP芯片组成并行处理系统。另外,为充分发挥 DSP芯片在复杂算法处理上的优势及FPGA在大数据量的底层算法上的优势,设计了一种基于FPGA控制的多DSP并行处理系统。1 系统设计基于FPGA控制的多

2019-05-21 05:00:19

我正在设计一个子板,上面有40个Artix 7(AC7A12T)设备。每台设备都应具有相同的图像。我不是一次编程链1中的每个器件的串行链,而是希望并行执行任务,以便所有FPGA同时进行编程。我似乎

2020-05-14 07:01:03

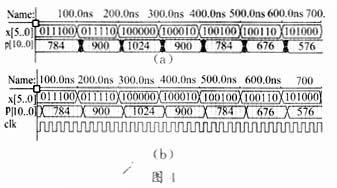

是人工智能大跃进的基础,在线下模型训练中Xeon-Phi、GPU等发挥着巨大的作用,而在线上的推理任务中,浪潮FPGA深度学习加速解决方案则能够实现7倍以上的能效比提升。 卷积网络之父、Facebook

2021-09-17 17:08:32

本文介绍一种使用硬件描述语言VHDL来实现基于Petri网的并行控制器的方法。首先使用Petri网对问题进行建模,并对模型进行分析和控制,获得控制器的Petri网模型;然后用VHDL对Petri网

2019-08-16 07:52:03

本文以并行多通道信号产生模型为依据,设计并实现了以FPGA为核心器件的并行多通道信号产生模块,主要包括FPGA系统设计和多通道波形产生模块设计。通过模块测试后发现,该模块具备产生高质量并行多通道激励信号的能力。

2021-04-29 06:17:38

本帖最后由 人间烟火123 于 2018-6-15 10:30 编辑

现在想把DM365的ECC由原来的软件ECC校验改为硬件校验,在TI提供的内核和u-boot中如何改?在

2018-06-15 03:28:38

如何利用单片机AT89C52对FLEX10K系列FPGA中的EPF10K10进行在线并行配置?

2021-04-29 06:19:03

各位前辈,小弟现在刚开始学习ARM,想用ARM与FPGA并行总线通信。实验过程是这样的,我现在FPGA内部建立了一个双口RAM,现在想通过ARM并行总线读写RAM,下面的是FPGA中RAM与ARM

2022-11-22 14:53:52

Mali T604 GPU的结构是由哪些部分组成的?Mali T604 GPU的编程特性有哪些?Mali GPU的并行化计算模型是怎样构建的?基于Mali-T604 GPU的快速浮点矩阵乘法并行化该如何去实现?

2021-04-19 08:06:26

本帖最后由 一只耳朵怪 于 2018-6-12 11:56 编辑

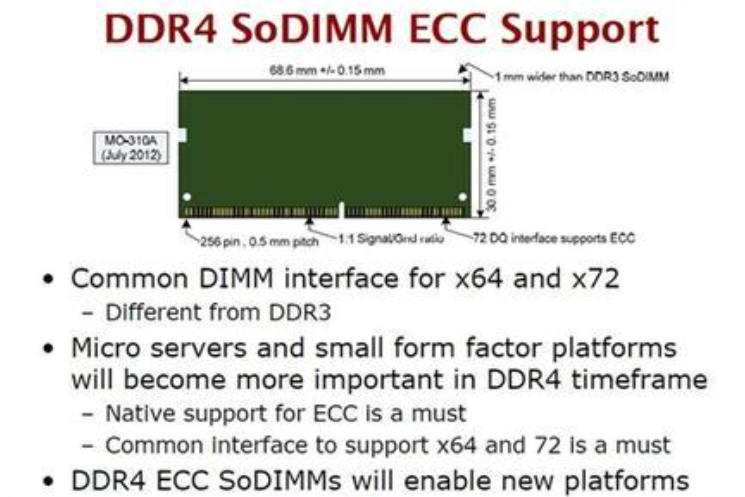

ECC校验是一种内存纠错原理,它是现在比较先进的内存错误检查和更正的手段。ECC内存即纠错内存,简单的说,其具有发现错误

2018-06-12 10:06:41

proteus中有仿真模型的并行插口怎么绘制?

2019-04-23 20:14:43

上EasyGo FPGA Solver中的FPGA Coder解算软件,可以将用户灵活搭建的模型直接下载至FPGA中运行,而不需要进行FPGA的编译,最

2022-05-19 09:16:05

概述EasyGo FPGA Solver是EasyGo开发的专门部署在FPGA 硬件上的解算器软件。根据不同的应用需求,会有不同的FPGA Solver 选择

2022-05-19 09:21:43

针对多线寻址驱动方案,以驱动算法的数学理论为基础,建立了可由EDA工具综合的硬件驱动算法模型。该算法模型综合了FRC-PWM灰度技术的解决方案,通过FPGA验证:实现了在保证CST

2009-02-28 16:52:58 38

38 采用软硬件结合的方法,给出一种基于VLIW 的并行可配置椭圆曲线密码体制(ECC)专用指令协处理器架构。该协处理器采用点加、倍点并行调度算法,功能单元微结构采

2009-03-20 16:14:02 25

25 提出一种适用于SMP 集群的混合MPI+OpenMP 并行编程模型。该模型贴近于SMP 集群的体系结构且综合了消息传递和共享内存2 种编程模型的优势,能获得较好的性能。讨论该混合模型的实

2009-03-30 09:28:40 32

32 ECC 数字签名算法是目前的研究热点之一。本文根据ECC 数字签名算法的相关理论,使用Verilog 语言实现了其完整方案,并给予相应的优化。给出了关键部分的仿真结果。

2009-09-12 15:39:31 16

16 算法隐含并行性的物理模型:利用物理学原理对算法的隐含并行性进行了分析,提出算法的不确定性和高熵态是隐含并行性出现的根源,但算法的隐含并行性会导致算法结果的不确定

2009-10-21 08:23:07 10

10 椭圆曲线密码体制(Elliptic Curve Cryptosystem,ECC)是目前已知的所有公钥密码体制中能提供最高比特强度(strength-per-bit)的一种公钥加密体制。研究椭圆曲线密码算法的芯片设计有较大

2010-08-06 15:50:36 20

20 介绍了一种二进制补码快速并行平方器的设计方法,并给出了一个6位二进制补码平方器的例子及在MAX+PLUS II 10.0环境下的仿真结果。

关键词:FPGA,二进制补码,平方器

2009-05-17 12:59:26 2549

2549

什么是内存ECC校验

2009-12-25 14:28:00 1979

1979 什么是ECC内存

ECC是“Error Checking and Correcting”的简写,中文名称是“错误检查和纠正”。ECC是一种能够实现“错误检查和纠正”的技术,ECC内存就是应用了这种技术的

2010-01-12 15:42:34 771

771 并行测试的实现途径分为软件方式和硬件方式。用软件方式实现并行测试,关键是对测试任务的分解和调度,但可能会产生竞争或者死锁现象。因此,在测试资源有限并且任务分解和调度算法不成熟的情况下,用软件实现并行测试会很困难。用硬件方式实现并行测试时,需

2011-01-21 00:17:44 1106

1106

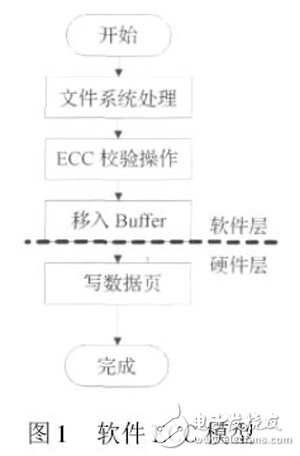

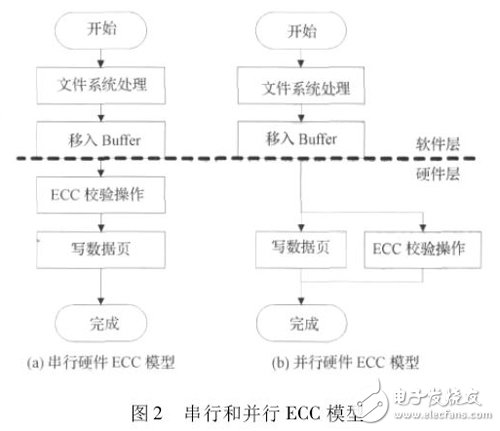

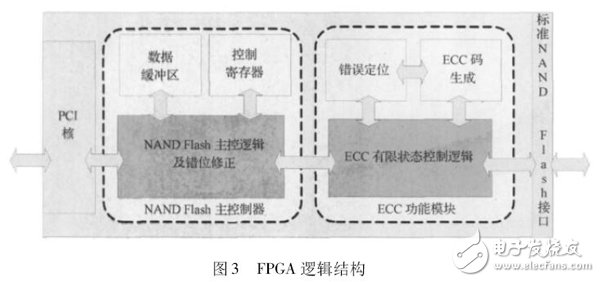

本文将ECC校验算法通过硬件编程语言VHDL在AheraQuanusⅡ7.0开发环境下进行了后仿真测试,实现了NANDFlash的ECC校验功能。本程序可实现每256Byte数据生成3ByteECC校验数据,且通过与原始ECC数据

2011-07-17 10:55:20 5763

5763

根据某移动公司本地传输现网的结构特点以及ECC 管理的现状,对 ECC 子网的优化配置方法进行详细规范。建立本地传输网ECC 子网划分的模型,对本地传输网的ECC 配置方法进行阐述。

2011-08-02 16:54:07 20

20 本文介绍的基于PCI总线的FPGA计算平台的系统实现:通过在PC机上插入扩展PCI卡,对算法进行针对并行运算的设计,提升普通PC机对大计算量数字信号的处理速度。本设计采用5片FPGA芯片及

2011-08-21 18:05:31 1970

1970

对FPGA技术来说,早期研发在5年前就已开始尝试采用多核和硬件协处理加速技术朝系统并行化方向发展。在实际设计中,FPGA已经成为CPU的硬件协加速器,很多芯片厂商采用了硬核或软核CPU+FPGA的

2011-09-23 15:30:06 770

770 针对复杂算法中矩阵运算量大, 计算复杂, 耗时多, 制约算法在线计算性能的问题, 从硬件实现角度, 研究基于FPGA/Nios-Ⅱ的矩阵运算硬件加速器设计, 实现矩阵并行计算。首先根据矩阵运算

2011-12-06 17:30:41 89

89 通过 labview fpga定制硬件。

2016-05-17 17:47:59 24

24 基于FPGA的嵌入式多核处理器及SUSAN算法并行化

2016-08-30 18:11:47 24

24 基于FPGA的ECC快速算法研究及设计_陈俊杰

2017-01-07 19:08:43 2

2 基于FPGA的ARM并行总线研究与仿真

2017-01-24 16:54:24 19

19 一种基于门限ECC的PKI_CA模型的设计_毛颖慧

2017-03-19 11:46:13 0

0 本文介绍了FPGA电源设计并行工程的合理性,讲解了并行工程(CE)技术及其作用,讨论了FPGA电源系统设计的复杂性和不确定性。

2017-10-13 13:00:35 5

5 基于FPGA和多DSP的多总线并行处理器设计

2017-10-19 13:40:31 4

4 AES和ECC的混合加密系统的设计

2017-10-31 09:04:25 11

11 7 系列 FPGA 帧 ECC 逻辑可检查配置帧数据的单位或双位错误。它可使用基于帧数据( BitGen 生成)计算的 13 位汉明码校验值。 在读回过程中,帧 ECC 逻辑可计算使用所有帧位(包括

2017-11-15 12:25:01 1877

1877 限的并行性。针对这个问题,普渡大学的研究人员提出了一种LSTM在Zynq 7020 FPGA的硬件实现方案,该方案在FPGA中实现了2层128个隐藏单元的RNN,并且使用字符级语言模型进行了测试。该实现比嵌入在Zynq 7020 FPGA上的ARM Cortex-A9 CPU快了21倍。

2017-11-15 13:30:06 1974

1974

基于串行异步收发器(UART)的通信中经常用到循环冗余校验(CRC),常见的CRC校验电路多为串行校验,校验所需时钟周期较多,基于查找表或输入矩阵转换的并行算法,需要存储余数表,占用大量的硬件资源

2017-11-18 11:24:54 1789

1789

了一种可用于模型参数求解的并行迭代模型MRI。MRI模型在保持Map以及Reduce阶段的基础上,新增了Iterate阶段以及相关通信协议,实现了迭代过程中模型参数的更新、分发与迭代控制;通过对MapReduce状态机进行增强,实现了节点任务的重用,避免了迭代过程中节点任务

2017-11-23 15:04:35 1

1 重复计算稀疏矩阵向量乘,提出了新的并行计算结构。实验分析表明,提出的架构提高了Wiedemannn算法中稀疏矩阵向量乘的并行性,同时充分利用了FPGA的片内存储器和吉比特收发器,与目前性能最好的部分可重构计算PR模型相比,实现了2.65倍的加速性能。

2017-11-27 10:45:14 0

0 针对并行软件的状态空间规模大导致测试难度大的问题,提出一种基于着色Petri网(CPN)的针对待测行为的并行模型化简方法。首先,将原模型根据模型中出现的并发变迁、同步变迁、分叉库所、汇合库所等特殊

2017-12-03 10:14:26 0

0 两个显著问题:(1)如何让软件设计充分发掘硬件的并行处理能力,从而提高系统的性能;(2)在系统硬件规模不断扩大、复杂度越来越高的情况下,如何保证系统的可靠性. 任务并行程序设计模型已成为并行程序设计的主流,其通

2018-01-12 09:35:01 0

0 针对嵌入式系统所处理任务日益复杂,难以满足安全关键任务的执行时间需求问题,提出了一种高性能嵌入式并行处理模型(-IPEPPM)。模型可分为3层。底层传输层通过使用SRI0 9erialrapid

2018-02-12 17:21:36 0

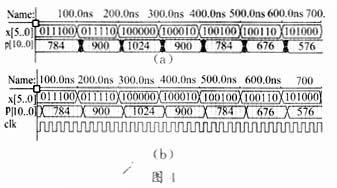

0 根据课题要求,设计FPGA部分硬件电路如图1所示。FPGA芯片选用Altera公司的中档器件FLEX-EPF10K10LC84-4,他是基于SRAM LUT结构的FPGA器件。根据传送数据的方式

2019-08-21 08:01:00 4908

4908

作为集成电路设计领域现场可编程门阵列 (FPGA) 技术的创造者之一,赛灵思一直积极推广高层次综合 (HLS) 技术,通过这种能够解读所需行为的自动化设计流程打造出可实现此类行为的硬件。赛灵思刚刚推出了一本专著,清晰介绍了如何使用 HLS 技术来创建优化的硬件设计。

2018-11-10 11:01:05 2750

2750 等串行总线接口只能实现FPGA 和ARM 之间的低速通信 ;当传输的数据量较大.要求高速传输时,就需要用并行总线来进行两者之间的高速数据传输.

2019-08-08 15:37:50 5863

5863

ECC的英文全称是“ Error Checking and Correcting”(错误检查和纠正),从这个名称就可以看出它的主要功能就是“发现并纠正错误”。

2020-03-22 13:39:00 48999

48999 本文档的主要内容详细介绍的是FPGA的硬件基础教程免费下载包括了:1、 FPGA 的发展历史,2、 FPGA 的结构,3、 FPGA 芯片选型

2020-12-09 13:47:50 38

38 出了四核心嵌入式并行处理器FPEP的结构设计并建立了FPGA验证平台.为了对多核处理器平台性能进行评测,提出了基于OpenMP的3种可行的图像处理领域的经典算法SUSAN算法的并行化方法:直接并行

2021-02-03 16:26:00 8

8 用软件实现 CRC 校验码计算很难满足高速数据通信的要求 ,基于硬件的实现方法中 ,有串行经典算法 LFSR 电路 以及由软件算法推导出来的其它各种并行计算方法。以经典的LFSR 电路为基础 ,研究

2021-03-28 09:34:24 30

30 提出了一种基于FPGA实现的全并行结构FFT设计方法,采用XILINX公司最新器件VirtexII Pro,用硬件描述语言VHDL和图形输入相结合的方法,在ISE6.1中完成设计的输入、综合、编译

2021-03-31 15:22:00 11

11 /ASCⅠ和¢PU/FPGA等简述了异构混合并行编程模型随着各类异构混合结构的发展而做岀的改变,异构混合并行编程模型可以是对现有的一种语言进行改造和重新实现,或者是现有异构编程语言的扩展,或者是使用指导性语句异构编程,或者是容器模式协同

2021-05-13 10:30:35 13

13 为 K9F2G08 。特点: 系统配合 FatFs 实现了坏块管理,硬件ECC,软件 ECC 纠错2、代码分析2.1、擦写均衡分析 在create_chain 函数中实现,每次分配都由当前scl 指向的 free cluster 开始,逐块检查,是否有可用 cluster 存在。如果没...

2021-11-20 12:51:03 21

21 ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA驱动并行ADC和并行DAC芯片。

2022-04-21 08:55:22 5774

5774 定义 ECC校验是一种内存纠错原理,它是比较先进的内存错误检查和更正的手段。ECC内存即纠错内存,简单的说,其具有发现错误,纠正错误的功能,一般多应用在高档台式电脑/服务器及图形工作站上,这将使整个

2022-06-18 20:08:01 9898

9898

电子发烧友网站提供《安路EG4X FPGA从动并行加载模式.pdf》资料免费下载

2022-09-27 10:44:27 1

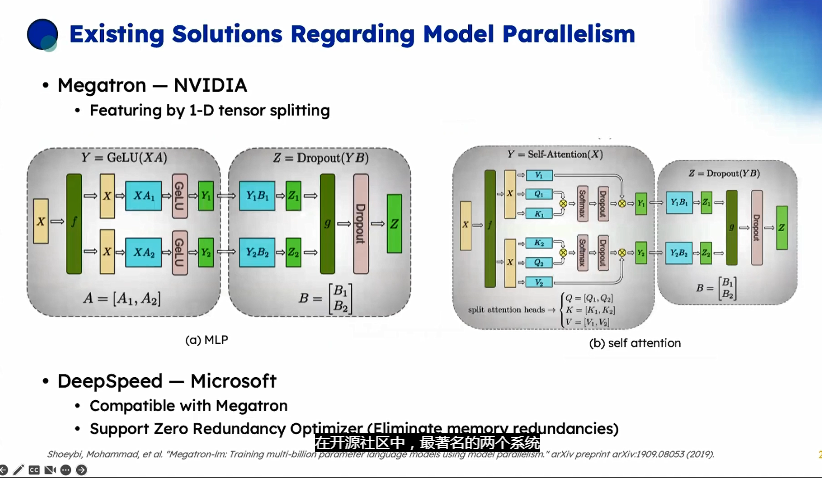

1 张星并行和流水线并行技术通常被描述为模型并行,在开源社区中,最著名的两个系统是NVIDIA的Megatron- M和Microsoft的DeepSpeed。

2023-03-23 17:21:29 1395

1395

本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

2023-05-24 10:57:36 653

653

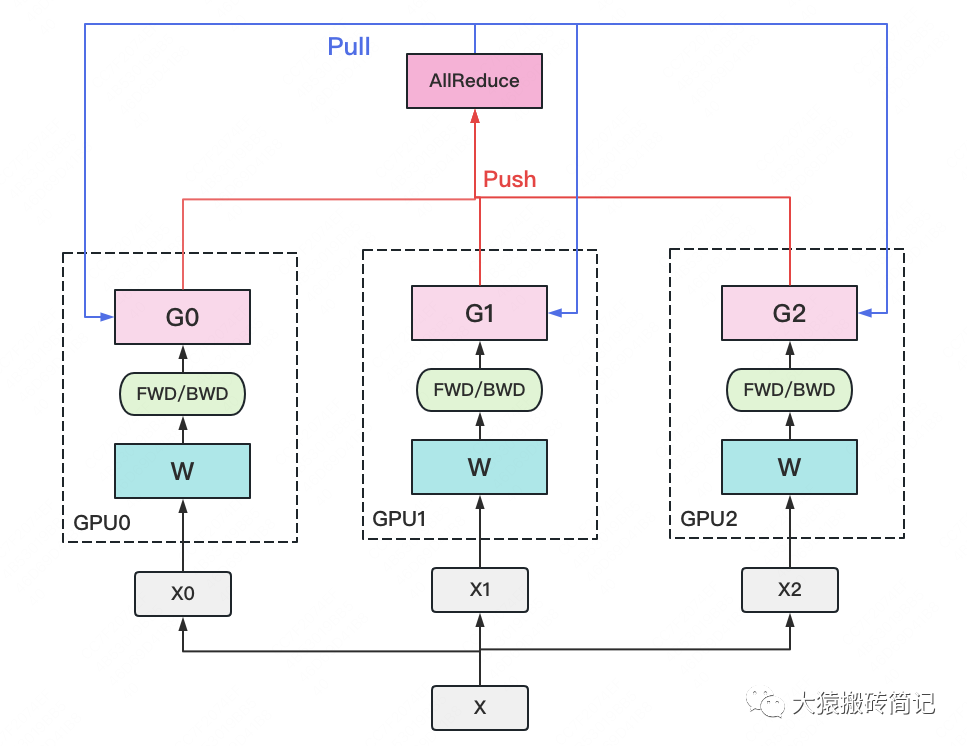

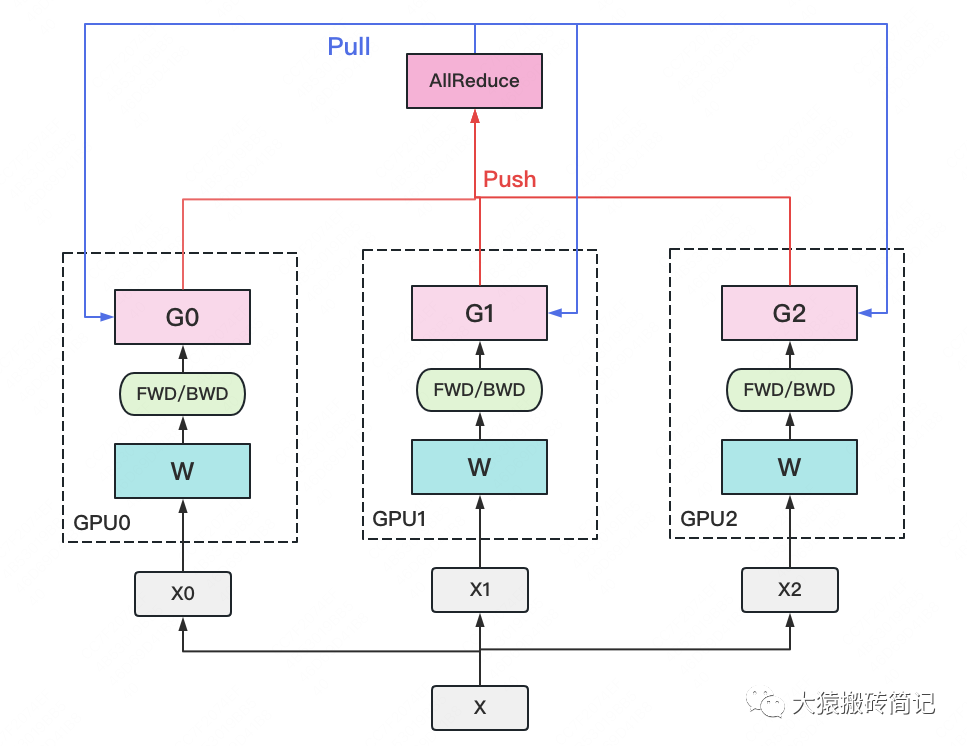

数据并行的核心思想是:在各个GPU上都拷贝一份完整模型,各自吃一份数据,算一份梯度,最后对梯度进行累加来更新整体模型。理念不复杂,但到了大模型场景,巨大的存储和GPU间的通讯量,就是系统设计要考虑的重点了。在本文中,我们将递进介绍三种主流数据并行的实现方式:

2023-06-16 09:54:36 1804

1804

数据并行是最常见的并行形式,因为它很简单。在数据并行训练中,数据集被分割成几个碎片,每个碎片被分配到一个设备上。这相当于沿批次(Batch)维度对训练过程进行并行化。每个设备将持有一个完整的模型副本,并在分配的数据集碎片上进行训练。

2023-08-24 15:17:28 537

537

电子发烧友网站提供《无与伦比的并行处理—FPGA加速的根本基石.pdf》资料免费下载

2023-09-15 14:57:19 0

0 电子发烧友网站提供《基于FPGA的ARM并行总线设计原理.pdf》资料免费下载

2023-10-10 09:31:31 0

0 NVIDIA Megatron 是一个基于 PyTorch 的分布式训练框架,用来训练超大Transformer语言模型,其通过综合应用了数据并行,Tensor并行和Pipeline并行来复现 GPT3,值得我们深入分析其背后机理。

2023-10-23 11:01:33 826

826

电子发烧友App

电子发烧友App

评论