作者:Mculover666 1.实验目的 通过例程探索Vivado HLS设计流 用图形用户界面和TCL脚本两种方式创建Vivado HLS项目 用各种HLS指令综合接口 优化Vivado HLS

2020-12-21 16:27:21 3153

3153 当我们安装好Vivado 的时候,也同时装好了Vivado HLS.。 这是个什么东西?我就有一种想一探究的感觉。网上一查,Vivado High-Level Synthesis。学习了一段时间

2020-10-14 15:17:19 2881

2881

,才能为既定的应用程序或程序集进行有效地HLS引擎做正确的决策。挑战为了探索解决方案空间,我们必须根据给定的配置合成所得到的电路进行全方位的尝试。使用现在的HLS工具,每种特定配置可能需要几分钟到半小时

2021-07-10 08:00:00

你好我有两个用VHDL编写的RTL处理器完全相同。第一个是三个管道阶段,它按如下划分:IF => ID => EX-WB(表示instr获取解码执行和写回)第二个是四个流水线级,按如下

2020-05-22 09:24:50

你好,在Vivado 2016.4中运行Synthesis功能时,我收到了有效的许可证错误[Common 17-345]。请参阅附件和帮助。谢谢,Gursimar合成日志file.txt 2 KB

2019-01-04 11:22:27

库函数,测试激励读入图像,经过滤波器处理输出的图像保存分析。可以看到,算法的处理基于IPIimage类型,输入和输出图像都使用此类型。2.3.2 使用IO函数和Vivado HLS视频库替换

2021-07-08 08:30:00

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用加入赛灵思免费在线研讨会,了解如何在Zynq®-7000 All Programmable

2013-12-30 16:09:34

我在Vivado HLS中有以下错误的合成。我试图更新许可证文件但没有成功。请给我一个建议。@E [HLS-72]许可证签出不成功。确保可以访问许可证或通过环境变量指定适当的许可证。 执行

2020-05-20 09:13:21

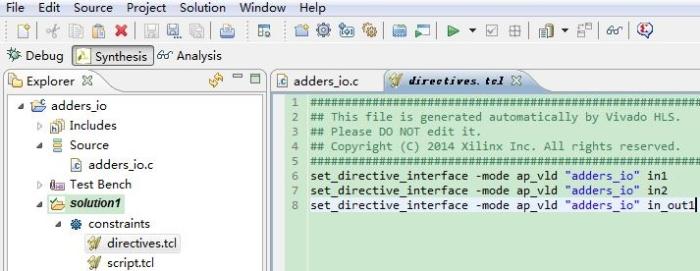

1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-11 07:09:49

本帖最后由 FindSpace博客 于 2017-4-19 16:57 编辑

在c simulation时,如果使用gcc编译器报错:/home/find/d/fpga/Vivado_HLS

2017-04-19 16:56:06

vivado可以正常使用,但是HLS总是出现图片中的错误。请问该如何解决?谢谢!

2020-08-12 01:36:19

你好!如果我想使用vivado hls来合成具有axi流接口的代码,是否有必须遵循的标准编码风格?

2020-04-21 10:23:47

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:40:28

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:39:13

,才能为既定的应用程序或程序集进行有效地HLS引擎做正确的决策。挑战为了探索解决方案空间,我们必须根据给定的配置合成所得到的电路进行全方位的尝试。使用现在的HLS工具,每种特定配置可能需要几分钟到半小时

2021-07-06 08:00:00

模拟过程完成没有0错误,但在合成期间显示错误。我无法找到错误。我在合成期间在HLS工具中收到这样的错误“在E中包含的文件:/thaus / fact_L / facoriall

2020-05-21 13:58:09

。Vivado HLS作为该套件的一个组件,能帮助设计人员将采用C/C++语言开发的算法编译为RTL,以便在FPGA逻辑中运行。Vivado HLS工具非常适用于嵌入式视觉设计。在此流程中,您用C/C++

2014-04-21 15:49:33

最近在测激光,用逻辑分析仪测出来的信号是0和1组成的信号。现在需要统计有效信号的个数。比如00100011101100,不管0和1的个数,只管1出现多少次,两个0之间不管有几个1都算是一个有效信号

2017-06-30 20:43:38

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

/C++进行设计,然后由Vivado HLS编译器将C代码综合成HDL描述,最后再进行逻辑综合得到网表,这个网表最终会被映射到具体的FPGA器件上。就像C语言或者其他高级语言针对不同的处理器架构有着

2020-10-10 16:44:42

【资料分享】Vivado HLS学习资料

2013-11-02 11:21:14

早安Xilinx Communitry,我有一个关于VIVADO IP中心设计流程的问题。设计针对Xilinx fpga的数字逻辑不仅仅有一种方法。您可以使用HLS和HDL进行设计。您可以使用纯

2019-03-29 09:14:55

Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis

2022-09-09 16:45:27

嗨,大家好,我有一个问题,在VIVADO HLS 2017.1中运行C \ RTL协同仿真。我已成功运行2014和2016版本的代码。任何人都可以告诉我为什么报告NA仅用于间隔

2020-05-22 15:59:30

Vivado 2017.4、Xilinx VivadoHLS 2017.4、Xilinx SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持

2021-02-19 18:36:48

,证明了这种方法的有效性和优越性【关键词】:自适应滤波器;;LMS算法;;滤波器优化设计;;粒子群算法;;可重构硬件【DOI】:CNKI:SUN:JMDB.0.2010-01-001【正文快照】:0

2010-04-26 16:13:08

你好,我使用Vivado HLS生成了一个IP。从HLS测量的执行和测量的执行时间实际上显着不同。由HLS计算的执行非常小(0.14 ms),但是当我使用AXI计时器在真实场景中测量它时,显示3.20 ms。为什么会有这么多差异? HLS没有告诉实际执行时间?等待回复。问候

2020-05-05 08:01:29

嗨,大家好,我是新手SDK用户。我使用vivado hls来合成一个简单的图像处理算法,并构建了我现在使用sdk的硬件平台,我想使用sdk在独立模式下使用opencv应用程序在zynq fpga上

2020-05-04 17:09:19

案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-01-01 23:52:54

案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-08-24 14:40:42

7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。Xilinx Vivado HLS

2023-01-01 23:46:20

7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。Xilinx Vivado HLS

2023-08-24 14:54:01

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

你好我正在尝试在vivado HLS中创建一个IP,然后在vivado中使用它每次我运行Export RTL我收到了这个警告警告:[Common 17-204]您的XILINX环境变量未定义。您将

2020-04-03 08:48:23

尊敬的先生,由于突然断电我的桌面电脑在vivado HLS正在进行我的代码的C-Synthesis时关闭了,电源恢复后我启动计算机并尝试启动HLS,然后小方形HLS符号来了(我把屏幕截图放在了注册

2020-04-09 06:00:49

我照着xapp1167文档,用HLS实现fast_corners的opencv算法,并生成IP。然后想把这个算法塞到第三季的CH05_AXI_DMA_OV5640_HDMI上,这个demo里

2017-01-16 09:22:25

您好我有一个关于vivado hls的问题。RTL是否来自xivix FPGA的vivado hls onyl?我们可以在Design Compiler上使用它进行综合吗?谢谢

2020-04-13 09:12:32

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

2020-03-25 09:04:39

你好,我有一个与switch语句的合成有关的问题。我开始使用Vivado HLS并且我已经创建了一个小的file.cpp,仅用于学习,但是当Vivado HLS合成文件时,我没有得到任何开关语句

2019-11-05 08:21:53

请问Vivado HLS出现这种情况是什么原因呢

2021-06-23 06:13:13

您好,我目前正在尝试使用Vivado HLS在FPGA上合成加密算法。我根据需要拆分了C ++代码并包含了一个测试平台,但是当我尝试模拟代码时,我得到一个错误,说找不到测试平台。我附上了错误图片和项目档案,希望有人能帮我找到解决方案。谢谢!LBlock_fpga.zip 48 KB

2020-05-15 09:26:33

Vivado HLS设计流程是怎样的?

2021-06-17 10:33:59

这是我从Vivado HLS获得的。如您所见,一旦完成合成,Vivado HLS就会提供延迟信息。当我使用VHDL代码运行vivado时,如何获得这种延迟?我运行了testbench和模拟,但我仍然没有获得延迟信息。请帮忙!谢谢!!

2020-05-01 15:20:12

嗨伙计,在我的PC Vivado设计套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2没有打开,这就是为什么我想重新安装Vivado HLS 2015.2。如何下载

2018-12-27 10:57:49

针对粗粒度可重构处理器的特点,提出一种二维离散余弦变换的设计方法,该方法在硬件资源受限的条件下,有效地挖掘了算法的并行性,结果证明算法在速度和资源利用率方面均

2009-04-14 08:44:42 18

18 设计了一款新的应用于 多媒体处理 领域的可重构多媒体流处理器。该可重构多媒体 流处理器 采用并行处理机制,在经过算法映射后,可以充分利用多媒体算法的高并行度,同时实时处

2011-08-18 14:48:29 21

21 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 testbench来验证设计。 Integrate带有Xilinx IP Block的 HLS IP 这里展示了在IP Integrator中,如何将两个HLS IP blocks跟Xilinx IP FFT结合在一起 ,并且在Vivado中验证设计。

2017-02-07 17:59:29 4179

4179

众所周知 Hackaday.com 网站上聚集着众多极客(Geeker),他们打破传统,标新立异,敢于尝试新的东西,今天这篇文章搜集了这些极客对Xilinx Vivado HLS工具使用经验和心得

2017-02-08 20:01:59 550

550

大,我是否能够利用Vivado HLS完成这项要求较高的运算呢? 我开始从软件方面考虑这个转换,我开始关注软件界面。毕竟,HLS创建专用于处理硬件接口的硬件。幸好Vivado HLS支持创建AXI slave的想法,同时工作量较少。 我发现Vivado HLS编码限制相当合理。它支持大多数C + +语言

2017-02-09 02:15:11 310

310 本实验练习使用的设计是实验1并对它进行优化。 步骤1:创建新项目 1.打开Vivado HLS 命令提示符 a.在windows系统中,采用Start>All Programs>Xilinx

2017-02-09 05:07:11 411

411

在使用高层次综合,创造高质量的RTL设计时,一个重要部分就是对C代码进行优化。Vivado Hls总是试图最小化loop和function的latency,为了实现这一点,它在loop

2017-11-16 14:44:58 3362

3362 接口(ORI)标准压缩算法可以分析其对信号保真度,延迟以及实现成本。Vivado HLS是一个评估实现压缩算法非常高效的软件平台。 无线数据带宽的增长使得新一代的网络要具备新的能力,例如更高阶MIMO

2017-11-17 02:25:41 1267

1267

使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者

2017-11-17 17:47:43 3293

3293

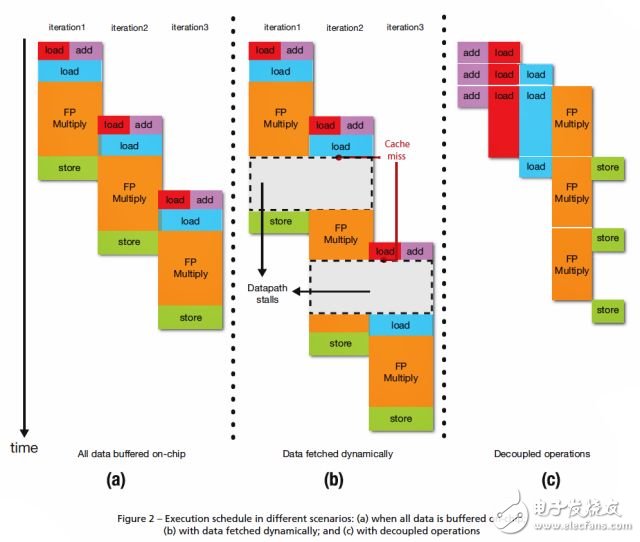

如果您正在努力开发计算内核,而且采用常规内存访问模式,并且循环迭代间的并行性比较容易提取,这时,Vivado® 设计套件高层次综合(HLS) 工具是创建高性能加速器的极好资源。通过向C 语言高级算法描述中添加一些编译指示,就可以在赛灵思FPGA 上快速实现高吞吐量的处理引擎。

2017-11-17 18:12:01 1647

1647 1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

2017-12-04 10:07:17 0

0 在实际工程中,如何利用好这一工具仍值得考究。本文将介绍使用Vivado HLS时的几个误区。

2018-01-10 14:33:02 19813

19813

本文内容介绍了基于用Vivado-HLS为软件提速,供参考

2018-03-26 16:09:10 7

7 Vivado HLS 是 Xilinx 提供的一个工具,是 Vivado Design Suite 的一部分,能把基于 C 的设计 (C、C++ 或 SystemC)转换成在 Xilinx 全可编程芯片上实现用的 RTL 设计文件 (VHDL/Verilog 或 SystemC)。

2018-06-05 10:31:00 6326

6326

我们使用 Vivado ®Design Suite 的高层次综合 (HLS) 工具来评估针对 E-UTRA I/Q 数据的开放无线电设备接口 (ORI) 标准压缩方案,以估计其对信号保真度的影响、造成的时延及其实现成本。我们发现赛灵思的 Vivado HLS 平台能够高效评估和实现所选压缩算法。

2018-07-24 09:30:00 1901

1901

OPENCV(Open Source Computer Vision)被广泛的使用在计算机视觉开发上。使用Vivado HLS视频库在zynq-7000全可编程soc上加速OPENCV 应用的开发,将大大提升我们的计算机视觉开发。

2018-11-10 10:47:49 1323

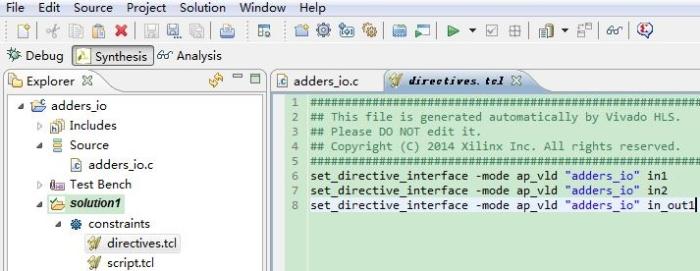

1323 了解如何使用GUI界面创建Vivado HLS项目,编译和执行C,C ++或SystemC算法,将C设计合成到RTL实现,查看报告并了解输出文件。

2018-11-20 06:09:00 3651

3651 了解如何生成Vivado HLS IP模块,以便在System Generator For DSP中使用。

2018-11-20 06:08:00 2940

2940 了解如何使用Tcl命令语言以批处理模式运行Vivado HLS并提高工作效率。

该视频演示了如何从现有的Vivado HLS设计轻松创建新的Tcl批处理脚本。

2018-11-20 06:06:00 2887

2887 尽管 Vivado HLS支持C、C++和System C,但支持力度是不一样的。在v2017.4版本ug871 第56页有如下描述。可见,当设计中如果使用到任意精度的数据类型时,采用C++ 和System C 是可以使用Vivado HLS的调试环境的,但是C 描述的算法却是不可以的。

2019-07-29 11:07:16 5072

5072

介绍了如何利用Vivado HLS生成FIR滤波算法的HDL代码,并将代码添加到ISE工程中,经过综合实现布局布线等操作后生成FPGA配置文件,下载到FPGA开发板中,Darren采用的目标板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 4554

4554 Vivado HLS中常见的接口类型有: 1. ap_none 默认类型,该类型不适用任何I/O转换协议,它用于表示只读的输入信号,对应于HDL中的wire类型。 2.

2020-12-26 11:44:10 6759

6759

HLS高阶综合(high level synthesis)在被广泛使用之前,作为商业技术其实已经存在了20多年。设计团队对于这项技术可以说呈现出两极化的态度:要么坚信它是先进技术之翘楚,要么对其持谨慎怀疑态度。

2020-11-04 13:45:03 3035

3035 Vivado HLS 2020.1将是Vivado HLS的最后一个版本,取而代之的是VitisHLS。那么两者之间有什么区别呢? Default User Control Settings

2020-11-05 17:43:16 37066

37066 本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2022-07-25 17:45:48 3058

3058

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2021-01-31 08:12:02 8

8 1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-06 09:20:58 6

6 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2022-09-02 09:06:23 2857

2857 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2023-01-15 11:27:49 1317

1317 HLS (high-level synthesis)称为高级综合, 它的主要功能是用 C/C++为 FPGA开发 算法。这将提升FPGA 算法开发的生产力。 Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 652

652

Xilinx平台的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令会无法导出 IP

2023-07-07 14:14:57 338

338

电子发烧友网站提供《UltraFast Vivado HLS方法指南.pdf》资料免费下载

2023-09-13 11:23:19 0

0 电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

2 电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

0

电子发烧友App

电子发烧友App

评论