本文介绍了基于FPGA、以并行多相滤波结构为算法基础的超宽带数字下变频技术。设计过程包括高速AD信号降速预处理,应用SysGen开发环境完成的数字混频、多相滤波和数据抽取,并通过仿真验证了算法

2014-02-22 10:23:41 3144

3144 N8201A性能下变频器,用户和SCPI编程指南

2019-10-30 08:40:15

问题,为什么不一次变频到70M呢.我想用adf4153可以一次就产生1020-1820的混频信号,为什么不这么做呢?问题二,是不是下变频的主电路都必须做50欧的阻抗控制(非数字部分).第三,有没有软件可以对整个电路,包括adf4113,adf4153在内的下变频,混频,滤波,电阻桥负载均衡等进行整体仿真

2015-09-20 11:47:07

AD采样80MHz,中频信号60MHz,在数字下变频时NCO输出频率设置为多少?

2017-02-15 16:00:19

数字下变频中的抽取和直接降低AD的采样率有什么区别?比如AD采样率100M,下抽倍数为4倍,和AD采样率25M有什么区别。

2017-11-03 21:53:13

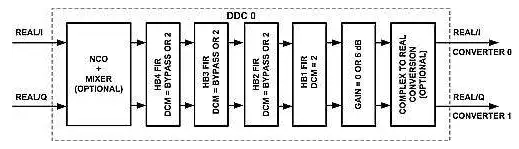

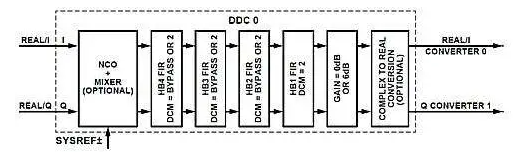

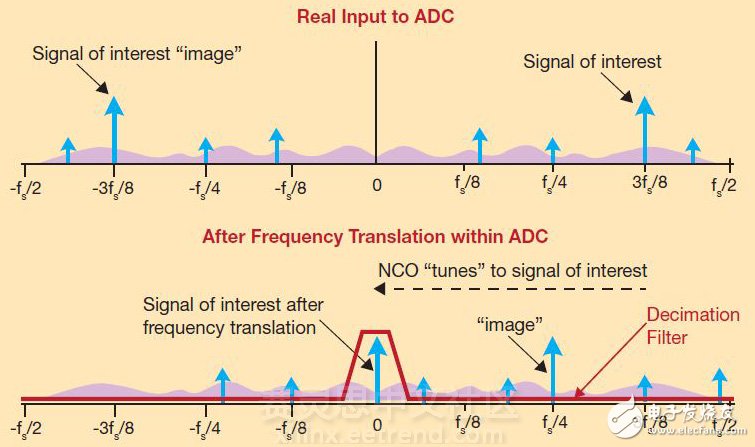

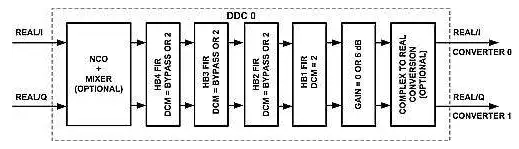

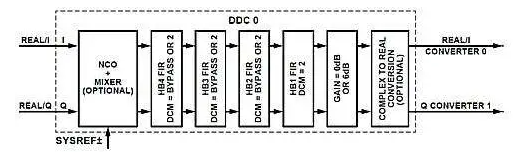

时的输入时钟为368.64 MHz,模拟 输入频率为270 MHz。首先,理解AD9680中数字处理模块的 设置很重要。AD9680将设为使用数字下变频器(DDC),其输 入为实数,输出为复数,数控

2018-11-01 11:19:48

数字上/下变频器:VersaCOMM™白皮书

2019-07-08 09:33:14

大多数字接收机对其采用的高性能模-数转换器(ADC)及模拟器件的要求都较高。例如,蜂窝基站数字接收机要求有足够的动态范围,以处理较大的干扰信号,从而把电平较低的有用信号解调出来。Maxim的15位

2019-08-09 08:23:54

FPGA收发器资源可以得到更好的分配,以接收所需的低带宽并疏导来自多个ADC的数据。可在FPGA的多相滤波器组信道器中针对频分复用 (FDM) 应用进行额外滤波。高性能GSPS ADC现将数字下变频

2019-06-14 05:00:09

为什么要开发一款高性能卫星应用手持终端?高性能卫星应用手持终端有什么优势?

2021-05-17 07:18:51

N8201A高性能下变频合成仪器模块3Hz-26.5GHz

2019-11-05 07:10:32

TI的工程师们你们好!目前在参考设计EEG的测量,使用过完整集成的EEG采集前端芯片ADS1299以及ADS1294,但是在使用过程中还是存在一些局限性,无法更自由的调整内部电路功能和进一步提高性能

2019-03-05 13:47:24

。LTC5510是一款1MHz至6GHz的有源混频器,可在极宽的输入带宽上提供高性能,该器件可用于上变频和下变频应用,具备灵活的电源,停机时功率极低,仅需要很低(0dBm)的LO驱动电平。图1显示了一个可用带宽为

2019-06-21 08:15:41

本帖最后由 eehome 于 2013-1-5 09:44 编辑

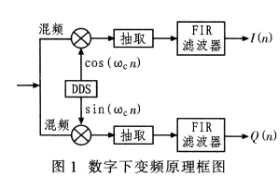

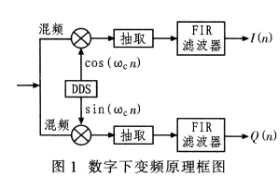

这是系统的一个模块,实现了数字下变频功能。

2012-06-06 15:59:13

与传统的模拟电源相比,数字电源的主要区别是控制与通信部分。在简单易用、参数变更要求不多的应用场合,模拟电源产品更具优势,因为其应用的针对性可以通过硬件固化来实现,而在可控因素较多、实时反应速度更快、需要多个模拟系统电源管理的、复杂的高性能系统应用中,数字电源则具有优势。

2020-10-29 06:03:50

小弟最近在做一个数字下变频和脉冲压缩的仿真,现在一点头绪都没有,有没有大神指教一下方向的。希望大神不吝赐教,或者是有源代码能分享一下,跪谢了。

2017-03-11 10:50:24

分享一个不错的高性能数字ANC主动降噪方案

2021-06-17 10:55:27

可满足高性能数字接收机动态性能要求的ADC和射频器件有哪些?

2021-05-28 06:45:13

影响,测量精度不高;而数字式频谱分析仪由于其基于数字滤波器,故而形状因子小,频率分辨率高,稳定性好,可以获得很窄的分析带宽,而测量精度较高;而且由于它基于高速ADC技术、数字信号处理技术、FFT分析等进行

2019-06-05 06:30:45

近年来,软件无线电已经成为通信领域一个新的发展方向,数字下变频技术(Digital Down Converter-DDC)是软件无线电的核心技术之一,也是计算量最大的部分。基于FPGA的DDC

2019-10-12 08:17:00

基于FPGA设计了一高速数字下变频系统,在设计中利用并行NCO和多相滤波相结合的方法有效的降低了数据的速率,以适合数字信号处理器件的工作频率。

2019-09-26 07:06:35

采用ADC(LTC2208)、FPGA和SDRAM(HY57V561620)设计高速的数据采集及正交下变频系统,其中数据采样速率90MSPS;实现70M中频的数字正交下变频…………请求大牛的帮助啊,我是小菜鸟,这方面还需要你们的大力提携啊,万分感谢

2014-04-01 10:44:33

数字上变频/下变频(DUC/DDC)是数字中频设计的重要组成部分,其功能是将基带信号经过内插滤波后变到中频的频率,或者将中频的信号经过抽取滤波后降到基带的频率上。

2019-08-21 06:24:03

数字上变频/下变频(DUC/DDC)是数字中频设计的重要组成部分,其功能是将基带信号经过内插滤波后变到中频的频率,或者将中频的信号经过抽取滤波后降到基带的频率上。本文的主要目的就是介绍多天线多载波数字上下变频的FPGA实现方法,以及Altera提供的一种数字信号处理的工具,DSP BUILDER。

2019-09-25 08:22:51

数字上变频/下变频(DUC/DDC, digital up convert/ digital down convert)是数字中频设计的重要组成部分,其功能是将基带信号经过内插滤波后变到中频的频率

2019-08-09 06:52:39

如何成功实现高性能数字无线电?

2021-05-24 06:25:47

软硬件相结合的方式进行,把计算量最大的数字下变频和抽取系统用专门的硬件芯片实现,其原理仍然通过多类滤波器的分组级联实现。尽管目前的硬件DDC芯片已经可以达到很高的性能要求,但终究与软件无线电的思想相悖

2009-10-23 10:26:53

IF。该高性能双平衡混频器可用于上变频或下变频。该混频器采用2 mm × 3 mm、12引脚小型QFN封装,提供23 dBm IIP3和14 dBm P1dB。采用3.3 V电源供电时,混频器功耗为132

2021-01-08 07:58:43

针对频分复用(FDM) 应用进行额外滤波。高性能GSPS ADC现将数字下变频(DDC)功能在信号链中进一步提升,以使其位于基于赛灵思FPGA的设计解决方案的ADC之中。该方案为高速系统架构师提供了多种

2019-07-29 07:14:03

成功实现高性能数字无线电

2020-12-22 06:59:41

,因为关于样本的信息要到ADC处理完信号之后才能确定。现在,高性能GSPS ADC让数字下变频(DDC)功能在信号链中前移,进驻到ADC内部。这就给高速系统架构师提供了多种新的设计选择。然而,这一功能

2018-10-26 11:16:21

的全部带宽,因为关于样本的信息要到ADC处理完信号之后才能确定。 现在,高性能GSPS ADC让数字下变频(DDC)功能在信号链中前移,进驻到ADC内部。这就给高速系统架构师提供了多种新的设计选择

2018-08-06 06:40:16

本文介绍了一种应用于数字化中频频谱分析仪的数字下变频电路,整个电路基于FPGA实现,结构简单,易于编程实现。

2021-04-15 06:21:22

RF:2.401GHz~2.473GHz IF: 中频输出大概在70M左右射频输入频率范围如上所示。求助下变频芯片推荐

2012-03-14 19:01:37

、处理并消耗功率传输宽带频谱的效率很低。没有必要在后期处理中使用大量FPGA收发器来抽取和过滤宽带数据。高性能GSPS ADC让数字下变频(DDC)进驻到ADC内部。减少JESD204B ADC输出通道数可以最大限度地降低数据速率和系统布局的复杂度。

2019-07-22 08:41:38

简要阐述数字下变频器的发展和更新

2021-05-19 06:22:14

高性能和高可用性链路的需求。电信通的运营经理说:“我们在这期间出现的机会数量感到惊讶。“我们研究了一些替代方案,但是在考虑产品的成本和可用性的同时,快速提供所需的额外带宽的唯一方法是使用Mimosa

2017-03-13 10:50:42

数字滤波器的实现一般有哪几条途径?宽带无线通信的数字上下变频是什么?滤波器的输入数据流有什么特点?

2021-04-14 06:21:44

GC5016及其结构是什么?怎样去设计GC5016数字上下变频系统的硬件部分?怎样去设计GC5016数字上下变频系统的软件部分?

2021-05-24 06:49:59

传递函数在目标窄带内具有低陷的非平坦形状。在此带中,CTSD ADC的工作性能最高,并且SNRFS达到最大。

ad6676是一款新型CTSD IF接收器子系统,在20-160MHz可调谐频带上,其噪声

2023-12-11 08:14:37

讨论了软件无线电接收机中数字下变频处理技术中的CIC抽取滤波器结构原理,分析了CIC滤波器级联ISOP滤波器进行抽取滤波的设计技术。验证了ISOP滤波器对CIC滤波器带内衰减补偿的有

2009-05-26 20:44:21 21

21 本文介绍了数字下变频的组成结构,并通过一个具体的实例,给出了FPGA 实现的具体过程。

2009-11-30 14:11:52 34

34 FPGA在软件无线电中的工程应用之数字上下变频篇

2010-02-09 11:10:36 59

59 在微型SAR 实时成像样机的设计中,对雷达回波在中频进行采样,然后采用数字下变频技术实现正交解调,可以减少系统的复杂性,提高雷达的数字化程度和性能。该文针对微型SAR 方

2010-02-09 11:59:45 17

17 介绍了一种基于新型FPGA的高速数字下变频的实现方法,它充分利用数字下变频的优化算法以及FPGA领域的新技术,去除由于数据速率过高而造成的各种瓶颈,极大地减少了计算量和FPG

2010-07-02 16:49:24 21

21 数字下变频是软件无线电系统的重要组成部分,主要完成对信号的混频、滤波、抽取和整形等工作,包括数字混频模块和抽取滤波模块。在数字下变频系统实现方案中,输入的模拟

2010-11-02 15:26:27 48

48 基于FPGA芯片Stratix II EP2S60F672C4设计了一个适用于宽带数字接收机的带宽可变的数字下变频器(VB-DDC)。该VB-DDC结合传统数字下变频结构与多相滤波结构的优点,实现了对输入中频信

2010-11-11 15:56:54 57

57 针对传统正交数字下变频器结构计算效率低,首先介绍一种基于混频器后置的改进方法,该方法只能使得

2010-11-25 17:06:39 36

36

数字接收机中高性能ADC和射频器件的动态性能要求

今天的基站系统不得不

2006-05-07 13:41:54 1369

1369 数字下变频器中坐标变换模块的ASIC实现

1.引言 数字下变频(DDC)技术是软件无线电接收机的核心技术。其基本功能是从输人的宽带高速数字信

2007-08-15 16:32:54 1249

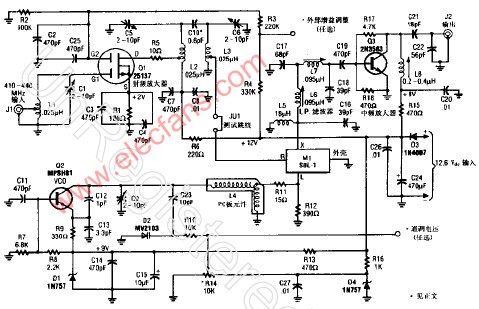

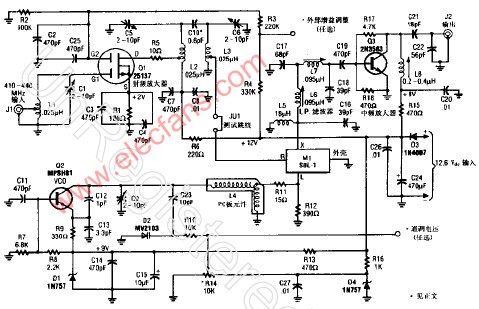

1249 ATV信号下变频器

该射频

2009-09-14 10:41:45 2206

2206

高性能∑-ΔADC-MAX1403的原理及应用

MAX1403是一种18位、过采样的ADC芯片,它利用∑-Δ调制器和数字滤流器可实现真正的16位转换精度

2009-12-07 22:02:21 914

914

数字下变频是软件无线电系统的重要组成部分,主要完成对信号的混频、 滤波、抽取和整形等工作,包括数字混频模块和抽取滤波模块。在数字下变频系 统实现方案中,输入的模拟中

2011-03-29 10:02:47 96

96 电路功能与优势 本电路提供一种高性能、双通道IF采样接收机;在基站术语中,它也称为主接收机和分集接收机。该下变频接收机使用153.6 MHz的单IF频率,内置一个双通道下变频混频器

2011-03-31 09:48:19 28

28 本文以某雷达对抗侦察数字接收机为例,介绍一种基于TI公司的DSP TMS320C6416的数字下变频器。

2011-08-09 11:15:54 2425

2425

宽带短波信道模拟器是一种运用仿真技术对真实的短波信道进行模拟的仪器。首先指出数字下变频在宽带短波信道模拟器中的作用。然后,阐述了数字下变频中的数控振荡器、CIC 滤波器

2011-09-15 18:30:21 1669

1669

阐述了雷达中频正交采样的原理,研究了使用System Generator实现数字下变频的一种自顶向下的新型设计方法。在Simulink中进行了功能仿真验证.

2012-02-09 15:13:48 46

46 FPGA在软件无线电中的工程应用之数字上下变频篇

2016-04-25 09:38:10 8

8 基于FPGA的DDC数字下变频设计,有兴趣的同学可以下载学习

2016-04-27 16:18:12 59

59 一种基于流水线DA算法的数字下变频器_周云

2017-01-07 22:14:03 2

2 数字下变频程序,可直接用于项目

2017-08-30 08:45:24 23

23 功能模块并组成模块库。在具体应用时,优化配置各个模块来满足具体无线通信系统性能的要求。 数字下变频技术在移动通信、数字广播、电视等领域具有重要应用价值。

2017-11-22 09:09:56 5706

5706

高性能GSPSADC为基于赛灵思FPGA的设计解决方案带来板载DDC功能 宽带每秒数千兆个样本(GSPS)模数转换器(ADC) 为高速采集系统带来众多性能优势。这些ADC在高采样率和输入带宽下提供

2017-11-22 18:44:01 343

343

数字上变频/下变频(DUC/DDC)是数字中频设计的重要组成部分,其功能是将基带信号经过内插滤波后变到中频的频率,或者将中频的信号经过抽取滤波后降到基带的频率上。本文的主要目的就是介绍多天线多载波数字

2017-11-25 02:31:01 259

259

下变频率芯片GC5016同时实现宽带和窄带信号的变频;采用FPGA实现对宽/窄带数据的接收和存储,存储后数据使用高性能 DSP 芯片C6455实现对这些数据的处理。文中详细介绍了该系统的软硬件设计方法。

2017-12-05 09:49:31 3044

3044

数字上变频/下变频(DUC/DDC)是数字中频设计的重要组成部分,其功能是将基带信号经过内插滤波后变到中频的频率,或者将中频的信号经过抽取滤波后降到基带的频率上。本文的主要目的就是介绍多天线多载波数字上下变频的FPGA实现方法,以及Altera提供的一种数字信号处理的工具,DSP BUILDER。

2019-03-13 15:16:58 1743

1743

重新思考快速宽频ADC中的数字下变频

2018-04-23 10:41:12 1

1 本文介绍了基于0.18μm CMOS工艺的802.11a无线局域网1GHz频段正交下变频电路的设计方法。该设计采用源级退化和电流注入的方法对传统的吉尔伯特混频单元进行改进,实现了高性能下变频器。

2019-05-23 08:28:00 2499

2499

数字上变频/下变频(DUC/DDC)是数字中频设计的重要组成部分,其功能是将基带信号经过内插滤波后变到中频的频率,或者将中频的信号经过抽取滤波后降到基带的频率上。本文的主要目的就是介绍多天线多载波数字

2018-09-15 04:57:00 2800

2800 高性能RX和DPD集成RF前端,包括LNA、µW下变频器、LO和14位四通道ADC,具有相位同步功能,可为大型数据转换器阵列提供时钟

2019-06-14 06:01:00 3355

3355 整个软件无线电系统的稳定性产生直接影响。采用专用DDC器件完成数字下变频,虽具有抽取比大、性能稳定等优点,但价格昂贵,灵活性不强,不能充分体现软件无线电的优势。FPGA工艺发展迅速,处理能力大大

2020-08-06 15:31:17 728

728

系统先将射频信号模拟混频至统一的中频信号,使用ADC器件对其采样,采样后的中频信号经过数字下变频器即图中的DDC模块变为低速的基带信号再送往DSP进行实时信号处理它在整个软件无线电系统中的主要作用

2020-09-01 16:02:00 7

7 研究了高倍抽取的数字下变频设计,重点分析了基于级联积分梳状滤波器和级联半带滤波器的多级抽样频率算法。并提出了用最新的Systemgenerator软件实现FPGA 的设计、仿真方案,缩短了开发周期

2020-11-05 17:04:55 14

14 数字上/下变频器简介:VersaCOMM™可重构数字转换器

2021-05-12 20:53:04 0

0 AD6636:150 MSPS、宽带、数字下变频器(DDC)数据表

2021-05-27 20:46:49 4

4 基于FPGA的DDC(数字下变频)设计与实现(电源技术审稿费多少)-该文档为基于FPGA的DDC(数字下变频)设计与实现讲解文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-09-15 12:04:22 28

28 基于FPGA的数字下变频器(DDC)的设计(ups电源技术转让)-基于FPGA的数字下变频器(DDC)的设计.适合新手学习参考

2021-09-16 11:43:52 37

37 在本文的第一部分“数字下变频器——第1部分”中,我们探讨了行业对更高频率RF频段采样的推动,以及数字下变频器(DDC)如何实现这种类型的无线电架构。讨论了与AD9680系列产品中的DDC相关的几个技术方面。

2023-01-05 14:28:21 1997

1997

应用设计的上/下变频器,它由混频器、内部LO以及可选的中频和射频滤波器组成,内部LO具有出色的相位噪声性能。虹科TYMTEK UD Box可以被配置为上变频器、下变频器或两者同时进行。 虹科上/下变频器TYMTEK

2023-04-10 10:12:08 0

0 下变频器(Downconverter)用于将高频信号转换为较低频率的信号。输入信号的幅度(即信号的电压或功率级别)会对下变频的影响产生以下几个方面的影响。

2023-06-07 10:18:25 544

544 回想一下示例中,AD9680-500的工作输入时钟为491.52 MHz,模拟输入频率为150.1 MHz。AD9680设置为使用数字下变频器(DDC),具有实输入、复数输出、155 MHzNCO

2023-06-30 15:18:00 717

717

在本例中,我们将介绍AD9680-500,其工作输入时钟为491.52 MHz,模拟输入频率为150.1 MHz。AD9680将设置为使用数字下变频器(DDC),具有实际输入、复数输出、155

2023-06-30 15:20:25 747

747

电子发烧友网站提供《数字下变频在人工智能引擎上的实现应用说明.pdf》资料免费下载

2023-09-13 15:06:31 0

0

电子发烧友App

电子发烧友App

评论