早前,多家客户已经收到全新英特尔 Stratix 10 GX 10M FPGA样片,该产品是全球密度最高的FPGA,拥有1020 万个逻辑单元,现已量产。该款元件密度极高的FPGA,是基于现有

2019-11-06 12:13:28 5510

5510 非晶硅反熔丝FPGA技术尤其有用,它可以提供一种高电路密度与低功耗,以及非易失性编程和高可靠性的组合。为了充分发挥其可靠性,FPGA厂商需要考虑反熔丝的崩溃(wear-out)机制,并通过一种

2011-05-27 09:55:42 1968

1968 电子发烧友网核心提示 :目前在高可靠领域应用的FPGA器件大约可占整个FPGA市场份额的10%~15%。对FPGA企业而言,高安全性或许不失为一条差异化的发展路径。 目前FPGA的应用不断扩展,

2012-10-17 09:43:44 1058

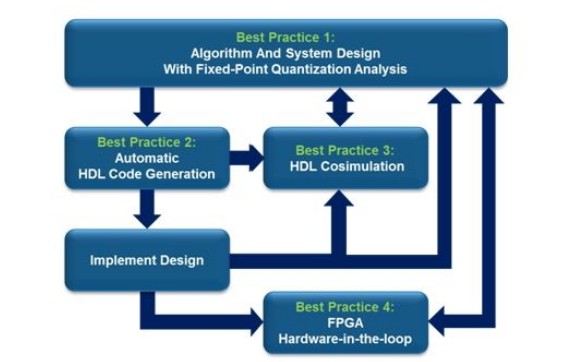

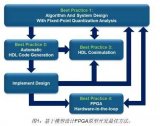

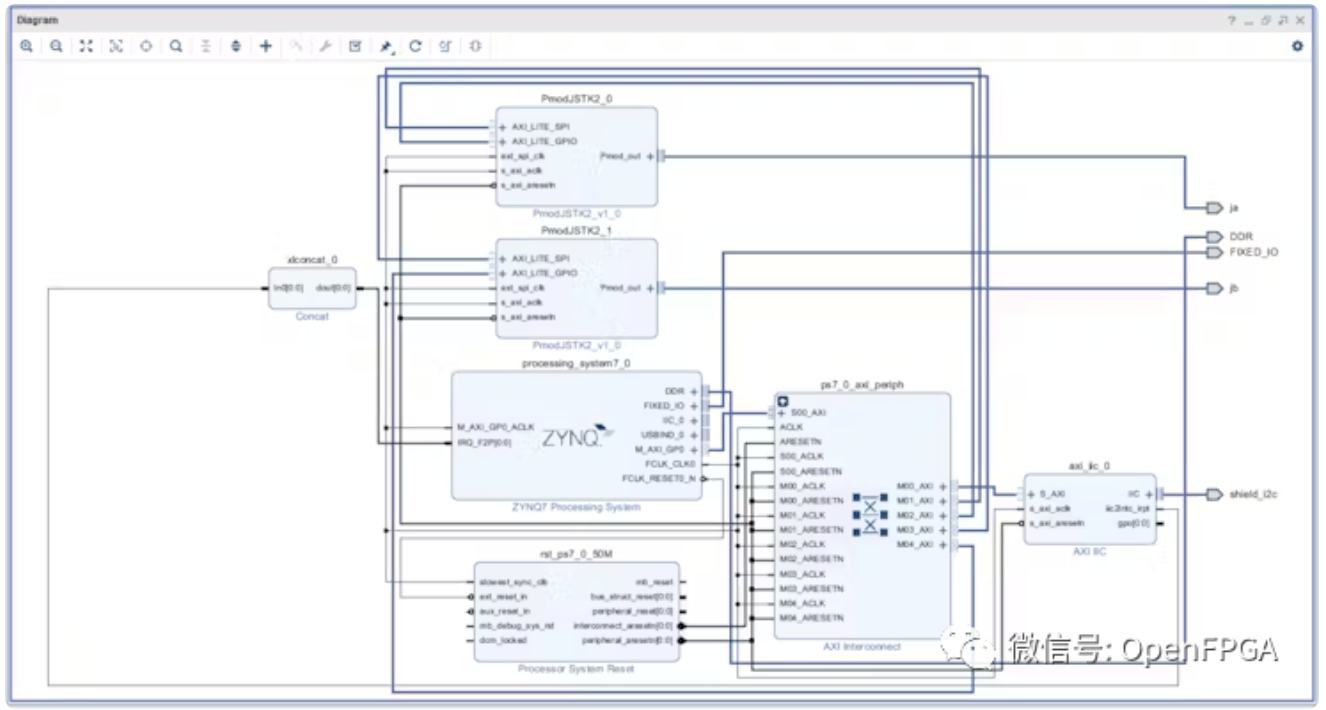

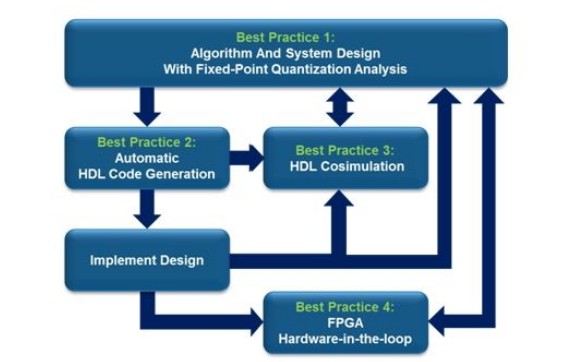

1058 本文将介绍使用MATLAB和Simulink创建FPGA原型的最佳方法。这些最佳方法包括:在设计过程初期分析定点量化的效应并优化字长,产生更小、更高效的实现方案;利用自动HDL代码生成功能,

2013-01-28 11:08:08 16036

16036

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 8153

8153 使用Vivado 2018.1 第二篇:mig IP的创建 1 DDR3 Digilent的Arty Artix-35T FPGA开发板板载MT41K128M16JT-125 DDR3基本信息如下表所示

2020-12-16 15:47:59 1692

1692

本文列出了FPGA设计中常见的十个错误。我们收集了 FPGA 工程师在其设计中犯的 10 个最常见错误,并提供了解决方案的建议和替代方案。本文假定读者已经具备 RTL 设计和数字电路方面的基础。接下来让我们深入探讨在FPGA 设计中要避免的 10 大错误。

2023-05-31 15:57:28 529

529

FPGA 非常适合精密电机控制,在这个项目中,我们将创建一个简单的电机控制程序,在此基础上可以构建更复杂的应用。

2023-08-11 09:06:33 753

753

国微思尔芯发布3亿门原型验证系统,采用业界最高容量的 Intel® Stratix® 10 GX 10M FPGAs。

2020-09-08 10:56:20 883

883 本帖最后由 lee_st 于 2017-10-31 09:00 编辑

10分钟学会FPGA设计

2017-10-21 20:23:56

10分钟学会FPGA设计

2017-09-27 10:57:47

文档创建既然是ROM,那么我们就必须实现给它准备好数据,然后在FPGA实际运行时,我们直接使用这些预存储好的数据就行。Xilinx FPGA的片内ROM支持初始化数据配置。如图所示,我们可以创建一个名为

2019-04-08 09:34:43

1. 概要本篇文章主要介绍在FPGA设计中如何使用本GXFPGA驱动创建一个中断事件/请求。2. 简介中断作为硬件与软件握手和同步的手段而被广泛使用,可用于表示硬件进程的完成或软件执行过程中的请求

2018-08-31 15:12:06

了3款足够“有料”的FPGA及SoC系列:Arria 10、Stratix 10以及MAX 10,它们都是Altera在创新大潮中重磅推出的“第10代”(Generation 10)产品,也为

2019-07-01 08:14:44

请问各位大神,在没有终端的情况下,如何创建一个带有FPGA终端(NI PXLe-5840)的Labview项目?

2018-03-20 17:30:34

本帖最后由 一只耳朵怪 于 2018-6-7 10:23 编辑

该装的驱动都装了,但是就是没办法创建FPGA项目。在MAX理可以看到NI PCI 7833R可以看到 RTFPGANI RIO

2018-06-06 20:22:17

NetFPGA-10G是什么?它有什么功能?

2021-05-25 06:13:28

在英特尔® Stratix® 10 FPGA 上的实施方案。对于大批量任务,该方案能以每瓦 每秒 70 幅图像的速度每秒处理 14,000 幅图像;对于批量大小为 1 的任务,该方案能 以每瓦每秒

2019-07-17 06:34:16

请问一下Stratix 10 MX FPGA是什么?Stratix 10 MX FPGA有哪些功能?

2021-07-09 08:08:06

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

`Xilinx FPGA入门连载8:Verilog源码文件创建与编辑特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 Verilog

2015-09-21 11:18:07

The Artix-7 is part of the 7-Sseries of FPGA's from Xilinx. Containing 1,156 pins, creating

2014-02-13 09:24:15

。但如果你是新的FPGA技术,记住这一点,这不是最简单的设计,以了解关于这个站点。HDL设计或如何创建示波器在FPGA内部逻辑。一部分1 -设计FIFO为主。第2部分 -基于RAM的设计。3部分 -触发

2012-04-09 14:55:29

项目名称:FPGA+c8051高可靠性通用核心板卡试用计划:基于max10系列fpga和c8051设计一款2*3cm大小核心板 提供40个gpio 双路uart。mcu的io通过fpga桥接 另外提供u***转uart功能。板载epprom

2018-10-24 17:20:21

本文以星载测控系统为背景,提出了一种基于 Actel Flash FPGA的高可靠设计方案。采用不易发生单粒子翻转的 flash FPGA芯片,结合 FPGA内部的改进型三模冗余、分区设计和降级重构,实现了高实时、高可靠的系统。

2021-05-10 06:58:47

`勇敢的芯伴你玩转Altera FPGA连载79:FPGA片内ROM实例之ROM初始化文档创建特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2018-06-20 22:04:28

本文详细讨论了基于FPGA的mif文件创建与使用,对于mif文件创建与使用均给出了两种可行性的方法。mif文件具有固定格式,而对mif文件使用主要就是对mif。文件begin与end之间的内容进行修改。本文以四位二进制加法查找表的实现为例,给出了m(Matlab)语言源程序。

2021-05-06 06:04:19

完成数据采样,并添加SDRAM和EEPROM模块来扩展FPGA芯片的存储资源、降低数据丢失的风险。在完成设计之后,本文针对性地设计了可靠性评估方法,确定本文所设计实现的可靠性等级为0.625,具有较高

2018-05-03 12:25:32

基于Multisim 10的电子电路可靠性研究利用Multisim 10平台进行电子电路设计的可靠性研究,可以有效地解决传统分析方法难以对电子电路设计进行容差精确分析的技术问题。方法为统计取样法,其

2012-07-20 09:39:18

请问如何使用LabVIEW和FPGA来创建一个自动化的微控制器测试系统?

2021-04-09 06:08:00

为了FPGA保证设计可靠性, 需要重点关注哪些方面?

2019-08-20 05:55:13

目前,汽车中使用的复杂电子系统越来越多,而汽车系统的任何故障都会置乘客于险境,这就要求设计出具有“高度可靠性”的系统。同时,由于FPGA能够集成和实现复杂的功能,因而系统设计人员往往倾向于在这些系统中采用FPGA。

2019-09-27 07:45:33

我安装了FPGA Module 但按照帮助里说的总是创建不了 各位帮帮 最好能把关键步骤截个图

2010-12-05 20:31:23

请帮帮我。我无法在FPGA中创建可用信号。(引脚FPGA中的网关输出)显示错误。焊盘位置的数量必须与驱动该网关输出的信号的位数相匹配。格式必须指定为单元格数组,例如{'MSB',...,'LSB

2019-09-10 12:44:58

缺陷成团对FPGA片内冗余容错电路可靠性的影响是什么?缺陷成团对冗余容错电路可靠性的影响是什么?

2021-04-08 06:50:18

如何创建一个可靠、低成本、简单的电感测试仪?

2021-04-14 06:05:52

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包软件。提供了一些基础的函数库以及常用的控制函数模块,配合

2022-05-19 09:16:05

概述EasyGo FPGA Solver是EasyGo开发的专门部署在FPGA 硬件上的解算器软件。根据不同的应用需求,会有不同的FPGA Solver 选择

2022-05-19 09:21:43

EP4CE10F17C8N,Cyclone IV FPGA设备,INTEL/ALTERAEP4CE10F17C8N,Cyclone IV FPGA设备,INTEL

2023-02-20 17:00:57

EP4CE10F17I7N,Cyclone IV FPGA设备,INTEL/ALTERAEP4CE10F17I7N,Cyclone IV FPGA设备,INTEL

2023-02-20 17:03:19

本文以星载测控系统为背景,提出了一种基于Actel Flash FPGA 的高可靠设计方案。采用不易发生单粒子翻转的Flash FPGA 芯片,结合FPGA 内部的改进型三模冗余、分区设计和降级重构,

2010-01-20 14:35:53 21

21 mif文件的创建与使用是在基于FPGA的系统设计中引入ROM的关键环节。对mif文件的创建与使用展开详细讨论,给出两种可行性方法,并引入实例在MAX+PLUS Ⅱ环境下做了详细的仿真

2010-12-13 17:47:29 42

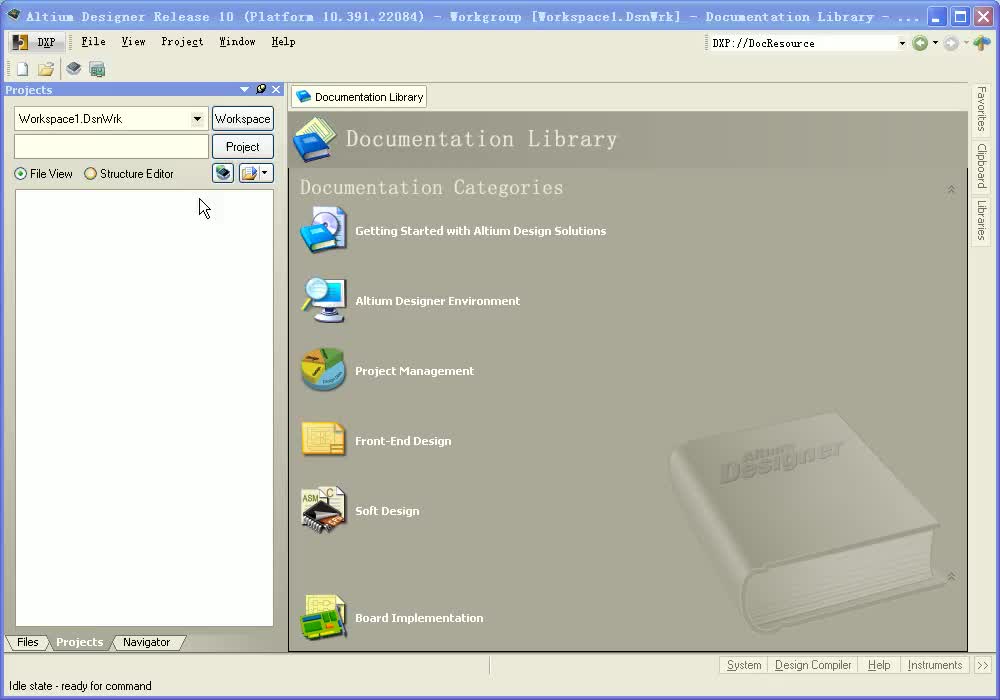

42 OrCAD FPGA系统规划

创新的FPGA - PCB协同设计

该Cadence ®的OrCAD ® FPGA系统提供了一个完整的策划,为FPGA - PCB协同设计,使用户能够创建可扩展解决方案的

2010-08-30 17:49:26 1748

1748

摘要:为提高8B/10B编解码的工作速度和简化逻辑方法,提出一种基于FPGA的8B/10B编解码系统设计方案。与现有的8B/10B编解码方案相比,该方案是一种利用FPGA实现8B/lOB编解码的模块方

2011-05-26 11:08:20 3364

3364

Altera于6月11日在北京宣布,全球同步推出10代FPGA和SoC。先行发布的包括高端Stratix10和中端Arria10系列。目标是替代传统的ASSP和ASIC。

2013-06-13 14:26:14 2150

2150 在Altera的MAX®10现场可编程门阵列(FPGA)系列发布之际,艾睿电子公司(NYSE:ARW)推出了BeMicro Max 10FPGA评估板。

2014-10-08 09:58:21 2451

2451 ADC_Convertor_Using_MAX_10_FPGA_Development_Kit

2015-12-07 18:20:15 9

9 QNX程序创建指南

2017-01-03 17:40:48 0

0 通过在FPGA设计流程引入功率分析改善PCB的可靠性

2017-01-14 12:36:29 7

7 Flash 和反熔丝架构FPGA为汽车应用提供灵活、可靠和安全的平台

2017-01-18 20:35:09 13

13 参加 FPGA 功率优化班,将帮助您创建更高电源效率的 FPGA 设计。通过本课程的学习,将有助于您的设计满足更小型化的 FPGA 器件,降低 FPGA 功耗,或在更低的温度下运行

2017-02-09 06:24:11 167

167 编译FPGA VI至FPGA应用前必须创建一个程序生成规范。

2017-11-18 02:46:52 706

706 使用FPGA终端创建应用程序前,必须创建一个LabVIEW项目。然后添加FPGA终端至该项目并创建FPGA VI。

2017-11-18 02:47:23 2228

2228 可靠传输方面实现了MAC 层的流控以及错误包检测功能。仿真以及实际平台测试表明,该通信协议能够实现FPGA 片间万兆的线速通信。 云计算服务目前在互联网上急速增长,其通过互联网来提供动态易扩展的资源。

2017-11-18 08:13:01 15054

15054

针对空间辐照效应影响的高可靠性设计,将越来越成为FPGA软硬件设计的难点和重点。根据飞行器空间轨道的不同、辐射总剂量的差异,从硬件上,可以通过加厚屏蔽层、元器件加固等方式,尽可能地降低SEU发生

2017-11-24 15:30:01 2294

2294 Intel 再次隆重介绍了自家的 Stratix 10 TX FPGA芯片 。 这是地球上最快的FPGA芯片,浮点性能达到10TFLOPS(每秒10万亿次),简单来说,可以在1秒内处理420张蓝光

2018-04-23 05:55:00 7830

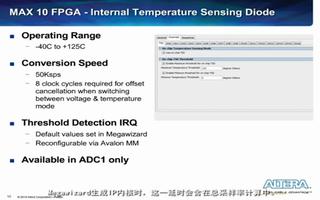

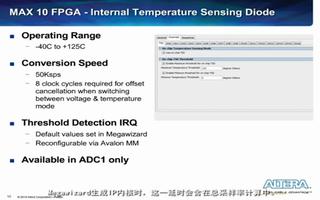

7830 MAX 10 FPGA模拟模块培训,此次培训介绍MAX 10 FPGA中的ADC是怎样工作的,怎样对其进行配置,怎样在硬件中测量其性能。

2018-06-20 12:00:00 4044

4044

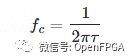

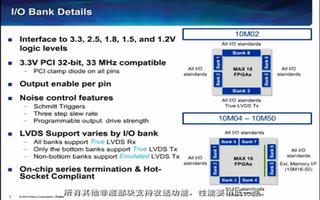

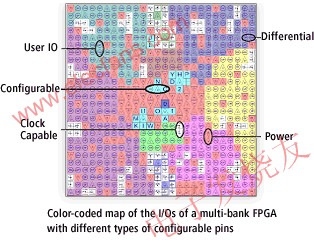

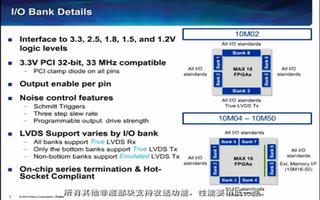

MAX 10 FPGA GPIO培训,可编程逻辑一般用作胶合逻辑,连接电路板上的大量数字逻辑器件,这些器件通常有不同的I/O标准、电压电平和协议。这里列出了我们I/O特性的很多优势。MAX 10 FPGA支持多种I/O标准和特性,因此,与其他可编程逻辑方案相比,Altera是最佳选择。

2018-06-20 05:00:00 2371

2371

此次培训涉及到MAX 10 FPGA所支持的配置方法,介绍非易失集成、瞬时接通配置和双配置镜像的价值所在。

2018-06-20 08:00:00 2248

2248 如何创建英特尔 Stratix 10 后配置BSDL 文件

2018-06-22 10:09:00 2922

2922 本篇文章主要介绍在FPGA设计中如何使用本GXFPGA驱动创建一个中断事件/请求。

中断作为硬件与软件握手和同步的手段而被广泛使用,可用于表示硬件进程的完成或软件执行过程中的请求。Gx3500

2018-09-07 14:34:18 6

6 FPGA的I / O优化提供了一个自动化的FPGA符号生成过程集成的原理图和PCB设计,节省天的PCB设计创建时间的整体质量和准确性,同时增加你的原理图符号。

2019-10-16 07:06:00 2292

2292 根据Tom's Hardware的报道,今天,英特尔推出了世界上最大的FPGA芯片Stratix 10 GX 10M,搭载433亿个晶体管,拥有1020万个逻辑元件,使用EMIB将两个FPGA芯片和四个收发芯片连接在一起。

2019-11-07 14:32:19 4049

4049 在北京举办的 IntelFPGA 技术大会上,Intel 发布全球最大容量的全新 Stratix 10 GX 10M FPGA。这是全球密度最高的 FPGA,拥有 1020 万个逻辑单元,433 亿颗晶体管,现已量产,即日出货。

2019-11-20 17:11:21 1026

1026 Microsoft将全力投入Windows 10,最终实现了拥有可跨平台运行的应用程序的梦想。结合对Arduino的官方支持,您可以使用一个功能强大的新工具:能够轻松创建具有与现实世界硬件连接的通用Windows应用程序的功能。

2019-12-03 08:53:13 2365

2365 本文档的主要内容详细介绍的是FPGA 10K10单片机配置的PCB原理图免费下载。

2020-10-14 14:52:00 20

20 为实现高效可靠的网络传输协议,依据RUDP草案并引人TCP可靠机制,设计一种基于消息包、面向连接的高速可靠网络传输协议 ORUDP。通过创建确认机制、重传机制、流量控制机制和双队列加速机制等实现

2021-03-31 15:47:18 16

16 中,小编为大家分别总结了英特尔 Cyclone FPGA和英特尔 Stratix 10 FPGA的应用之路,今天就轮到咱们的英特尔 Arria 10 FPGA了~ 英特尔 Arria 器件家族

2021-05-31 09:42:42 2704

2704 AGM FPGA之AG10K 系列的开发建议(连载二)

2021-12-05 17:21:14 25

25 (10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 BASIC 10 Liner Contest 的目标是用 10 行 BASIC 语言创建一个完整的电脑游戏。

2022-07-30 17:21:42 1555

1555

LiteX 框架为创建 FPGA 内核/SoC、探索各种数字设计架构和创建完整的基于 FPGA 的系统提供了方便高效的基础架构。

2022-09-13 09:04:14 1179

1179 电子发烧友网站提供《安路科技SALEAGLES10 FPGA数据手册.pdf》资料免费下载

2022-09-27 10:39:10 1

1 要求:创建10个普通用户,并给它们设置随机密码,将密码记录到一个文档里,用户名为user_01 — user_10,密码要求包含大小写字母以及数字,密码长度15位。

2022-10-31 09:14:51 1150

1150 电子发烧友网站提供《使用FPGA创建RISC V系统.zip》资料免费下载

2022-11-08 10:26:45 1

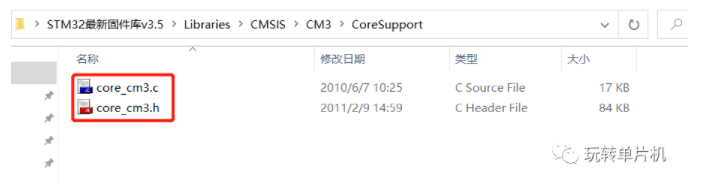

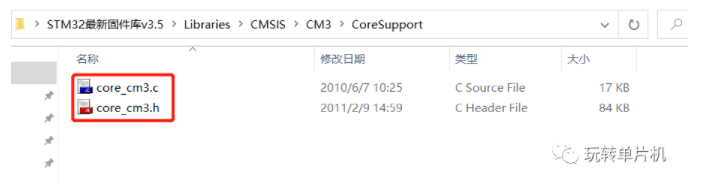

1 创建一个工程文件夹,并且在文件夹里创建三个文件夹并分别以CORE、STM32F10X_LIB、USER命名。

2023-02-10 14:38:55 841

841

proFPGA 四模块英特尔 Stratix 10 GX 10M FPGA 原型设计系统采用 4 个基于英特尔 Stratix 10 GX 10M FPGA 的可插拔 FPGA 模块。

2023-03-17 11:22:30 470

470 点击蓝字,关注我们购置了贵司E103-W10Wi-Fi模块,不会创建UDP通信,怎么办?不用担心,E103-W10UDP使用示例教程附上。前期配置设置E103-W10的WiFi模式,连接到路由器

2022-05-27 10:52:00 1416

1416

LiteX 框架为创建 FPGA 内核/SoC、探索各种数字设计架构和创建完整的基于 FPGA 的系统提供了方便高效的基础架构。

2023-06-28 09:08:05 425

425

FPGA 设计工程师需要对如何创建系统以及使用行业软件和工具有深入的了解。在软件方面,设计工程师必须知道如何建模自己的设计,并通过一系列测试保证正确的运行。业界有许多这种高级建模程序,包括Matlab,Simulink,Octave,Verdi等等。

2023-08-01 09:20:51 414

414 芯片设计和验证工程师通常要为在硅片上实现的每一行RTL代码写出多达10行测试平台代码。验证任务在设计周期内可能会占用50%或更多的时间。尽管如此辛 苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以发现系统级错误,芯片设计人员正利用FPGA来加速算法创建和原型设计。

2023-08-06 10:49:09 977

977

本文开源一个FPGA高速串行通信项目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收发器,本工程主要是围绕该IP核采用Vivado提供的例程创建。

2023-10-01 09:48:00 2604

2604

机器人技术处于工业 4.0、人工智能和边缘革命的前沿。让我们看看如何创建 FPGA 控制的机器人手臂。

2023-10-24 17:15:33 456

456

机器人技术处于工业 4.0、人工智能和边缘革命的前沿。让我们看看如何创建 FPGA 控制的机器人手臂。

2023-10-24 17:26:20 935

935

如何创建二维数组在Python中是一个常见的问题。在Python中,我们可以使用嵌套的列表(list of lists)或者使用NumPy库来创建二维数组。在本文中,我们将详细介绍这两种方法,以及

2023-11-21 15:10:43 830

830

电子发烧友App

电子发烧友App

评论