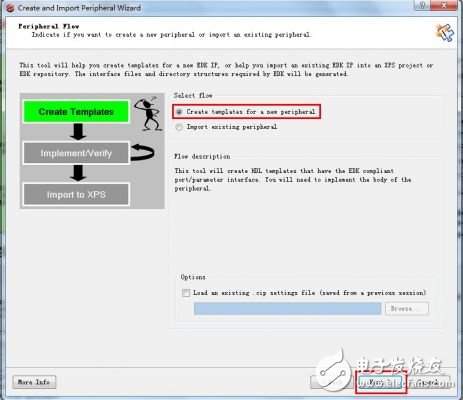

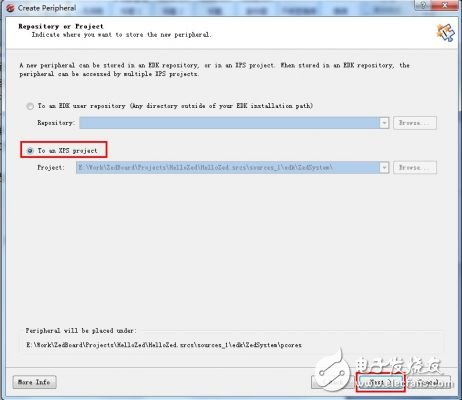

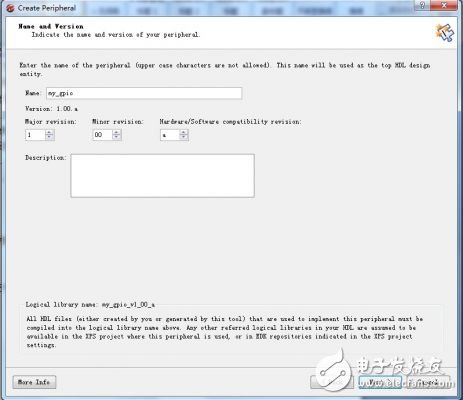

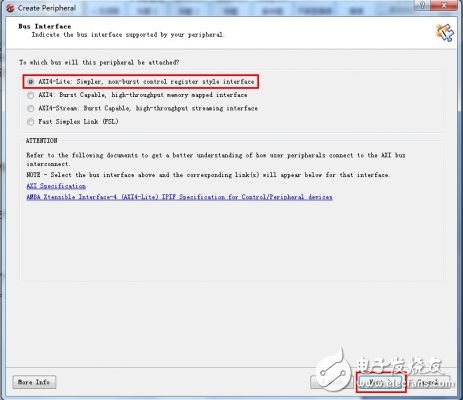

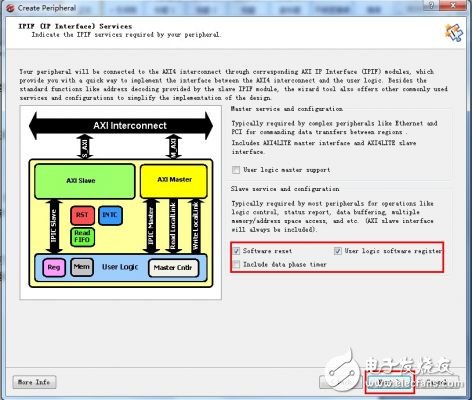

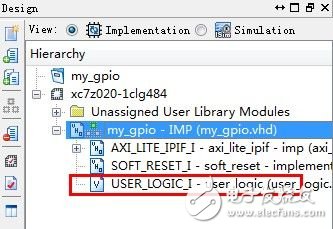

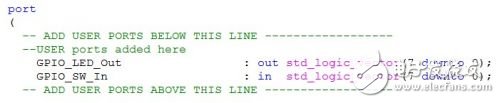

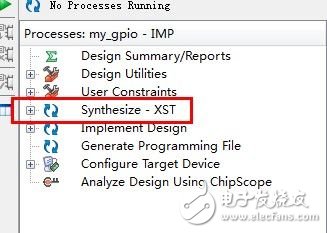

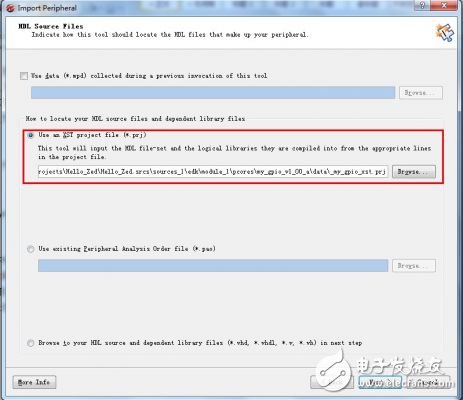

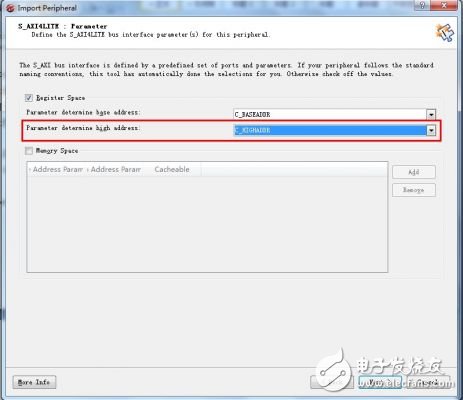

本小节通过使用XPS中的定制IP向导(ipwiz),为已经存在的ARM PS 系统添加用户自定IP(Custom IP ),了解AXI Lite IP基本结构,并掌握AXI Lite IP的定制方法,为后续编写复杂AXI IP打下基础。同时本小

2012-12-23 15:39:12 11129

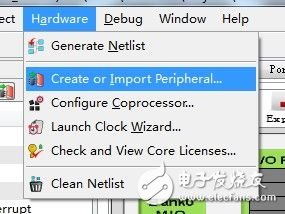

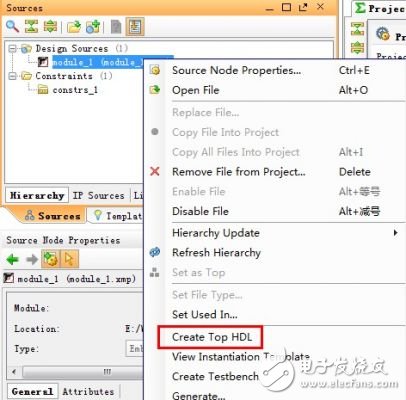

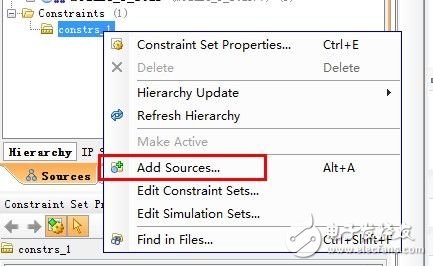

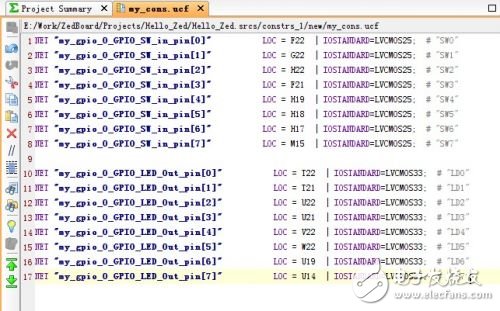

11129 作者:Mculover666 1.实验目的 用HDL语言+Vivado创建一个挂载在AXI总线上的自定义IP核 2.实验步骤 2.1.创建一个新的项目 2.2.调用Create

2020-12-21 16:34:14 3088

3088

如何为APP推送设置独特的通知铃声呢?本次带来的是MobPush对安卓端自定义铃声的教程,快来看看吧~

2023-10-21 15:34:05 773

773

自定义 带子 自定义 胶合剂 自定义 自定义 X 自定义

2024-03-14 22:58:08

嗨, 当我在XPS中创建自定义AXI外设时,AXI ID(ARID,AWID)在生成的包装器中不可用。我如何获得这些ID?谢谢。以上来自于谷歌翻译以下为原文Hi, When I create a

2019-03-21 09:00:19

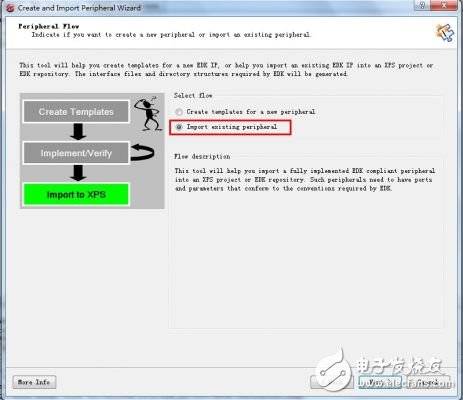

你好,我使用创建和导入向导创建我自己的IP,然后我通过fsl链接我的ip与microblaze接口,但是我不能通过fsl得到输出所以在自定义ip vhdl code.tell我需要更改需要我,如果

2020-03-11 09:59:27

自定义外设和自定义指令在SOPC系统中是如何运行的?怎样去验证?

2021-05-26 06:33:55

本文转载自《OpenHarmony应用开发之自定义弹窗》,作者:zhushangyuan_

应用场景

在应用的使用和开发中,弹窗是一个很常见的场景,自定义弹窗又因为极高的自由度得以广泛应用。本文

2023-09-06 14:40:27

的fifo接口),用户只要操作fifo接口,无需关心PCIE的内部驱动。为了便于读者更加明白,可以深入了解PCIE,我们将会制作一个PCIE的连载系列。今天,首先说一下自定义AXI4的IP核,至于AXI

2019-12-13 17:10:42

STM32总线外设是如何分布的?

2021-09-27 06:48:55

(1个):是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。我们可以双击查看ZYNQ的IP核的内部配置,就能发现上述的三种

2018-01-08 15:44:39

ZYNQ自定义AXI总线IP应用——PWM实现呼吸灯效果一、前言 在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能。要想使自定义IP核被CPU访问

2020-04-23 11:16:13

sopc builder中添加自定义ip,编写自定义ip核的时候, avalon接口信号:clk、rst

2013-11-26 11:11:22

这学期一个半月了都在学习自定义外设,开始时做最简单的从外设,到后来的主外设。一个接着一个做,已经完成了三个自定义外设的设计。 做了这几个外设后,感觉学到了很多东西。在调试中遇到了很多问题,但都一一

2018-07-03 10:02:41

你好,我如何启用自定义IP的中断。我使用vivado HLS生成了IP。中断线连接到ZYNQ的中断端口。以下是设备树{amba_pl:amba_pl {#address-cells

2020-05-01 16:46:48

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:40:28

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:39:13

我写了一个缓存模块,里面包含有一个BlockRAM的IP核,现在想把这个缓存模块封装成我的一个自定义ip,但是封装完成之后仿真的时候会报错 ,我的步骤是这样的:1.写一个.v文件,里面是我的缓存控制

2018-12-11 10:25:41

嗨,我正在使用zynq zc702,我设计了几个自定义ip,它们用verilog模块编写,并且将驻留在PL部分,现在我的设计工作正常,ps和pl通信意味着即用自定义ip的arm完成..但是我

2019-03-04 13:02:20

zynq的PS如何向一个基于AXI4-FULL协议的自定义IP批量传输数据?

2017-02-22 12:05:35

小弟我是学习FPGA嵌入式的新手,最近在学习使用zedboard开发板,在研究zedboard_CTT_V14.4官方例程的时候,按照附录的程序,一直报错,表示添加的外设DEVICE_ID没有定义

2015-04-22 20:54:49

是Vivado中十分常用的自定义IP核,使用AXI接口的IP,能够方便的连接到软核(MicroBlaze)或硬核(Zynq)的总线上,方便软核或硬核对其进行读写操作。本设计的重点是使用FPGA逻辑设计独立

2016-12-16 11:00:37

LED_IP、IIC_IP1.2搭建基本硬核、AXI接口、GPIO外设1.3自定义IP:File->NewIP Location 1.4记得要在 led_ip_v1_0.v声明接口wire、在

2015-06-11 23:52:23

到Qsys系统以外的逻辑2、内部寄存器和线网的定义 数据寄存器(读/写) 状态寄存器(IP运行状态、数据状态……) 控制寄存器 中断屏蔽寄存器 用户自定义寄存器3、Avalon总线对寄存器的读写 //写入数据

2020-02-25 18:47:04

),数据)对自定义IP的第n个寄存器进行写入操作可以使用IORD(基地址,寄存器编号(n)) 对自定义IP的第n个寄存器进行读出操作如果使用动态地址对齐,(每个寄存器在Avalon总线上占 数据位宽/8

2020-02-27 19:20:59

8.1.1 系统框图框图中的UART用于打印信息,Breath LED IP核为自定义的IP核,McroBlaze处理器通过AXI接口为LED IP模块发送配置数据,从而来控制LED灯。8.2实验任务

2020-10-17 11:52:28

的方式来自定义IP核,支持将当前工程、工程中的模块或者指定文件目录封装成IP核,当然也可以创建一个带有AXI4接口的IP核,用于MicroBlaze软核处理器和可编程逻辑的数据通信。本次实验选择常用的方式

2020-10-19 16:04:35

Vivado软件中,通过创建和封装IP向导的方式来自定义IP核,支持将当前工程、工程中的模块或者指定文件目录封装成IP核,当然也可以创建一个带有AXI4接口的IP核,用于PS和PL的数据通信。本次实验

2020-09-09 17:01:38

`附件为小梅哥SOPC公开课第二课NIOS II自定义IP的设计与使用的建随堂工程。小梅哥SOPC公开课第二课主要讲解如何使用Verilog自己编写一个符合NIOS II Avalon MM接口总线

2016-08-13 11:04:32

)!问题是这样的:我开发NIOS II,基本上都是自己编写IP核的,比较省资源,自由度也高,而自定义IP核,都是要用上自定义中断的(IRQ),更新版本后(13.1),出现下在一个问题,请看图: 看图

2014-05-06 13:06:30

我正在为 OTA 目的开发自定义引导加载程序。我在一个假设下成功地做到了这一点,即 .bin 文件可以被 4 整除。这意味着因为它是 32 位的,所以即使最后一部分也会在一个完整的存储单元中。这是正确的吗?

2023-01-06 09:02:47

如何使用BMLang开发自定义的算子

2023-09-18 06:57:11

如何在Libero的开发环境下封装通用的自定义的IP核?请各位大侠指点!

2019-11-13 23:09:18

我正在尝试在 Nucleo-H743ZI2 评估板上开发自定义引导加载程序。但是引导加载程序不会跳转到应用程序代码。我参考了有关该主题的其他帖子,并从中采纳了一些代码。我已经将应用程序和引导加载程序的代码闪存到 0x8020000 和 0x8000000 的相应内存位置。请指出我提供的代码中的问题。

2023-01-29 07:02:52

断开连接的应用程序提供支持。在这里,我的问题是如何开发自定义连接器..?我没有 sailpoint 提供的包含“AbstractConnector”类的 jar 文件。这样我就可以编写自己的课程并进

2023-04-27 06:24:53

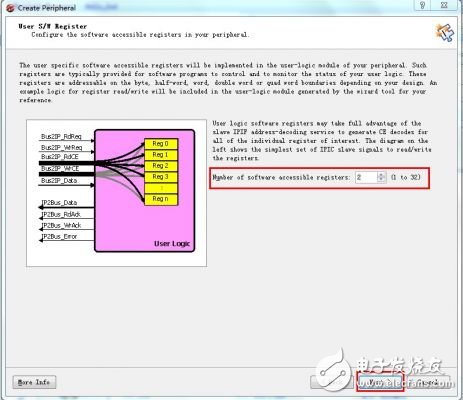

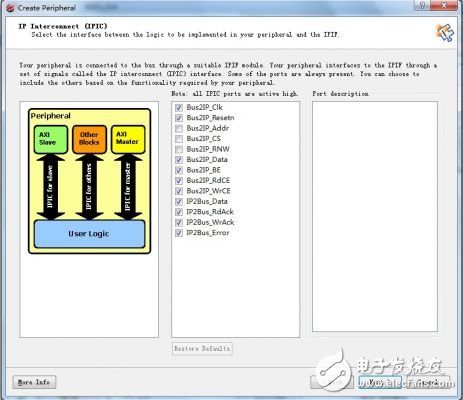

嗨!我使用Xilinx EDK创建了一个自定义IP,没有什么特别的,只是向导创建的默认IP,它连接到AXI Lite。它还使用一个寄存器为用户逻辑创建了模块。 (附带用户逻辑文件)地址范围

2019-08-12 09:38:23

大家好,我正在使用zedboard创建一个AXI接口应用程序,以突发模式从ARM发送64字节数据到FPGA。为此,我在vivado中创建了一个自定义AXI从站,选择它作为AXI FULL(因为AXI

2020-08-12 10:37:46

嗨,我开始使用Vivado了。我正在尝试配置从Dram读取数据的自定义IP,处理它们然后将结果发送到Bram控制器。我想过使用AXI主接口制作自定义IP。但是,我不知道将AXI主信号连接到我的自定义逻辑,以便我可以从Dram读取数据并将结果发送到Bram。谢谢。

2020-05-14 06:41:47

我看到 Espressif 提供了二进制映像和 Windows 工具,以适应其产品的 WiFi 和蓝牙的 FCC 测试。是否有任何支持 API 以便我可以开发自己的自定义固件以进行 FCC 测试?请注意,我们的产品中还有其他 RF 无线电,因此我们需要开发自定义固件以在多个无线电之间进行共存测试。

2023-03-02 08:11:16

1、构建自定义AXI4-Stream FIR滤波器 AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程

2022-11-07 16:07:43

`玩转Zynq连载23——用户自定义IP核的创建与封装更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接:https

2019-09-09 10:55:24

`玩转Zynq连载24——用户自定义IP核的移植更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接:https://pan.baidu.com/s

2019-09-15 09:55:57

`玩转Zynq连载25——[ex04] 基于Zynq PL的自定义IP核集成更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接:https

2019-09-20 11:35:29

无论是做SOC设计还是FPGA设计,AXI4总线是经常提及的。关于AXI4总线关于什么是AXI4总线的定义,网络上相关的文章不胜枚举,也是无论是做FPGA还是ASIC都是必须要了解和掌握的知识,这里

2022-08-02 14:28:46

开发自定义组件目前还不是很丰富,在开发过程中常常会有一些特殊效果的组件,这就需要我们额外花一些时间实现,这里给大家提供了一个 BottomSheet 上拉抽屉的组件,同时通过这个组件示例讲解一下 HarmonyOS 中的几个自定义控件用到的知识,分享一下自己自定义组件的思路。

2022-03-16 16:05:53

EVAL-AD7960FMCZ评估版通过LPC接口与zedboard连接,在AXI总线上自定义了一个AD采集的IP核,然后把这个IP映射到虚拟地址空间,然后读取AD采集的数据通过以太网发送到pc机

2018-12-11 11:38:18

有意见了~今天带大家来设计一个自定义的IP核,我们从最基本的做起,包括datasheet 的理解,设计的整体框架,AD转换代码的编写,仿真,Avalon-MM总线接口的编写,硬件系统还是基于上次的硬件

2015-02-01 12:39:08

本文主要介绍了如何开发基于TCP/IP 协议网络编程的自定义通讯协议,在QNX,Linux 和Windows 三种不同的操作系统平台下实现多节点间的互相通讯。测试结果表明,该协议可以方便高

2009-05-30 09:16:04 14

14 自定义函数测试学习工程

2010-07-01 16:37:44 5

5 SOPC中自定义外设和自定义指令性能分析

NiosII是一个建立在FPGA上的嵌入式软核处理器,灵活性很强。作为体现NiosII灵活性精髓的两个最主要方面,自

2009-03-29 15:12:49 1490

1490

本文介绍了基于Avalon总线SHT11温湿度传感器自定义IP核的开发流程,利用有限状态机设计了驱动硬件逻辑,并且基于NiosII嵌入式处理器构建了一个用户定制的嵌入式系统。在SOPC中,设计人员可以灵活添加IP核,减轻设计负担,避免重复工作。

2013-01-28 18:41:04 3892

3892

AMBA AXI 总线学习笔记,非常详细的AXI总线操作说明

2015-11-11 16:49:33 11

11 1602液晶能够显示自定义字符,能够根据读者的具体情况显示自定义字符。

2016-01-20 15:43:51 1

1 Delphi教程自定义系统的About项,很好的Delphi资料,快来下载学习吧。

2016-03-16 14:46:37 3

3 JAVA教程之自定义光标,很好的学习资料。

2016-03-31 11:13:36 7

7 Labview之自定义错误,很好的Labview资料,快来下载学习吧。

2016-04-19 11:17:14 0

0 C#教程之自定义屏保,很好的C#资料,快来学习吧。

2016-04-20 09:59:37 7

7 C#教程之自定义动画鼠标,很好的C#资料,快来学习吧。

2016-04-20 14:46:25 4

4 基于模型设计—自定义目标系统配置指南,RTW自动代码生成相关资料。

2016-05-17 16:41:51 3

3 易语言是一门以中文作为程序代码编程语言学习例程:自定义信息框模块

2016-06-07 10:41:41 2

2 易语言是一门以中文作为程序代码编程语言学习例程:自定义进度复制文件

2016-06-07 10:41:41 7

7 易语言是一门以中文作为程序代码编程语言学习例程:自定义鼠标光标

2016-06-07 10:41:41 2

2 Xilinx FPGA工程例子源码:EDK中PS2自定义IP

2016-06-07 11:44:14 4

4 可以说zybo是mini-zedboard。Zybo全栈开发教程共分为三部分:自定义IP、移植Linux操作系统、编写驱动模块和应用。通过这三部分你将能够全面熟悉Zynq AP SoC架构的开发流程,包括FPGA逻辑电路设计、软件编程、Linux操作。

2017-11-10 14:49:02 3403

3403

,并对外设进行测试。以后还有一个很重要的自定义用户Ipcore设计,下个实验来做下这个(一开始以简单的led和sw为例)。这个实验就使用呢自带外设IP。

2017-02-09 14:23:11 1812

1812

认识zedboard板子也有半个多月了,期间有不少杂事,学的也不是很认真,最近几天在学习如何利用AXI总线进行PS和PL部分的相互通信,利用自定义的IP核实现了简易的计算功能(只有加减),下面对实验的过程和自己的理解进行一下记录。

2018-07-12 03:45:00 2370

2370

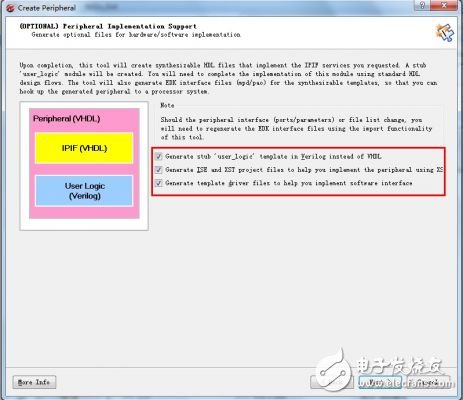

本小节通过使用XPS中的定制IP向导(ipwiz),为已经存在的ARM PS 系统添加用户自定IP(Custom IP ),了解AXI Lite IP基本结构,并掌握AXI Lite IP的定制方法,为后续编写复杂AXI IP打下基础。

2017-02-10 20:37:12 5407

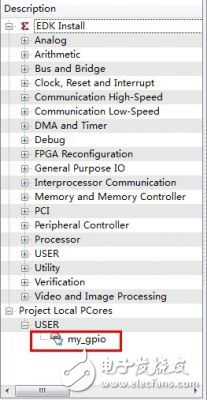

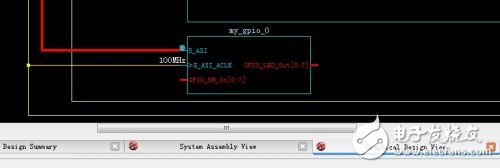

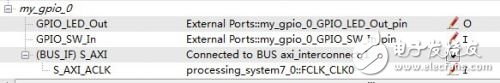

5407 今天所讨论的内容就是通过QT开发的GUI软件来控制ZedBoard板上的硬件外设,完整的信号链如下:QT GUI → Linux Driver → AXI Bus → My_GPIO

2017-02-11 01:28:12 1886

1886

本工程目的是自定义一个IP,用于对OV2643摄像头的进行配置。重点有3个,一是需要在定制板上建立系统(即我们使用的不是现有的开发板,无官方的板级支持包);二是自建IP;三是IIC总线在EDK

2017-09-15 17:25:30 12

12 本文包含两部分内容:1)AXI接口简介;2)AXI IP核的创建流程及读写逻辑分析。 1AXI简介(本部分内容参考官网资料翻译) 自定义IP核是Zynq学习与开发中的难点,AXI IP核又是十分常用

2018-06-29 09:33:00 14958

14958

Atmel小贴士 如何开发自定义应用程序

2018-07-11 00:05:00 2124

2124 了解如何使用Vivado的创建和封装IP功能创建可添加自定义逻辑的AXI外设,以创建自定义IP。

2018-11-29 06:48:00 6801

6801

自定义sobel滤波IP核 IP接口遵守AXI Stream协议

2019-08-06 06:04:00 3573

3573 完成后,请执行相同的操作,但不要选择自定义rom,而是选择间隙。安装间隙之前需要使用一些自定义rom,您可以从自定义rom的开发人员网页上了解,如果他们没有提及任何相关内容,只需在自定义rom

2019-11-05 10:48:24 4545

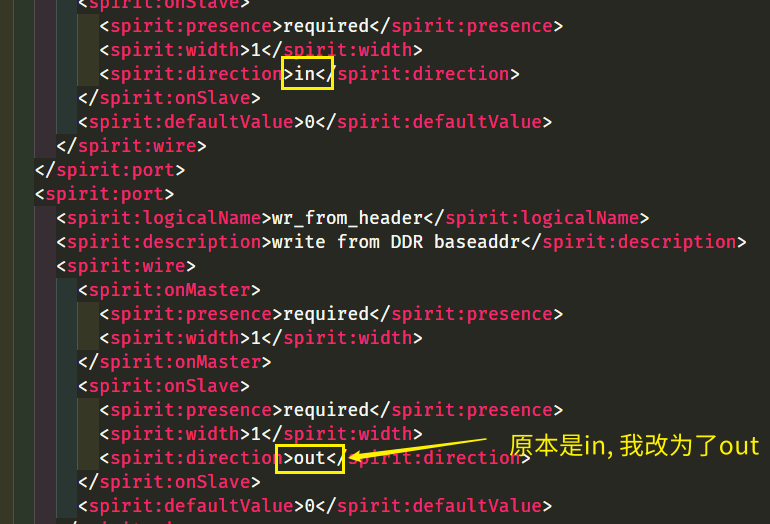

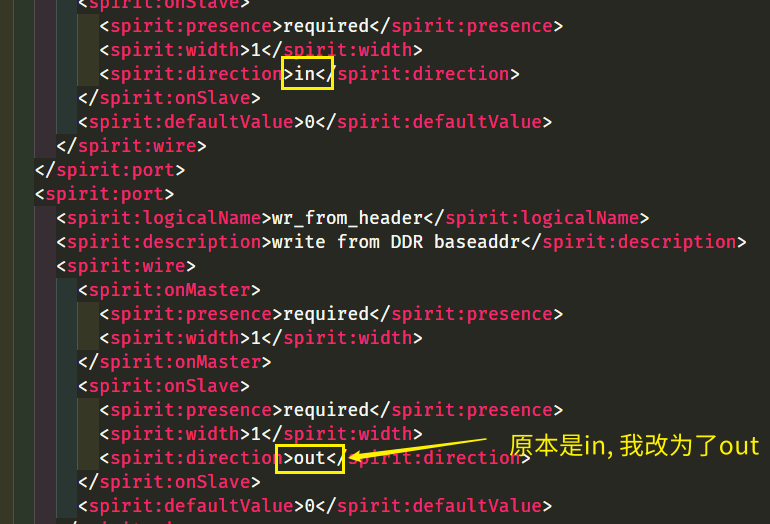

4545 因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。

2021-03-30 15:49:47 4420

4420

在实际开发过程中,我们经常会遇到一些系统原有组件无法满足的情况,而 HarmonyOS 提供了自定义组件的方式,我们使用自定义组件来满足项目需求。 自定义组件是由开发者定义的具有一定

2021-11-10 09:27:16 2233

2233

HarmonyOS 开发自定义组件目前还不是很丰富,在开发过程中常常会有一些特殊效果的组件,这就需要我们额外花一些时间实现。

2022-01-04 13:49:30 1761

1761 自定义组件 1.自定义组件-particles(粒子效果) 2.自定义组件- pulse(脉冲button效果) 3.自定义组件-progress(progress效果) 4.自定义组件

2022-04-08 10:48:59 14

14 因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。

2022-08-02 09:49:46 2247

2247

自定义弹窗其实也是比较简单的,通过CustomDialogController类就可以显示自定义弹窗。

2022-08-31 08:24:36 1354

1354 AWPLC 是 ZLG 自主研发的 PLC 系统(兼容 IEC61131-3),本文用定时器为例介绍一下如何扩展自定义功能块。

2022-10-26 11:50:01 654

654 AWPLC 是 ZLG 自主研发的 PLC 系统(兼容 IEC61131-3),本文以定时器为例介绍一下如何扩展自定义功能块,以及代码生成器的用法。

2022-11-02 13:22:05 700

700 教程 2:自定义配置文件示例

2023-03-13 19:33:00 0

0 教程 3:构建自定义配置文件

2023-03-15 19:39:12 0

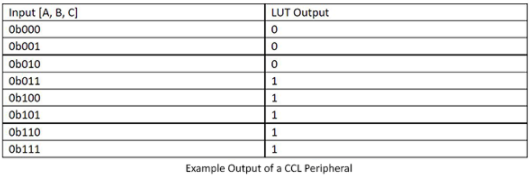

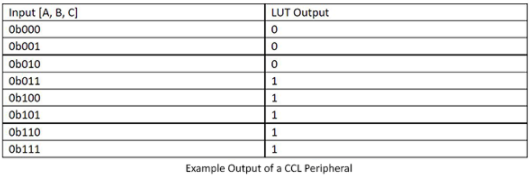

0 PIC® 和 AVR® 微控制器 (MCU) 上的自定义逻辑外设是功能强大的工具,可用于创建独立于 CPU 运行的分立逻辑小块。PIC 微控制器具有可配置逻辑单元 (CLC),而 AVR 微控制器

2023-05-06 09:51:42 562

562

labview自定义精美控件

2023-05-15 16:46:23 9

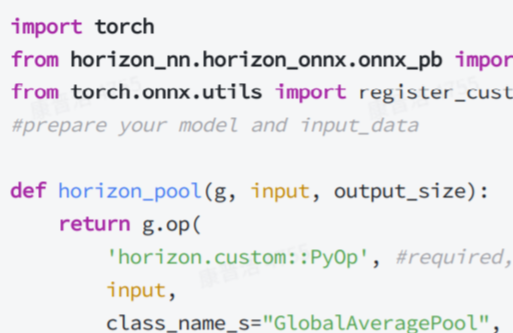

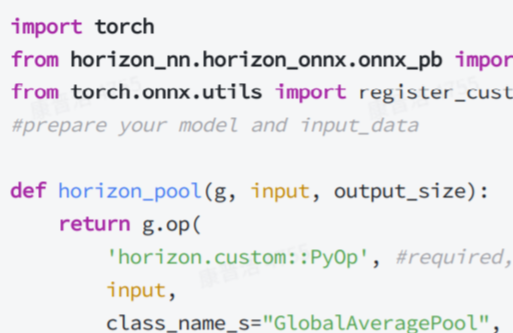

9 一个完整的自定义算子应用过程包括注册算子、算子实现、含自定义算子模型转换和运行含自定义op模型四个阶段。在大多数情况下,您的模型应该可以通过使用hb_mapper工具完成转换并顺利部署到地平线芯片上……

2022-04-07 16:11:21 1808

1808

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

2023-06-25 16:31:25 1914

1914

labview超快自定义控件制作和普通自定义控件制作

2023-08-21 10:32:58 5

5

电子发烧友App

电子发烧友App

评论