安全高效的状态机设计对于任何使用FPGA的工程师而言都是一项重要技能。选择Moore状态机、Mealy状态机还是混合机取决于整个系统的需求。无论选择哪种类型的状态机,充分掌握实现方案所需的工具和技巧,将确保您实现最佳解决方案。本文主要介绍如何在FPGA中实现状态机

2013-03-29 15:02:57 12361

12361

FPGA 对绝大多数的人来说相对有些陌生。经常有朋友问我,你们成天搞的这个 FPGA 到底是什么东西。 我想很难用一两句通俗易懂的语言解释什么是 FPGA ,因为当今的 FPGA 已经是一个非常复杂

2018-03-31 08:20:01 25704

25704 1. 初识XILINX 初识XILINX,是PYNQ-Z2。当时刚学完学校的数字电路课程,对FPGA并不了解,学校课程也仅仅是用VHDL验证了一些基础的FPGA实验,例如生成一个n进位序列

2020-11-05 15:56:42 4204

4204 即是相应的 HDL 程序以及最新非常流行的基于高层次综合的程序方法,如Xilinx的一系列工具HLS、SDSoC和Altera的SoC EDS等。 (1)选择FPGA(SoC)的若干理由 a)FPGA

2020-12-17 12:58:21 4094

4094 用软件从 C 转化来的 RTL 代码其实并不好理解。今天我们就来谈谈,如何在不改变 RTL 代码的情况下,提升设计性能。 本项目所需应用与工具:赛灵思HLS、Plunify Cloud 以及

2020-12-20 11:46:46 1416

1416

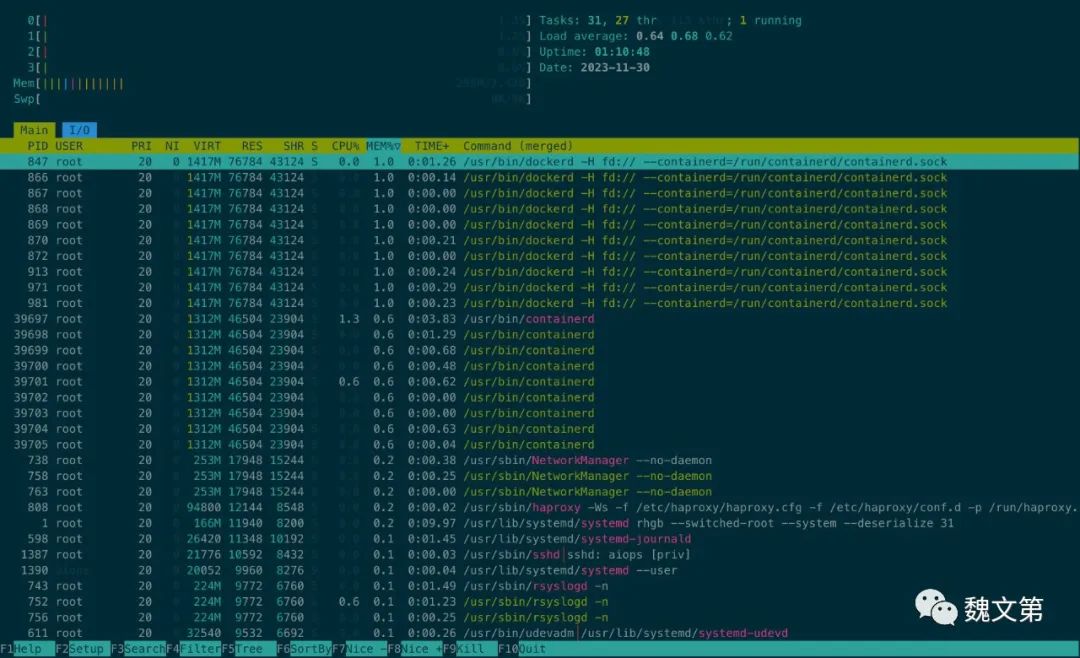

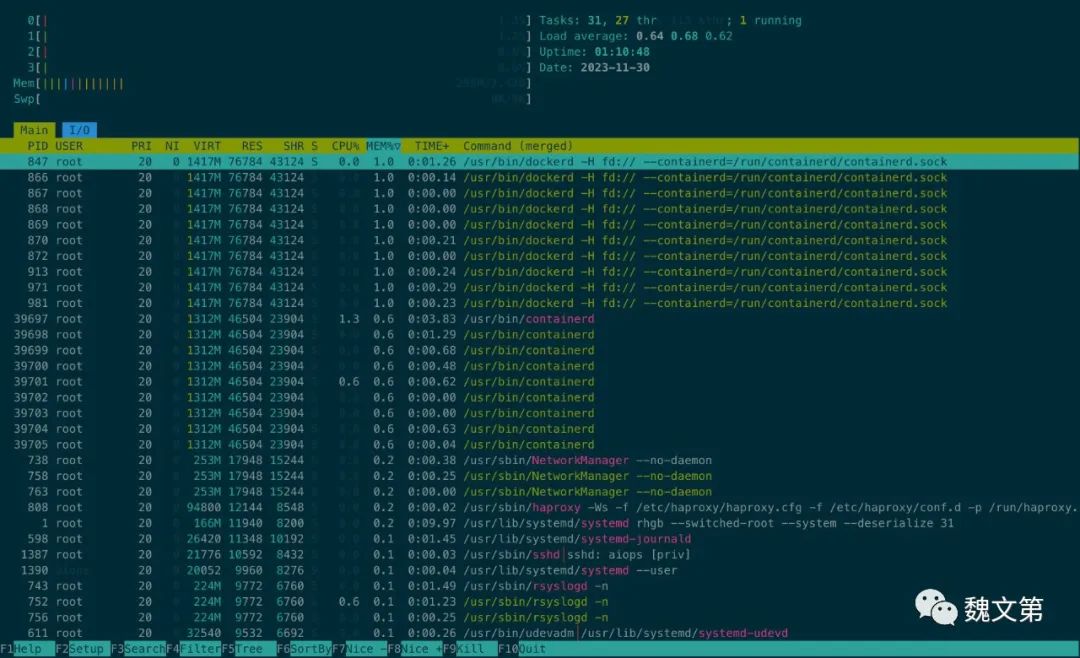

本文介绍如何在 Linux 中使用 htop 命令。

2023-12-04 14:45:28 441

441

和 GPU 不同, FPGA 不需要在内存和编程之间切换,这使得存储和检索数据的过程更高效。FPGA 架构灵活性更高,因此您可以自定义您希望 FPGA 用于特定任务的电源。

这种灵活性有助于将能耗极高的任务从

2023-06-28 18:18:57

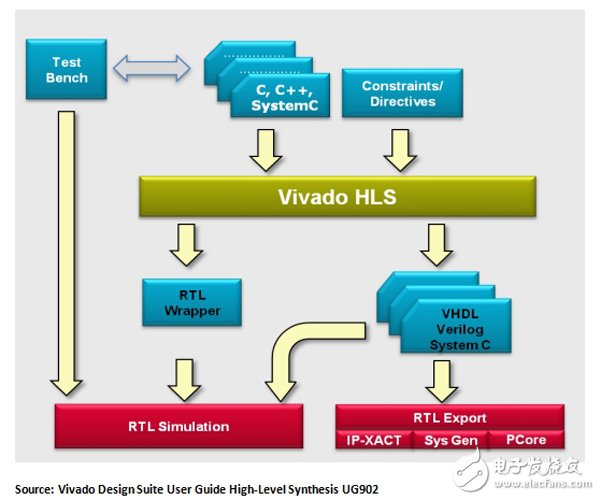

简化了 FPGA 的开发流程,使画家的画笔更好用更易用。HLS (High level Synthesis,高层次综合)工具给“画家”提供了新的画笔——可以直接用抽象级别更高的c/c++进行硬件编程

2018-08-13 09:31:45

,大大简化了 FPGA 的开发流程,使画家的画笔更好用更易用。HLS (High level Synthesis,高层次综合)工具给“画家”提供了新的画笔——可以直接用抽象级别更高的c/c++进行硬件

2018-08-10 09:16:48

嗨, 我是National Instruments公司的应用工程师。如您所知,我们在许多产品中使用您的FPGA芯片组,最近我们收到了一位非常关注安全问题的客户提出的问题。众所周知,使用FPGA芯片组

2020-03-09 09:56:44

重要组成部分,所以我们将重点介绍Vitis HLS。LUT 或 SICELUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!BRAM 或 Block

2022-09-07 15:21:54

BOARD EVAL FPGA BLACKFIN EXTENDR

2023-03-30 12:06:40

MODULE USB-TO-FPGA TRAINING TOOL

2023-04-06 11:27:13

MODULE USB-TO-FPGA TOOL W/MANUAL

2023-04-06 11:27:29

MODULE USB-TO-FPGA SPARTAN3

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN 3A

2023-04-06 11:27:11

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

)对正点原子FPGA感兴趣的同学可以加群讨论:8767449005)关注正点原子公众号,获取最新资料第一章HLS简介为了尽快把新产品推向市场,数字系统的设计者需要考虑如何加速设计开发的周期。设计加速

2020-10-10 16:44:42

为什么要在显示器应用中使用FPGA?一种Spartan-3E显示器解决方案板

2021-06-04 06:47:39

本帖最后由 eehome 于 2013-1-5 09:56 编辑

《成为Xilinx FPGA设计专家(基础篇) 》是一朋友查阅各方面资料后加以梳理后整理出来的电子书。我在这里帮她宣传一下...

2012-07-26 22:15:57

HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。LUT 或 SICELUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!BRAM 或

2022-09-09 16:45:27

FPGA入门嵌入式块RAM使用为FIOF(First In First Out)单时钟FIOF、双时钟FIOF(普通双时钟和混合宽度双时钟)由于单时钟FIOF只有一个时钟信号,所以可以在FPGA内部中使用单时钟FIOF用以其他模块数据的缓存。...

2021-12-17 07:59:18

国外的融合技术专家展示了一项基于FPGA的数据采集系统,用于合成孔径成像技术。采用了Xilinx ISE设计软件,支持ARM AMBA AXI4接口。文风犀利,观点新颖,FPGA中使用ARM及AMBA总线中不可多得的资料在赛灵思FPGA中使用ARM及AMBA总线[hide][/hide]

2012-03-01 15:48:17

FPGA的HLS案例开发|基于Kintex-7、Zynq-7045_7100开发板前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

你好xilinx用户,我正在使用FPGA实现人工神经网络。我想知道如何在FPGA中使用0.784,1.768..etc等数字。表示这些数字的方法是什么。以上来自于谷歌翻译以下为原文hello

2019-03-04 13:38:31

美好的一天!我想知道如何在FPGA上有持久的价值,我的意思是当我修改它的值时,当块再次运行时,值不会被改变?在Matlab中通过定义一个像:persistent u的值,它会完成,但VHDL怎么样

2019-02-20 11:17:46

嗨,我是Xilinx FPGA的新手。我该如何在FPGA中实现实时时钟或时间和日期计数器?Xilinx是否为Artix 7提供任何RTC核心或IP?非常感谢您的建议。

2020-05-22 12:41:35

大家好!我想知道如何在FPGA中使用VHDL实现过零检测器。所以我想实现一个数字常数小数鉴别器。 firt部分提供了双极性信号,但我想知道如何在vhdl中实现过零检测器。感谢您的帮助!以上来自于谷歌

2019-01-29 08:16:40

大家好我正在尝试在斯巴达6上开发UDP / IP堆栈。该FPGA将与外部PHY(DP83640)通信。我已经添加了TEMAC v4.4核心。所以我的问题是: - 如何在FPGA和PHY之间执行自动

2019-11-05 09:46:20

如何在FPGA应用程序中将固定点称为重要的?以上来自于谷歌翻译以下为原文How fixed point can be called important in FPGA Applications?

2019-02-18 13:24:43

]命令失败:'E9'不是有效的站点或包引脚名称。 [ “C:/lab/test/test.srcs/constrs_1/new/demo.xdc”:5]如何在FPGA设计中使用E9引脚来控制NOR闪存?谢谢。

2020-06-10 16:52:14

你好!正如我在标题中提出的那样,希望大家可以讨论如何在FPGA设计中测试数字IF信号功率。以上来自于谷歌翻译以下为原文Hello! as what I put forward

2019-01-09 10:00:59

嗨〜 如何在HLS 14.3中编写pow功能? HLS 14.3不支持exp和pow功能。我在我的代码中写了“#include math.h”。但是,它不起作用。 另外,我想知道C代码中

2019-03-05 13:40:09

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。那么该如何在低端FPGA中实现DPA的功能呢?

2021-04-08 06:47:08

如何在视频监控系统中使用FPGA进行视频处理?

2021-06-07 06:12:39

有没有人知道教程的一些链接,如何在设计套件中使用sumulink的指南?我希望找到一个简单的101教程,它将引导我在Simulink中创建一个简单的项目(包括Xilinx Sys gen工具箱组件

2019-03-21 16:42:18

如何使用NI LabVIEW FPGA来设计和自定义您的射频仪器?软件设计仪器为您的测试系统带来了哪些好处?

2021-05-24 06:26:34

你好,我想使用Vivado HLS开发FPGA比特流并将其加载到Pynqpython模块中或使用Linux使用C ++进行ARM加载。到目前为止,我能够生成FPGA比特流文件,但是知道如何集成它或与Pynq通信。那有什么教程吗?

2019-09-30 10:50:36

开拓者FPGA DEVB_121X160MM 6~24V

2023-03-28 13:06:25

相比,能够为通信和多媒体应用提供高达10倍速的更高的设计和验证能力。Synphony HLS为ASIC 和 FPGA的应用、架构和快速原型生成最优化的RTL。Synphony HLS解决方案架构图

2019-08-13 08:21:49

您是否曾想在您的FPGA设计中使用先进的视频压缩技术,却发现实现起来太过复杂?那么如何满足视频压缩的需求?

2021-04-08 06:43:18

和生成比特流以对FPGA进行编程4 - 将比特流导入并阻塞到SDK中,基于此生成板级支持包(BSP)并与Zedboard连接。顺便说一下,SDK的目标是成为我在Vivado HLS中的测试平台吗?即在计算机中观察Zedboard产生的结果是否为例外情况。

2020-03-24 08:37:03

对大家有所帮助,当然更加希望Xilinx? FPGA工程师/爱好者能跟我们一起来探讨学习!《成为Xilinx FPGA设计专家》这本电子书,计划分为3大部分:基础篇、提升篇、高级篇。 当然这里讲

2014-11-05 13:56:42

设计专家》这本电子书,计划分为3大部分:基础篇、提升篇、高级篇。 当然这里讲的就是《成为Xilinx FPGA设计专家》(基础篇)。本电子书主要论述了等相关内容。本电子书旨在解决工程师日常设计中所

2014-11-03 17:15:51

新起点FPGA DEVB_90X128MM 6~24V

2023-03-28 13:06:25

的问题是:所有3种类型都可以在FPGA Spartan 6中使用,如果它们中的任何一种都有利于以更简单的方式实现。谢谢您的帮助。

2019-08-05 07:38:33

您好我有一个关于vivado hls的问题。RTL是否来自xivix FPGA的vivado hls onyl?我们可以在Design Compiler上使用它进行综合吗?谢谢

2020-04-13 09:12:32

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

2020-03-25 09:04:39

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包软件。提供了一些基础的函数库以及常用的控制函数模块,配合

2022-05-19 09:16:05

概述EasyGo FPGA Solver是EasyGo开发的专门部署在FPGA 硬件上的解算器软件。根据不同的应用需求,会有不同的FPGA Solver 选择

2022-05-19 09:21:43

EP4CE10F17C8N,Cyclone IV FPGA设备,INTEL/ALTERAEP4CE10F17C8N,Cyclone IV FPGA设备,INTEL

2023-02-20 17:00:57

什么是FPGA?FPGA是什么意思,本内容详加描述了FPGA的相关知识包括FPGA配置模式,PPGA特点及应用

2011-12-07 13:39:00 79099

79099 解决本本黑屏问题 专家教你DIY

问题:最近我的笔记本在以下情况下特别容易出现黑屏(不是纯黑,屏上较亮的还以隐约看

2010-01-25 14:45:32 633

633 投影屏幕选购让专家教你三招

1、不同应用选择不同材质 表面上看,投影屏幕的外观颜色都是白的,没有什么差别,其实不同材质

2010-02-11 09:29:52 424

424 电子发烧友网核心提示 :在嵌入式系统中使用FPGA时会经常出现以下常见问题,如在嵌入式设计中,怎样使用FPGA、在嵌入式设计中,怎样采用FPGA进行设计来降低风险等。今天电子发烧友

2012-10-17 13:38:35 906

906 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 介绍如何设计HLS IP,并且在IP Integrator中使用它来作一个设计——这里生成两个HLS blocks的IP,并且在一个FFT(Xilinx IP)的设计中使用他们,最终使用RTL

2017-02-07 17:59:29 4179

4179

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

通常基于传统处理器的C是串行执行,本文介绍Xilinx Vivado-HLS基于FPGA与传统处理器对C编译比较,差别。对传统软件工程师看来C是串行执行,本文将有助于软件工程师理解

2017-11-18 12:23:09 2377

2377

HLS,高层综合)。这个工具直接使用C、C++或SystemC 开发的高层描述来综合数字硬件,这样就不再需要人工做出用于硬件的设计,像是VHDL 或Verilog 这样的文件,而是由HLS 工具来做这个事情。

2018-06-04 01:43:00 7171

7171

Achronix的Speedcore系列eFPGA可得到Catapult HLS的全面支持。

Catapult HLS为FPGA流程提供集成化设计与开发环境,率先支持5G无线应用。

2018-08-30 10:09:32 7368

7368 中断作为硬件与软件握手和同步的手段而被广泛使用,可用于表示硬件进程的完成或软件执行过程中的请求。Gx3500 & GX3700/GX3700e 用户可编程 FPGA 板卡都支持这一特性,并向 FPGA 设计者开放专用的硬件中断引脚;软件方面,三个 API 函数用于中断管理和设置。

2018-08-31 08:00:00 10

10 作为集成电路设计领域现场可编程门阵列 (FPGA) 技术的创造者之一,赛灵思一直积极推广高层次综合 (HLS) 技术,通过这种能够解读所需行为的自动化设计流程打造出可实现此类行为的硬件。赛灵思刚刚推出了一本专著,清晰介绍了如何使用 HLS 技术来创建优化的硬件设计。

2018-11-10 11:01:05 2750

2750 亚马逊网络服务公司的Gadi Hutt于2018年1月9日在法兰克福举行了Xilinx开发者论坛的开幕主题演讲.Gadi解释了Amazon EC2 F1实例的基础知识,如何在AWS云中加速Xilinx FPGA

2018-11-23 06:15:00 2524

2524 Xilinx FPGA是支持OpenStack的第一个(也是目前唯一的)FPGA。

该视频快速介绍了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展台上运行每个演示,并使用OpenStack进行配置和管理。

2018-11-23 06:14:00 3322

3322 了解如何在UltraScale +设计中包含新的UltraRAM模块。

该视频演示了如何在UltraScale + FPGA和MPSoC中使用UltraRAM,包括新的Xilinx参数化宏(XPM)工具。

2018-11-22 05:50:00 7646

7646 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。然而,这种方法最受诟病的是对性能的牺牲。在复杂的 FPGA 设计上实现高性能,往往需要手动优化 RTL 代码,这也意味着

2018-12-16 11:19:28 1435

1435

用软件从 C 转化来的 RTL 代码其实并不好理解。今天我们就来谈谈,如何在不改变 RTL 代码的情况下,提升设计性能。 本项目所需应用与工具:赛灵思HLS、Plunify Cloud 以及 InTime。 前言 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。

2019-09-15 11:56:00 265

265 本文档介绍如何在Spartan®6 FPGA中使用GTP收发器。•spartan-6 FPGA GTP收发器简称为GTP收发器。

•gtpa1_dual是实例化原语的名称,它实例化一组

2019-02-15 14:42:47 27

27 展示了赛灵思 SDAccel 开发环境的运行情况,并演示了一个软件程序员是如何在OpenCL中捕获一个应用,并利用 FPGA 对其完成加速的。整个过程中该程序员完全不需要是一个FPGA专家或对赛灵思器件设计流程特别熟悉即可独立完成。

2019-08-01 11:03:25 1528

1528 接着开始正文。据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,intel也快马加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入门门槛(不用编写

2019-07-31 09:45:17 6232

6232

在本教程中,我们将来聊一聊有关如何在 Vitis HLS 中使用 AXI4-Lite 接口创建定制 IP 的基础知识。

2020-09-13 10:04:19 5961

5961

一:fifo是什么 FIFO的完整英文拼写为FirstIn First Out,即先进先出。FPGA或者ASIC中使用到的FIFO一般指的是对数据的存储具有先进先出特性的一个存储器,常被用于数据

2021-03-12 16:30:48 2796

2796

FPGA的布局布线软件向来跑得很慢。事实上,FPGA供应商已经花了很大的精力使其设计软件在多核处理器上运行得更快。

2022-05-25 09:50:10 959

959 需要门级验证:FPGA 和 ASIC 一样需要设计级验证。但是,FPGA 在门级不是细粒度的,因此它们不需要门级验证。您将每个门都放置在 ASIC 设计中,因此您需要验证每个门。

2022-06-20 16:13:05 2184

2184

您是否想创建自己带有 AXI4-Lite 接口的 IP 却感觉无从着手?本文将为您讲解有关如何在 Vitis HLS 中使用 C 语言代码创建 AXI4-Lite 接口的基础知识。

2022-07-08 09:40:43 1232

1232 HLS的FPGA开发方法是只抽象出可以在C/C++环境中轻松表达的应用部分。通过使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

2022-08-02 09:43:05 579

579

电子发烧友网站提供《ThunderGP:基于HLS的FPGA图形处理框架.zip》资料免费下载

2022-10-27 16:49:59 0

0 电子发烧友网站提供《如何在Arduino中使用LDR.zip》资料免费下载

2022-10-31 09:50:41 0

0 1、HLS简介 HLS(High-Level Synthesis)高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境

2022-12-02 12:30:02 2571

2571 HLS (high-level synthesis)称为高级综合, 它的主要功能是用 C/C++为 FPGA开发 算法。这将提升FPGA 算法开发的生产力。 Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 电子发烧友网站提供《如何使用HLS加速FPGA上的FIR滤波器.zip》资料免费下载

2023-06-14 15:28:49 1

1 FPGA IP核(Intellectual Property core)是指在可编程逻辑器件(Field-Programmable Gate Array,FPGA)中使用的可复用的设计模块或功能片段。它们是预先编写好的硬件设计代码,可以在FPGA芯片上实现特定的功能。

2023-07-03 17:13:28 4100

4100 本篇博文旨在演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS IP,然后在 Vitis 中使用该函数作为平台来运行嵌入式应用。

2023-08-01 10:18:08 307

307

本篇博客介绍 VVAS 框架所支持调用的 H/W(HLS) 内核。 H/W 内核指的是使用 HLS 工具生成的在 FPGA 部分执行的硬件功能模块。

2023-08-04 11:00:43 335

335

Vitis™ HLS 2023.1 支持新的 L1 库向导,本文将讲解如何下载 L1 库、查看所有可用功能以及如何在 Vitis HLS GUI 中使用库函数。

2023-08-16 10:26:16 546

546

电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

0 Dimitar Panayotov 在 2023 年 QA Challenge Accepted 大会 上分享了他如何在测试中使用 ChatGPT。

2024-02-20 13:57:01 280

280

电子发烧友App

电子发烧友App

评论