Vivado起航

大家好,欢迎Vivado的一个快速演示,它是xilinx新的设计套件,应用到7系列和以上的系列器件。

开始

当你打开Vivado IDE集成设计环境的时候,你首先看到的是开始页,在右边是文档,方法指导手册和指引。

左边是向导,他指导你创建新的工程,包括如何从ise和Planahead工具迁移到vivado。

快速集成设计环境概要

创建一个新的工程后,Vivado IDE集成设计环境包含工程总结标签就打开了,这个标签给你有关你的工程信息,比如现在的状态,编译流程,设置,错误和警告信息。

这个顶层菜单和工具条给你访问到通用的功能。

你工程的设计源被列在源视图里。

左边的这个部分叫做流程导航器。这是你控制和分析Vivado能力的地方,在后面的演示里,我们会一步一步来讨论。在Vivado集成设计环境里,你能管理源文件,实现流程和所有的设计分析。

在Vivado里,有一个新的功能是IP装配,也叫做IP集成。这个演示的剩下部分会显示如何快速和容易地使用IP集成来创建一个复杂的子系统。

创造IP集成器设计演示

IP 集成器是一个图形化设计工具,它在复杂的IP block(模块)之间做接口级的连接。然而,因为IP集成器紧紧地连接到了Vivado IDE,设计者能在图形化环境和Tcl互动之间切换。

我们开始运行一个简单的MicroBlaze软处理器系统脚本。

当这个脚本在运行的时候,你能看见独立的IP 模块放置在模块框图里,还有在这些模块之间的接口级网线连接。

我要加一些模块到这个设计里,开始,打开这个MicoBlaze配置对话框,同时使能调试接口和AXI4数据接口。 通过右击这个图,IP就能被加到这个设计里,你也能使用查找对话框快速地来找到这些接口。这个IP可以来自第三方,也可以是你自己的。一个调试模块被加上了,也连接到了处理器。注意开始很深的绿色线标记表明可能的连接,很深的蓝色线表示这是个接口级的连接。这个连接由多个相关的信号组成。在IP打包进程中,这是通过IP-XACT自动地创建。

现在,一个AXI GPIO外设会被连接到处理器,来自这个GPIO的输出信号会作为外部的信号。

为了演示接口级连接的强大功能,我会在MicroBlaze处理器展开这个AXI接口。所有要求的AXI4信号需要用单一连接连接到GPIO的外设。当这些接口级的连接创建时,互联的DRC(设计规则检查)也被实时地运行。

IP集成器支持任意的层次级。组成存储系统的5个IP模块现在会移动成自己的层次。这个白色盒子显示了你的层次。IP整合器支持任意的设计层次级。

IP集成器在互联的IP模块之间支持全部的参数传播,确保结构化设计的正确性。一旦一个设计完成,Verilog或VHDL从这个框图中就被产生。这整个IP框图,或者任意的层次级能被快速地封装并添加到Vivado的IP 目录中。使系统级的IP模块可以被重用。

供货情况

Vivado 设计套件 2012.1 版本现已作为早期试用计划的一部分推出。客户可联系所在地的赛灵思代表。今夏早些时候将公开发布 2012.2 版本,今年晚些时候还将推出 WebPACK。目前采用 ISE 设计套件版本的客户将免费获得最新 Vivado 设计套件版本和IDS。赛灵思将继续为针对 7 系列及早期产品设计的客户提供 ISE 设计套件支持。如需更多信息,敬请访问以下网址:www.xilinx.com/cn/design-tools。

关于赛灵思

赛灵思致力于开发All Programmable的技术和器件,超越了硬件进入软件,超越了数字进入模拟,超越了单芯片进入了3D堆叠芯片。这些行业领先的器件与其新一代设计环境和IP相结合,可以满足从可编程逻辑到可编程系统集成领域更广泛的客户需求。如需了解更多信息,请访问赛灵思公司中文网站:www.xilinx.com/cn.

Vivado IP集成器

- Vivado(64979)

- IP集成器(5763)

相关推荐

赛灵思Vivado设计套件加速集成和系统级设计,继续领先一代

本在生产力方面进行了两大改进。Vivado设计套件2013.1版本新增了一款以IP为中心的设计环境,用以加速系统集成;而其提供的一套完整数据库,则可加速C/C++系统级设计和高层次综合(HLS)。

2013-04-08 15:08:54 902

902

902

9022014.1 Windows 8.1 MIG IP生成器无法运行

在win8.1 pc上使用Vivado 2014.1,MIG IP生成器在启动时收到Windows错误。相同的安装文件已加载到win7 pc上,MIG IP生成器运行正常。在Win8.1机器上,我

2018-12-07 11:18:46

Vivado 2013.1和Zynq需要及早访问Vivado IP集成商是什么意思?

关于Zynq的Vivado 2013.1发行说明说:“需要及早访问Vivado IP集成商”。这是什么意思?它是否真的支持Zynq开箱即用?提前致谢。以上来自于谷歌翻译以下为原文Vivado

2018-12-04 11:00:58

Vivado IP交付

在模拟模型方面,Vivado提供的IP似乎有一些根本性的变化。在将工作设计从ISE 14.4转换为Vivado 2013.2之后,然后按照建议的方式升级大部分Xilinx IP,例如基本乘法器,除法

2019-02-26 10:42:23

Vivado IP核锁定的解决办法分享

发生IP核锁定,一般是Vivado版本不同导致的,下面介绍几种方法: 1 常用的方法 1)生成IP核的状态报告 Report -》 Report IP Status 2)点击

2021-01-08 17:12:52

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用

)配合优化综合的视频库和Vivado IP集成器,为一个特定的视频应用打造一个定制化的加速器。该设计流程可以在兼具高性能和低功耗的条件下快速地实现许多计算机视觉算法。此设计流程还可以让设计人员能够在

2013-12-30 16:09:34

Vivado生成IP核

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

Vivado系统生成器中黑盒的问题

嗨,我正在使用Vivado和系统生成器2015.4,以及Matlab 2015b。我正在运行Windows 7.每当我尝试使用.vhd文件或第三方文件在Sys Gen中进行模拟时,我会得到以下tcl

2020-04-13 09:28:58

vivado带ip核的工程封装

请教一下,vivado怎么把带ip核的工程进行封装,保证代码不可见,可以通过端口调用。我尝试了以下方法,ippackage,如果要在另一个程序里调用,也要提供源代码;另一个方法是将网表文件edf文件与端口声明结合,这种方法只能实现不带ip核的封装

2017-07-14 09:18:30

vivado有哪几种常用IP核?如何去调用它们

vivado三种常用IP核的调用当前使用版本为vivado 2018.3vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点

2021-07-29 06:07:16

关于Vivado内部IP检查点的问题

我对Vivado内部的IP检查点有疑问。当我在Vivado中启用IP内核的检查点时,我可以在Design Runs窗口中看到此IP的“synth”和“impl”。对于IP的“合成”,我可以理解这是

2019-03-08 13:30:52

可以使用Vivado安装Xilinx系统生成器吗

大家好我可以在Matlabwith Vivado上安装Xilinxsystem生成器吗?有了ISE,有一个应用程序调用System Generator Matlab Configuration

2018-12-27 10:57:02

基于 FPGA vivado 2017.2 的74系列IP封装

基于 FPGA vivado 2017.2 的74系列IP封装实验指导一、实验目的掌握封装IP的两种方式:GUI方式以及Tcl方式二、实验内容 本实验指导以74LS00 IP封装为例,介绍了两种封装

2017-12-20 10:23:11

如何使用Vivado IP Block Design?

的是如何使用它或将其转移到普通的Vivado项目,这样我就可以应用测试平台并对其进行测试。从我的角度来看,IP块设计是加载IP和进行互连的好方法。但是,使用它还需要其他步骤。我错了吗?我花了几个星期的时间尝试将

2020-03-20 08:52:30

嵌入式处理器硬件设计

Vivado设计套件用户指南:嵌入式处理器硬件设计 讨论使用Vivado™IP集成器和Xilinx软件开发套件(SDK),使用Zynq®-7000 All Programmable(AP)SoC

2017-11-15 10:34:10

怎么在Vivado HLS中生成IP核?

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

怎么在vivado HLS中创建一个IP

你好我正在尝试在vivado HLS中创建一个IP,然后在vivado中使用它每次我运行Export RTL我收到了这个警告警告:[Common 17-204]您的XILINX环境变量未定义。您将

2020-04-03 08:48:23

是否可以在不升级IP内核的情况下通过较新版本的Vivado打开旧版Vivado?

你好是否可以在不升级IP内核的情况下,通过较新版本的Vivado打开旧版Vivado?最好的祝福以上来自于谷歌翻译以下为原文HiIs it possible to open the older

2018-12-28 10:30:06

是否有任何方法可以更改Vivado 2013.2中的默认IP目录?

我使用的是Vivado 2013.2。就我而言,我不喜欢Vivado提供的喜剧。我为我的项目构建了自己的hirachey,IP核心文件夹位于另一个位置,而不是默认的“src / ip”。我只是想知道

2019-04-17 09:27:52

测试模式生成器许可证无效

嗨,视频测试模式生成器IP模块需要一个免费许可证,我已从Xilinx下载,添加到我的许可证文件中,并加载到Vivado for Ubuntu。 TheLicense Manager看到它,但是当我

2019-01-02 14:34:16

玩转Zynq连载21——Vivado中IP核的移植

`玩转Zynq连载21——Vivado中IP核的移植更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接:https://pan.baidu.com

2019-09-04 10:06:45

系统生成器的版本与Vivado不兼容

你好,我有一块ZC-702板,并使用套件附带的节点锁定licese安装了Vivado。我看到Vivado设计版15.2包含系统生成器。我成功安装了Vivado。但是,我无法选择( check)安装

2018-12-17 11:49:00

获得IP核评估许可,无法在Vivado中看到IP

我已获得Xilinx HDMI IP内核的评估许可证,并已将其加载到许可证管理器中。我的IP经理似乎缺少实际的IP本身。我已经检查了计算机上的Xilinx文件夹,但找不到任何文件。我找到了名为

2019-01-02 15:02:41

请教大神帮忙解决microblaze挂接axi_qual_spi模块,主模式信息发不出去的问题?

我最近在实验microblaze挂接spi核的问题,遇到很多问题,请求大神帮忙看看哪有问题?具体描述如下:1、首先我在vivado IP集成器中设计了microblaze软核挂接spi模块,时钟

2017-09-27 18:07:13

请问如何在Vivado项目中实例化hdl系统生成器输出的多个实例》

嗨,如何在Vivado项目中实例化hdl系统生成器输出的多个实例?在vivado项目中很容易实例化一个hdl系统生成器输出。当我想将另一个实例实例化到同一个项目时,我在合成状态下面临一些错误。最好的祝福

2020-07-31 10:38:59

Vivado环境下如何在IP Integrator中正确使用HLS IP

testbench来验证设计。 Integrate带有Xilinx IP Block的 HLS IP 这里展示了在IP Integrator中,如何将两个HLS IP blocks跟Xilinx IP FFT结合在一起 ,并且在Vivado中验证设计。

2017-02-07 17:59:29 4179

4179

4179

4179

基于vivado的fir ip核的重采样设计与实现

本文基于xilinx 的IP核设计,源于音频下采样这一需求。 创建vivado工程 1. 首先打开vivado,创建一个新的project(勾选create project subdirectory

2017-02-08 02:25:09 3716

3716

3716

3716

Vivado IP Package自定义总线Interface

的操作中只能使用Vivado自带的interface。像上面这个IP中的HDMI接口,Vivado就没有集成合适的interface。分立的port会使得框图设计变的比较凌乱,尤其是像HDMI这样既有

2017-02-08 11:50:11 3289

3289

3289

3289

Xilinx Vivado的使用详细介绍(3):使用IP核

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-02-08 13:08:11 1235

1235

1235

1235

Xilinx推出Vivado设计套件HLx版 为主流系统及平台设计人员带来超高生产力

HLx 版本均包括带有 C/C++ 库的 Vivado 高层次综合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE™ IP 子系统以及完整的 Vivado 实现工具套件,使主流用户能够方便地采用生产力最高、最

2017-02-08 19:35:06 386

386

386

386Xilinx Vivado 2015.3 运用 IP子系统将设计提升至新高

IP子系统集成了多达80个不同的IP 核、软件驱动程序、设计实例和测试平台,可大幅提高生产力 赛灵思发布 Vivado Design Suite2015.3版本。这一新版本通过支持设计团队利用

2017-02-09 01:15:42 225

225

225

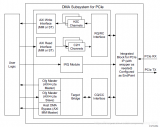

225Northwest Logic支持Xilinx IP集成器工具流

Northwest Logic 的 DMA 内核现已支持 Vivado 设计套件中的 IP 集成器工具流。 IP 集成器流可为客户简化将基于 AMBA® AXI4 接口的 IP

2017-02-09 08:12:36 319

319

319

319

了解Vivado中IP核的原理与应用

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-11-15 11:19:14 8390

8390

8390

8390ucos iii在zynq上的移植

本教程介绍了如何使用μC/ OS BSP建立在ZYNQ基本应用程序®使用Vivado -7000 ™ IDE和赛灵思® SDK。在本教程中,您将使用Vivado IP集成器配置ZYNQ处理器系统以及

2017-11-17 15:06:01 8001

8001

8001

8001如何优化赛灵思内核以便在CPRI远程无线电头端设计中使用Vivado IPI

新型基于FPGA的设计使用IP核的数量和种类日趋繁多。Vivado®设计套件中的IP集成器 (IPI)工具和赛灵思通信IP让设计人员能够更加轻松快速地将IP模块连接在一起。 为了更好地阐明IPI方法的强大之处,我们以远程无线电头端(RRH)为例。RRH位于天线附近,构成蜂窝通信网络的一部分。

2017-11-18 01:25:01 1933

1933

1933

1933在Vivado下利用Tcl实现IP的高效管理

在Vivado下,有两种方式管理IP。一种是创建FPGA工程之后,在当前工程中选中IP Catalog,生成所需IP,这时相应的IP会被自动添加到当前工程中;另一种是利用Manage IP,创建独立

2017-11-18 04:22:58 5473

5473

5473

5473Xilinx CORE生成器IP列表名称及说明详解

本页包含通过LabVIEW FPGA模块可用的Xilinx CORE生成器IP的列表。LabVIEW通过Xilinx IP节点实现该IP。 下列IP名称和说明来自于Xilinx数据表。LabVIEW

2017-11-18 05:55:51 4465

4465

4465

4465集成Xilinx内核生成器IP至FPGA VI详细步骤

LabVIEW使用IP集成节点方便的整合Xilinx内核生成IP至FPGA VI。按照下列步骤添加Xilinx内核生成器IP至FPGA VI。 1、在支持的FPGA终端下新建一个空白VI,并显示VI

2017-11-18 05:56:22 1746

1746

1746

1746了解Vivado设计套件集成能力的九大理由分析

理由一:突破器件密度极限:在单个器件中更快速集成更多功能;理由二:Vivado以可预测的结果提供稳健可靠的性能和低功耗;理由三:Vivado设计套件提供了无与伦比的运行时间和存储器利用率;理由四:使用Vivado高层次综合生成基于C语言的IP。

2017-11-22 08:15:19 1421

1421

1421

1421赛灵思Vivado开发套件与IP核的原理作用分析

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-11-28 15:49:58 1766

1766

1766

1766Vivado将模块封装为IP的方法介绍

在给别人用自己的工程时可以封装IP,Vivado用封装IP的工具,可以得到像xilinx的ip一样的可以配置参数的IP核,但是用其他工程调用后发现还是能看到源文件,如何将工程源文件加密,暂时没有找到方法,如果知道还请赐教。

2018-06-26 11:33:00 7425

7425

7425

7425在IP集成器中调试AXI接口有哪些优势?

用户可以使用IP集成器连接IP模块创建复杂的系统设计。通过接口构建基于模块的设计,一般情况下接口包含多个总线和大量的信号线。因此,为了方便在硬件上调试那些包含大量接口的设计,就需要验证设计的接口连接。

2018-04-18 15:28:24 2978

2978

2978

2978

vivado调用IP核详细介绍

大家好,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。 首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 36233

36233

36233

36233赛灵思推出Vivado设计套件HLx版本,助力SoC和FPGA以及打造可复用的平台

、HL 设计版本和 HL WebPACK 版本。所有 HLx 版本均包括带有 C/C++ 库的 Vivado 高层次综合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE IP

2018-08-17 11:43:00 2677

2677

2677

2677赛灵思Vivado设计套件推出2013.1版本,提供IP 集成器和高层次综合功能

FPGA器件中创建高度集成的、复杂的设计,赛灵思推出了Vivado IP Integrator(IPI)早期试用版本。Vivado IPI可加速RTL、

2018-09-25 09:18:01 275

275

275

275如何将Vivado IP和第三方综合工具配合使用

观看视频,学习如何将 Vivado IP 和第三方综合工具配合使用。 此视频将通过一个设计实例引导您完成创建自定义 IP 的步骤;用第三方综合工具IP黑盒子来审查所需 IP 输出;整合 Vivado IP 网表和第三方综合工具网表的两个方法,即 “网表项目模式” 和 “非项目 Tcl 脚本模式”。

2018-11-21 06:34:00 4811

4811

4811

4811如何让Vivado IP Integrator和Amazon F1开发套件进行协同使用

欢迎阅读本快速视频,我将解释如何使用Vivado IP Integrator流程与Amazon F1硬件开发套件或HDK配合使用

2018-11-20 06:35:00 2212

2212

2212

2212如何在Vivado Design Suite 中进行IP加密

此视频概述了Vivado Design Suite中的IP加密。

它涵盖了IP加密工具流程,如何准备加密IP以及如何在Vivado中运行加密工具。

2018-11-20 06:34:00 5948

5948

5948

5948用于系统生成器中Vivado HLS IP模块介绍

了解如何生成Vivado HLS IP模块,以便在System Generator For DSP中使用。

2018-11-20 06:08:00 2940

2940

2940

2940如何使用Vivado Logic Analyzer与逻辑调试IP进行交互

了解Vivado中的Logic Debug功能,如何将逻辑调试IP添加到设计中,以及如何使用Vivado Logic Analyzer与逻辑调试IP进行交互。

2018-11-30 06:22:00 3107

3107

3107

3107如何使用Vivado Design Suite IP Integrator的调试AXI接口

了解如何使用Vivado Design Suite IP Integrator有效地调试AXI接口。

本视频介绍了如何使用该工具的好处,所需的调试步骤和演示。

2018-11-29 06:00:00 3680

3680

3680

3680如何使用Vivado IP Integrator组装具有多个时钟域的设计

该视频演示了如何使用Vivado IP Integrator组装具有多个时钟域的设计。

它显示了Vivado中的设计规则检查和功能如何帮助用户自动执行此流程。

2018-11-27 07:40:00 3539

3539

3539

3539调用Vivado IP核的方法

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26:38 4468

4468

4468

4468FPGA实现基于Vivado的BRAM IP核的使用

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

9496

9496

9496如何在vivado创建新工程上使用IP集成器创建块设计

本文介绍如何在 vivado 开发教程(一) 创建新工程 的基础上, 使用IP集成器, 创建块设计。

2022-02-08 10:47:39 2090

2090

2090

2090

Vivado中xilinx_BRAM IP核使用

Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5种类型:Single-port RAM 单端口RAM,Simple Dual-port RAM 简单双端口RAM(A写数据B读数据)

2021-03-10 06:15:56 19

19

19

19VCS独立仿真Vivado IP核的一些方法总结

前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有

2021-03-22 10:31:16 3409

3409

3409

3409关于Vivado三种常用IP核的调用详细解析

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。

2021-04-27 15:45:12 22634

22634

22634

22634

如何导出IP以供在Vivado Design Suite中使用?

以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。 本篇博文将分为 3 个部分: 1. 从 Vitis HLS 导出 IP。 2.

2021-04-26 17:32:26 3506

3506

3506

3506

基于VIVADO的PCIE IP的使用

基于VIVADO的PCIE IP的使用 项目简述 上一篇内容我们已经对PCIE协议进行了粗略的讲解。那么不明白具体的PCIE协议,我们就不能在FPGA中使用PCIE来进行高速数据传输了吗?答案是否

2021-08-09 16:22:10 10199

10199

10199

10199

Vivado BDC (Block Design Container)怎么用

谈到BDC(Block DesignContainer)就不得不提IPI(IP Integrator)。IPI常被翻译为“IP集成器”,也是有道理的。它提供了一种“图形化+模块化”的设计方式。若用过

2021-11-09 09:43:17 3253

3253

3253

3253使用VIvado封装自定IP并使用IP创建工程

在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之后的设计中继续使用此IP。因此本次详细介绍使用VIvado来封装自己的IP,并使用IP创建工程。

2022-04-21 08:58:05 4579

4579

4579

4579在Vivado中创建基于IP集成器(IP Integrator)的设计

Zynq UltraScale+ RFSoC 是业界首款单芯片自适应无线电平台,在一款芯片内集成射频直采数据转换器、单芯片软决策前向纠错核(SD-FEC)、FPGA逻辑、完整的ARM处理器子系统和高速收发器等。

2022-06-08 16:07:54 2307

2307

2307

2307如何导出IP以供在 Vivado Design Suite 中使用

在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

2022-07-08 09:34:00 2023

2023

2023

2023Vivado Synthesis的各种流程

Vivado IPI (IP Integrator)提供了直观的模块化的设计方法。用户可以将Vivado IP Catalog中的IP、用户自己的RTL代码、或者用户已有的BD文件添加到IP Integrator中构成Block Design,设计更复杂的系统,如下图所示。

2022-07-15 11:39:12 1335

1335

1335

1335使用VCS仿真Vivado IP核时遇到的问题及解决方案

前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有些许改进,所以写这篇文章补充下。

2022-08-29 14:41:55 1549

1549

1549

1549FPGA应用之vivado三种常用IP核的调用

今天介绍的是vivado的三种常用IP核:时钟倍频(Clocking Wizard),实时仿真(ILA),ROM调用(Block Memory)。

2023-02-02 10:14:01 2529

2529

2529

2529VCS独立仿真Vivado IP核的一些方法总结

最近,需要使用VCS仿真一个高速并串转换的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原语。而此前我只使用VCS仿真过Quartus的IP核。

2023-06-06 11:09:56 1597

1597

1597

1597

Xilinx Vivado DDS IP使用方法

DDS(Direct Digital Frequency Synthesizer) 直接数字频率合成器,本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

2023-07-24 11:23:29 1728

1728

1728

1728

把子模块包含网表的RTL代码添加到BD中的方法分享

Vivado以IP为核心的设计理念的一个重要支撑就是IP Integrator(简称IPI,IP集成器)。用户可以很便捷地把VivadoIP Catalog中的IP拖到IPI中形成Block Design(.bd文件)。

2023-08-24 09:10:50 628

628

628

628

Vivado中BRAM IP的配置方式和使用技巧

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 2605

2605

2605

2605

Vivado IP核Shared Logic选项配置

在给Vivado中的一些IP核进行配置的时候,发现有Shared Logic这一项,这里以Tri Mode Ethernet MAC IP核为例,如图1所示。

2023-09-06 17:05:12 529

529

529

529

Vivado Design Suite用户指南:采用IP进行设计

电子发烧友网站提供《Vivado Design Suite用户指南:采用IP进行设计.pdf》资料免费下载

2023-09-13 11:18:53 0

0

0

0为什么说Vivado是基于IP的设计?

Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 1060

1060

1060

1060

FPGA实现基于Vivado的BRAM IP核的使用

文章是基于Vivado的 2017.1的版本,其他版本都大同小异。 首先在Vivado界面的右侧选择IP Catalog 选项。

2023-12-05 15:05:02 317

317

317

317 电子发烧友App

电子发烧友App

评论