本文介绍了FPGA在实现高清低码流视频编码中的作用以及如何具体实现。目前现状是高清视频720p的码流一般在2Mbps以上,1080p的码流在4Mbps以上,要大幅度降低码流,需要从几个方面考虑。

2013-09-23 13:41:15 1986

1986 的面阵CCD驱动时序发生器设计,基于CPLD的面阵CCD驱动时序发生器设计及其硬件实现,基于CPLD的线阵CCD驱动电路的设计,基于CPLD的线阵CCD驱动电路设计与实现,基于CPLD的线阵CCD驱动

2019-06-03 16:45:25

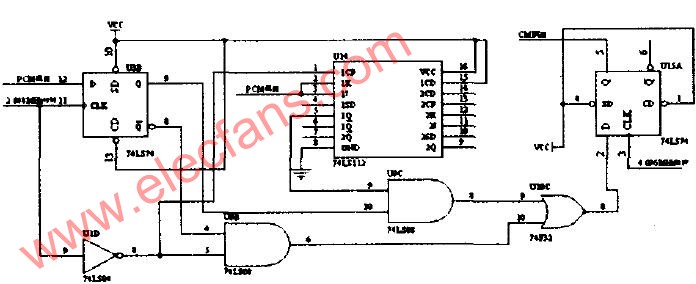

完全正确。 实践表明,运用CPLD实现CMI编码具有软件开发周期短、成本低、执行速度高、实时性强、升级方便等特点,而且可以把该电路和其他功能电路集成在同一块CPLD/FPGA中,减少了外接元件的数目,提高了集成度,而且有很大的编程灵活性,很强的移植性,因此有很好的应用前景。

2010-08-09 18:24:16

今天参加了个汽车电子的面试,面试官问我愿意做CMI吗,我问CMI是什么,大概描述了一下,似乎是软件流程管理。百度上谷歌了一下还是没得到想要的答案。各位谁知道,静候。

2012-09-17 23:00:18

它们的基本设计方法是借助于 EDA 设计软件,用原理图、状态机和硬件描述语言等方法,生成相应的目标文件,最后用编程器或下载电缆,由 CPLD/FPGA 目标器件实现。 生产 CPLD/FPGA

2019-03-04 14:10:13

FPGA CPLD入门教程很不错

2012-07-14 15:53:37

words:FPGA/CPLD;Synchronous design;Clock;Metastable state利用FPGA/CPLD实现数字系统电路设计时,如何设计出可读性强、重复利用率高、工作稳定可靠

2009-04-21 16:42:01

FPGA、CPLD常用protel库FPGA&CPLD_LIB.ddb

2012-08-11 10:32:00

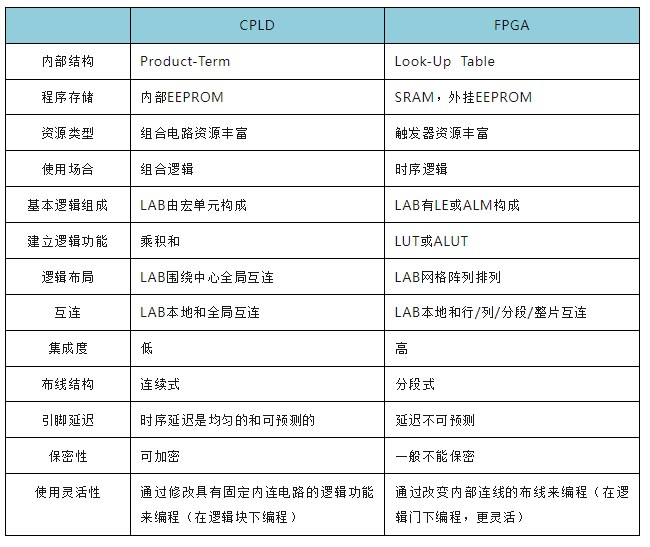

FPGA与CPLD的区别是什么,他与单片机的区别呢

2012-10-07 22:01:57

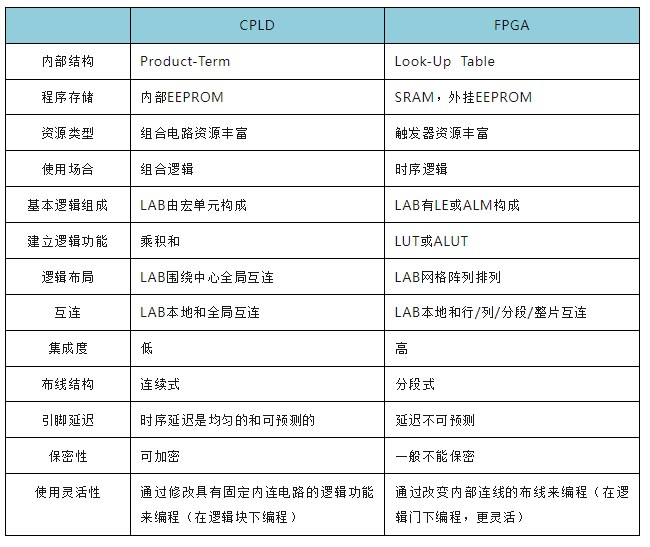

FPGA与CPLD的辨别和分类主要是根据其结构特点和工作原理。通常的分类方法是:将以乘积项结构方式构成逻辑行为的器件称为CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列

2019-07-01 07:36:55

FPGA与CPLD的区别

尽管很多人听说过CPLD,但是关于CPLD与FPGA之间的区别,了解的人可能不是很多。虽然FPGA与CPLD都是“可反复编程的逻辑器件”,但是在技术上却有一些差异。简单

2011-09-27 09:49:48

可以很快进入市场。许多设计人员已经感受到CPLD容易使用、时序可预测和速度高等优点,然而,在过去由于受到CPLD密度的限制,他们只好转向FPGA和ASIC。现在,设计人员可以体会到密度高达数十万门

2012-10-26 08:10:36

和CPLD最大的区别是他们的存储结构不一样,这同时也决定了他们的规模不一样。但是从使用和实现的角度来看,其实他们所使用的语言以及开发流程的各个步骤几乎是一致的。对于大多数的初学者来说,学FPGA还是

2019-02-21 06:19:27

器件。内部基本结构为“与或阵列”。因为任意一个组合逻辑都可以用“与—或”表达式来描述,所以该“与—或阵列”结构有利于实现大量的组合逻辑功能。简单的与或阵列 CPLD逻辑框图 CPLD和FPGA

2020-08-28 15:41:47

用“与—或”表达式来描述,所以该“与或阵列”结构能实现大量的组合逻辑功能) 简单的“与或”阵列:(PAL、GAL、CPLD) 含查找表的逻辑单元:(FPGA) CPLD和FPGA的主要

2020-07-16 10:46:21

和CPLD最大的区别是他们的存储结构不一样,这同时也决定了他们的规模不一样。但是从使用和实现的角度来看,其实他们所使用的语言以及开发流程的各个步骤几乎是一致的。对于大多数的初学者来说,学FPGA还是

2015-03-12 13:54:42

用vhdl实现cpld配置fpga,配置成功后在usermode下设置一个重新配置信号,当信号有效时对fpga进行重新配置;fpga配置程序放在flash内;现在遇到的问题是,上电cpld能够正常配置fpga并且进入usermode ,但是加上重新配置语句过后就不能成功配置fpga,求高人指点~

2013-01-17 22:35:39

cpld高手帮忙解答一下。感兴趣的也可以提出点建议哈。网上一般是fpga与海德汉的编码器接口通讯,但是fpga感觉有点浪费了,想直接用cpld来实现。

2011-05-30 22:45:23

Altera FPGA/CPLD设计与Verilog数字系统设计教程从网上找到了一些Altera FPGA/CPLD经典教材,包含夏宇闻老师的Verilog数字系统设计教程(第2版)Altera FPGA/CPLD设计与Verilog数字系统设计教程

2014-02-17 09:22:18

立题简介:内容:MCU+CPLD/FPGA实现GPIO扩展与控制;来源:实际得出;作用:MCU+CPLD/FPGA实现GPIO扩展与控制;仿真环境:Quartus II 11.0;日期

2021-11-04 07:42:16

XILINX FPGA/CPLD ISE下载教程 第一章 XILINX FPGA/CPLD ISE下载教程——下载.bit文件第二章 XILINX FPGA/CPLD ISE下载教程——烧录Flash 图文详细资料!

2019-08-15 00:32:31

`内容简介· · · · · ·CPLD/FPGA是目前应用最为广泛的两种可编程专用集成电路(ASIC),特别适合于产品的样品开发与小批量生产。本书从现代电子系统设计的角度出发,以全球著名

2018-03-29 17:11:59

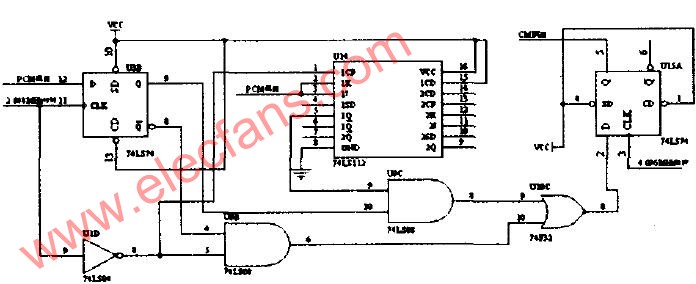

了基于Quartus Ⅱ软件仿真平台的设计与仿真实现,对于光纤信号传输的线路码型及设计数字光端机具有一定的参考作用。【关键词】:CMI码;;CPLD;;光纤传输;;VHDL;;同步时钟提取【DOI

2010-05-06 09:06:05

型。在高次脉冲编码调制终端设备中广泛使用CMI码作为接口码型,在速率低于8448kb/s的光纤数字传输系统中也被建议作为线路传输码型。

2019-08-29 06:41:21

基于FPGA的交织编码技术研究及实现中文期刊文章作 者:杨鸿勋 张林作者机构:[1]贵州航天电子科技有限公司,贵州贵阳550009出 版 物:《科技资讯》 (科技资讯)年 卷 期:2017年 第

2018-05-11 14:09:54

本文介绍了通过处理机用CPLD和Flash实现FPGA配置文件下载更新的方法。

2021-04-28 06:11:19

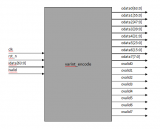

本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2021-05-07 06:33:09

从外部存储器将FPGA配置文件下载更新的方式有哪几种?如何用CPLD和Flash实现FPGA配置?

2021-04-08 06:07:22

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD 逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。

2021-04-29 06:04:14

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

毕业设计 基于EDA的CMI码编码译码器的设计,共20页,7505字 摘要 CMI码是一种应用于PCM四次群和光纤传输系统中的常用线路码型,它具有码变换设备简单、便于时钟提取、有一定的纠错能力

2009-03-25 13:19:20

),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2012-05-23 19:37:24

需要实现这样的功能,我有比如说10个IO从CPLD或者FPGA的左边10个管脚输入,序号为0到9,期望实现能够输出的为任意的序号,比如说我需要输出对应的序号为1,0,3,2,5,4,7,8,9,6

2023-04-23 14:19:12

如何通过添加一个简单的RC电路至FPGA或CPLD 的LVDS输入来实现模数转换器?请问怎么实现低频率(DC至1K Hz)和高频率(高达50K Hz)ADC?

2021-04-15 06:29:55

IJF编码是什么原理?如何实现IJF编码?采用FPGA和集成器件来实现IJF编码

2021-04-13 06:56:04

《Altera FPGA/CPLD设计(高级篇)》结合作者多年工作经验,深入地讨论了Altera FPGA/CPLD的设计、优化技巧。在讨论FPGA/CPLD设计指导原则的基础上,介绍了Altera器件的高级应用;引领读者

2009-02-12 09:19:12 4799

4799 altera fpga/cpld设计 基础篇结合作者多年工作经验,系统地介绍了FPGA/CPLD的基本设计方法。在介绍FPGA/CPLD概念的基础上,介绍了Altera主流FPGA/CPLD的结构与特点,并通过丰富的实例讲解

2009-07-10 17:35:45 57

57 本文介绍了可编程逻辑器件(PLD)在双音多频信号的PCM 编码中的应用。从双音多频信号的PCM 编码到PCM 编码信号的输出,利用CPLD、硬件描述语言VHDL 及MATLAB 来实现整个功能,仿真

2009-08-14 11:40:18 44

44 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。关键词 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 基于单片机的CPLD/FPGA被动串行下载配置的实现:介绍采用AT89S2051单片机配合串行E2PROM存储器,实现CPLD/FPGA器件的被动串行模式的下载配置,阐述了其原理及软硬件设计。 &nb

2009-10-29 21:57:22 19

19 CPLD 最常见的应用是键盘编码器。处理器、ASSP 或者ASIC 一般无法提供足够的引脚来实现键盘功能。I/O 扩展是CPLD 很普通的功能,使处理器采用很少的I/O 便可以解码规模较大的

2010-01-16 16:56:05 18

18 CPLD FPGA高级应用开发指南

2010-04-15 10:56:51 58

58 基于FPGA/CPLD芯片的数字频率计设计摘要:详细论述了利用VHDL硬件描述语言设计,并在EDA(电子设计自动化)工具的帮助下,用大规模可编程逻辑器件(FPGA/CPLD)实现

2010-04-30 14:45:13 132

132 摘 要 :UART是广泛使用的串行数据通讯电路。本设计包含UART发送器、接收器和波特率发生器。设计应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2009-06-20 13:14:52 982

982

摘要: 在简单介绍算术编码和自适应算术编码的基础上,介绍了利用FPGA器件并通过VHDL语言描述实现自适应算术编码的过程。整个编码系统在LTERA公司的MAX+plus Ⅱ软

2009-06-20 13:40:24 1026

1026

基于CPLD/FPGA的多功能分频器的设计与实现

引言

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求

2009-11-23 10:39:48 1139

1139

CMI码简介

CMI又称传号反转码,是一种二电平非归零码。其中“0”码用固定的负、正电平表示,“1”码用交替的正、负电平表示。具

2010-04-20 22:42:15 31823

31823

常用FPGA/CPLD四种设计技巧

FPGA/CPLD的设计思想与技巧是一个非常大的话题,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口

2010-05-12 11:10:43 766

766

基于FPGA和CPLD数字逻辑实现ADC技术

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现

2010-05-25 09:39:10 1309

1309

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的

2010-11-04 10:11:28 625

625

提出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案。在系统程序设计中,首先产生m序列,然后程序再对m序列进行CMI码型变换。在CMI码型变换过程中

2011-01-15 15:44:04 67

67 本文介绍了通过处理机用CPLD和Flash实现FPGA配置文件下载更新的方法。与传统的JTAG或PROM串行下载配置方法相比,此方法具有更新配置文件灵活方便、易于操作、适用于大容量FPGA下载的特点

2018-10-25 05:51:00 8194

8194

在工业控制中如何提高一对多的串口通讯可靠性和系统的集成性成为研究热点。本文利用嵌入式技术,提出基于CPLD/FPGA的多串口扩展设计方案。实现并行口到多个全双工异步通讯口之间

2011-04-27 11:17:15 111

111 在xo640上实现一个简单的Uart,能够解析串口数据,并在寄存器中存储,用FIFO实现数据的传递。那么后期可以通过开发板上的串口经CPLD访问各种数据。比如PC=CPLD=EEPROM等等,极大方便后期

2011-08-05 16:54:46 1741

1741 本方案采用FPGA和集成器件来实现IJF编码和IJF-OQPSK调制具有高度集成化、配置灵活、性能稳定、易于实现的特点,由于IJF编码有很多性能更好的变形,只需在此基础修改ROM中的波形系数

2011-08-11 10:14:41 1382

1382

采用CPLD与绝对式编码器进行高速串行通信,CPLD再把收到的编码器信息转变为并行数据传送给伺服单元中的DSP进行运算控制,本文将给出CPLD与绝对式编码器高速串行通信的软硬件设计方

2011-08-13 14:57:18 2117

2117

本文提出了一种用FPGA实现纠错编码的设计思想,并以Altera MAX+PluslI为硬件开发平台。利用FPGA编程的特点,用软件编程方法,很好的解决了纠错编码中存在的码速变换和实时性问题,实现

2011-11-10 17:10:59 61

61 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。

2011-12-17 00:15:00 57

57 altera FPGA/CPLD高级篇(VHDL源代码)

2012-11-13 14:40:38 134

134 FPGA和CPLD的区别,以及设计思路思想

2016-02-17 11:20:56 38

38 CPLD和FPGA的区别,好东西,喜欢的朋友可以下载来学习。

2016-02-19 16:59:55 0

0 SVPWM算法优化及其FPGA_CPLD实现

2016-04-13 15:42:35 18

18 800Mbps准循环LDPC码编码器的FPGA实现

2016-05-09 10:59:26 37

37 Xilinx-ISE9.x-FPGA-CPLD设计指南合集

2022-03-22 18:03:09 76

76 CPLD和FPGA 的介绍和学习文档

2016-09-02 17:01:13 16

16 基于FPGA/CPLD的UART功能设计

2017-01-23 20:45:37 30

30 CPLD和FPGA都是我们经常会用到的器件。有的说有配置芯片的是FPGA,没有的是CPLD;有的说逻辑资源多的是FPGA,少的是CPLD;有的直接就不做区分,把他们都叫做FPGA。那么两者到底有什么区别呢?下面我们就以Altera公司的CPLD和FPGA为例来说说两者的区别。

2017-09-18 16:35:32 5

5 FPGA/CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。 FPGA/CPLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法

2017-10-09 09:52:20 14

14 FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域

2017-10-24 10:04:00 46702

46702 数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2018-04-26 11:53:00 1121

1121

FPGA LAB和CPLD的LAB设计不同。CPLD LAB由宏单元构成,包括自己的本地可编程阵列,而FPGA LAB由大量的逻辑模块构成,这些模块被称为逻辑单元,即LE,而且本地互连和逻辑分开。LE看起来可能和CPLD宏单元相似,但更容易配置,有更丰富的特性来提高性能,减少逻辑资源的浪费。

2018-04-17 17:02:00 1979

1979

出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案

2018-05-31 04:38:00 2334

2334

CPLD和FPGA都是我们经常会用到的器件。有的说有配置芯片的是FPGA,没有的是CPLD;有的说逻辑资源多的是FPGA,少的是CPLD;有的直接就不做区分,把他们都叫做FPGA。那么两者到底有什么区别呢?下面我们就以Altera公司的CPLD和FPGA为例来说说两者的区别。

2018-05-24 02:03:00 49472

49472

CPLD通常用于实现前面提到的简单组合逻辑功能,并负责“引导”FPGA以及控制整个电路板的复位和引导顺序。

2018-09-27 11:56:01 6191

6191 介绍了采用CPLD和Flash器件对FPGA 实现快速并行配置,并给出了具体的硬件电路设计和关键模块的内部编程思路。

2018-10-24 15:15:49 7

7 本文档详细介绍的是FPGA教程之CPLD与FPGA的基础知识说明主要内容包括了:一、复杂可编程逻辑器件简介二、CPLD的组成与特点三、FPGA的组成与特点四、CPLD与FPGA的异同五、主要的PLD厂商

2019-02-27 17:09:32 32

32 本文档详细介绍的是FPGA教程之CPLD和FPGA的配置与下载的详细资料说明主要内容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下载配置,三、FLEX/ACEX系列FPGA的下载配置,四、ALTERA的编程文件

2019-02-28 09:56:18 17

17 详细探讨了卷积Turbo码编码器实现过程中的关键问题,结合CCSDS及IMT-2000国际通信标准给出了具体解决方案。使用Maxplus2开发工具在CPLD.上实现了整个卷积Turbo码编码器并给出了系统分析,实验结果表明了该编码器的正确性和合理性。

2019-05-30 17:26:55 9

9 对于CPLD/FPGA初学者而言,如何实现双向信号往往是个难题。duoduo 当年初接触CPLD/FPGA的时候也为这个问题头疼过。让我们透过下面这个简单的例子看看CPLD/FPGA设计中如何实现双向信号。

2019-06-11 16:13:51 15

15 CPLD和FPGA都是我们经常会用到的器件。有的说有配置芯片的是FPGA,没有的是CPLD;有的说逻辑资源多的是FPGA,少的是CPLD;有的直接就不做区分,把他们都叫做FPGA。

2019-09-13 14:58:00 5135

5135 FPGA/CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。

2020-01-20 09:29:00 3264

3264 本文主要介绍CPLD和FPGA的基本结构。 CPLD是复杂可编程逻辑器件(Complex Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field

2020-09-25 14:56:33 12233

12233

CPLD/FPGA的基本知识讲解。

2021-03-30 09:55:18 27

27 今天是画师第二次和各位大侠见面,执笔绘画FPGA江湖,本人最近项目经验,写了篇基于FPGA的Varint编码(压缩算法)实现,这里分享给大家,仅供参考。如有转载,请在文章底部留言,请勿随意转载,否则

2021-04-02 16:29:16 1580

1580

Altera FPGA CPLD学习笔记(肇庆理士电源技术有限)-Altera FPGA CPLD学习笔记

2021-09-18 10:54:41 79

79 FPGA CPLD数字电路设计经验分享.(电源技术发展怎么样)-FPGA CPLD数字电路设计经验分享

2021-09-18 10:58:03 51

51 FPGA CPLD中的Verilog设计小技巧(肇庆理士电源技术有限)-FPGA CPLD中的Verilog设计小技巧

2021-09-18 16:49:18 35

35 立题简介:内容:MCU+CPLD/FPGA实现GPIO扩展与控制;来源:实际得出;作用:MCU+CPLD/FPGA实现GPIO扩展与控制;仿真环境:Quartus II 11.0;日期

2021-10-29 10:21:11 2

2 都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。

2023-05-18 08:56:57 350

350

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB使用基于LUT的逻辑单元。

2023-06-28 11:28:04 862

862

可编程逻辑包括 PAL、GAL、PLD 等。通过不断发展,它已经发展成为现在的CPLD/FPGA。CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)的功能基本相同,只是实现原理略有不同

2023-07-03 14:33:38 6041

6041

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB使用基于LUT的逻辑单元。CPLD的LAB围绕中心全局互连排列,随着器件中逻辑数量的增加,呈指数

2024-01-23 09:17:04 280

280

电子发烧友App

电子发烧友App

评论