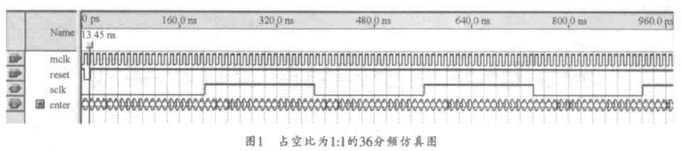

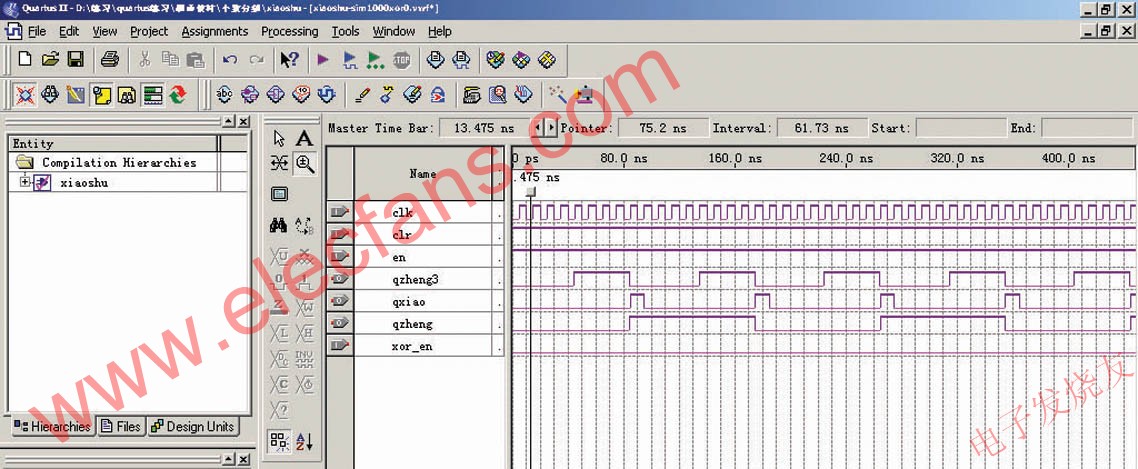

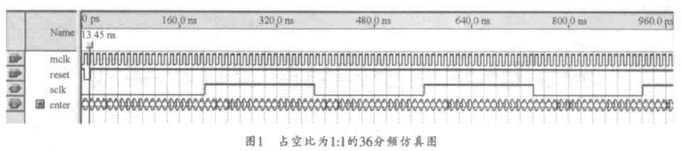

本文首先介绍了各种分频器的实现原理,并在FPGA开发平台上通过VHDL文本输入和原理图输入相结合的方式,编程给出了仿真结果。最后通过对各种分频的分析,利用层次化设计思想,综合设计出了一种基于FPGA的通用数控分频器,通过对可控端口的调节就能够实现不同倍数及占空比的分频器。

2015-05-07 09:43:16 4685

4685

初学FPGA,听说分频貌似挺重要,是必备的基础技能。小白的我今天就从奇偶分频开始我的FPGA学习成长之路偶数分频很简单的哈,打字蛮累的,直接上代码/*************6分频

2016-03-30 11:35:51

`基于FPGA+的任意小数分频器的设计基于FPGA的多种分频设计与实现基于FPGA的小数分频器的实用Verilog 实现基于FPGA 的通用分频用Verilog+HDL实现基于FPGA的通用分频

2012-02-03 15:02:31

设计RISC微处理器需要遵循哪些原则?基于FPGA技术用VHDL语言实现的8位RISC微处理器

2021-04-13 06:11:51

的设计早期就能查验设计系统的功能可行性,随时可对设计进行仿真模拟。3.大规模设计一些大型的 FPGA 设计项目必须有多人甚至多个开发组共同并行工作才能实现。VHDL 语句的行为描述能力和程序结构决定了它具有

2018-09-07 09:04:45

VHDL与FPGA设计

2012-08-17 09:44:37

请教大家怎么用VHDL语言实现减法运算?在FPGA设计时又该怎么操作呢?

2012-05-17 20:07:12

数字示波器的FPGA实现, VHDL语言,测试通过(仅供参考)

2009-11-06 19:53:52

所示。图22 八种编码波形总结1) 运用VHDL编写以上八种编码是可行的。2) 经过观察各模块的仿真波形,符合各个编码的特性。3) 通过整体程序的调试仿真,并在FPGA上实现了波形的键选。

2015-01-29 14:11:42

摘要:为了实现对非相干雷达的接收相参处理,基于数字稳定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL编程语言,设计了一种基于FPGA的DSU硬件实现方法。实验结果表明

2019-06-28 08:27:33

从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,完全可以通过计数器来实现,如进行三分频,通过待分频时钟

2019-06-14 06:30:00

各位朋友,大家好!我刚学习FPGA,选择的是VHDL语言,试着编写了一个二分频和四分频的程序,二分频成功了,但四分频却有问题,代码如下:library ieee;use

2012-11-27 22:03:47

Altera的PLL,Xilinx的DLL)来进行时钟的分频、倍频以及相移设计,但是,对于时钟要求不太严格的设计,通过自主设计进行时钟分频的实现方法仍然非常流行。首先这种方法可以节省锁相环资源,再者

2014-06-19 16:15:28

【摘要】:介绍了基于FPGA的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL语言进行了编译并且给出了仿真图。本

2010-04-26 16:09:01

不知道有没有大神做过:基于FPGA的图像边缘检测系统设计,用VHDL语言实现

2018-05-10 00:22:07

字电路中会经常用到多种不同频率的时钟脉冲,一般采用由一个固定的晶振时钟频率来产生所需要的不同频率的时钟脉冲的方法进行时钟分频。

2019-10-08 10:08:10

,一般情况下,速度指标是首要的,在满足速度要求的前提下,尽可能实现面积优化。因此,本文结合在设计超声探伤数据采集卡过程中的CPLD编程经验,提出串行设计、防止不必要锁存器的产生、使用状态机简化电路描述、资源共享,利用E2PROM芯片节省片内资源等方法对VHDL电路进行优化。

2019-06-18 07:45:03

你好,我是西安大略大学的研究生。我目前正在使用Virtex5 XUPV5 -LX110T FPGA开发板。我使用DCM在VHDL中编写了一个简单的时钟分频器,我使用IMPACT对代码进行了编程。我

2020-06-12 14:23:23

利用现场可编程门阵列(FPGA)和VHDL 语言实现了PCM码的解调,这样在不改变硬件电路的情况下,能够适应PCM码传输速率和帧结构变化,从而正确解调数据。

2021-05-07 06:58:37

本文介绍利用VHDL语言实现 FPGA与单片机的串口异步通信电路。

2021-04-29 06:34:57

从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,完全可以通过计数器来实现,如进行三分频,通过待分频时钟

2019-07-09 09:11:47

介绍了利用现场可编程逻辑门阵列FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法。重点介绍了DDS技术在FPGA中的实现方法,给出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC进行直接数字频率合成的VHDL源程序。

2021-04-30 06:29:00

大家好, 我想多闹钟。实际上我使用50Mhz时钟频率,我想把它作为100Mhz时钟频率。没有PLL,DCM,是否有任何其他可能性来实现使用vhdl编程逻辑? 我知道,如何将时钟分频如80Mhz时钟

2020-04-07 13:25:33

AC-Link音频编/解码原理是什么?怎么实现AC-Link数字音频VHDL编/解码的FPGA设计?

2021-05-10 06:46:20

本文介绍直流电机进行位置控制的方法,给出位置控制模块的设计和实现,使用 VHDL语言进行编程完成了FPGA对直流电机的各种控制。

2021-05-10 06:19:17

怎么设计一款基于FPGA的多种分频设计?

2021-05-08 07:06:43

学校要求的课程设计基于VHDL实现任意小数分频

2014-04-24 09:09:31

刚接触FPGA 想用FPGA实现422通讯 求大牛给一个实现UART的VHDL的程序

2013-12-05 20:40:39

有关VHDL分频的问题,最终输出不对,程序什么的都有,程序的作用是对时钟先进行10分频,再进行20分频,最终级联实现200分频,程序如附件

2016-10-27 12:56:08

求助帮忙用vhdl实现一段fpga框图,(价钱可商议),急用!!!!求助帮忙用vhdl实现几个fpga框图,(价钱可商议),急用!!!!已经有现成的vhdl程序编码主要是想完成资料里面已经有的框图出来,,写材料需要用的~~~有意者请联系我的QQ:444741540 或者***~~越快越好~~~~

2013-03-29 18:04:41

使用VHDL语言怎样实现数控半整数分频器,就当输入为3时,就实现3.5分频,当输入为4时,就实现4.5分频,同时要求占空比为50%。

2014-12-02 18:28:57

传统交通灯控制器多数由单片机或PLC 实现。本论文介绍一种用FPGA 实现交通灯控制器的设计方法。关键词:FPGA; VHDL; MAXPLUSll; 交通灯控制器Abstract:Traffic light controller is usually

2009-06-12 11:12:52 90

90 FPGA/VHDL技术是近年来计算机与电子技术领域的又一场革命。本书以AAltera公司的FPGA/CPLD为主详细介绍了FPGA、CPLD为主详细介绍了FPGA的相关知识,MAX+PLUSⅡ开发环境和VHDL语言基础,并

2009-07-11 15:06:42 58

58

介绍了用VHDL 语言在硬件芯片上实现浮点加/ 减法、浮点乘法运算的方法,并以Altera

公司的FLEX10K系列产品为硬件平台,以Maxplus II 为软件工具,实现了6 点实序列浮点加/ 减法

2009-07-28 14:06:13 85

85 在复杂数字逻辑电路设计中,经常会用到多个不同的时钟信号。介绍一种通用的分频器,可实现2~256 之间的任意奇数、偶数、半整数分频。首先简要介绍了FPGA 器件的特点和应用范

2009-11-01 14:39:19 78

78 本文介绍了一种能够完成半整数和各种占空比的奇/偶数和的通用的分频器设计,并给出了本设计在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中实现后的测试数据和设计硬件的测

2009-12-19 16:25:09 65

65 基于FPGA 的等占空比任意整数分频器的设计

给出了一种基于FPGA 的等占空比任意整数分频电路的设计方法。首先简要介绍了FPGA 器件的特点和应用范围, 接着讨论了一

2010-02-22 14:22:32 39

39 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过

2010-07-17 17:55:57 36

36 摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2006-03-13 19:36:44 869

869

用VHDL语言实现3分频电路

标签/分类:

众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相

2007-08-21 15:28:16 5527

5527 容错系统中的自校验技术及实现方法

阐述了自校验技术在容错系统中的作用,给出了自校验网络实现原理及实现方法,指出用VHDL语言结合FPGA/CPLD是实现大规模自校

2009-03-28 16:23:21 603

603

【摘 要】 通过设计实例详细介绍了用VHDL(VHSIC Hardware DescriptionLanguage)语言开发FPGA/CPLD的方法,以及与电路图输入和其它HDL语言相比,使用VHDL语言的优越性。

2009-05-10 19:47:30 1111

1111

基于多种EDA工具的FPGA设计

介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配置下载等具体内容。并以实

2009-05-14 18:38:38 854

854

摘要:介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配置下载等具体内容。并以实际操作介绍了

2009-06-20 11:42:45 522

522

摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

2009-06-20 12:41:04 1238

1238

摘 要: 本文通过在QuartursⅡ开发平台下,一种能够实现等占空比、非等占空比整数分频及半整数分频的通用分频器的FPGA设计与实现,介绍了利用VHDL硬件描

2009-06-20 12:43:07 562

562

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2009-06-20 12:45:00 627

627

摘要:介绍了一种用VHDL设计USB2.0功能控制器的方法,详术了其原理和设计思想,并在FPGA上予以实现。

关键词:USB VHDL FPGA

在视

2009-06-20 13:26:46 1474

1474

摘 要: 阐述了自校验技术在容错系统中的作用,给出了自校验网络实现原理及实现方法,指出用VHDL语言结合FPGA/CPLD是实现大规模自校验网络的有效途径。

2009-06-20 15:46:43 529

529

用VHDL语言实现3分频电路(占空比为2比1)

分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁

2009-06-22 07:46:33 7831

7831 数字电压表的VHDL设计与实现

介绍数字电压表的组成及工作原理,论述了基于VHDL语言和FPGA芯片的数字系统的设计思想和实现过程。 关键词:数字电压表;VHDL语

2009-10-12 19:14:32 1628

1628

基于CPLD/FPGA的多功能分频器的设计与实现

引言

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求

2009-11-23 10:39:48 1139

1139

多种EDA工具的FPGA设计方案

概述:介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配

2010-05-25 17:56:59 670

670

针对目前国内SDH系统中还没有一个专门的E1分接复用芯征,本文介绍一种用高级硬件描述语言VHDL及状态转移图完成该发接复用器的设计的新型设计方法及其FPGA实现。并给出了

2010-08-27 09:42:32 2704

2704

本文采用VHDL描述语言,充分利用Xilinx公司Spartan II FPGA的系统资源,设计实现了一种非对称同步FIFO,它不仅提供数据缓冲,而且能进行数据总线宽度的转换。

2011-01-13 11:33:43 1744

1744 利用FPGA实现时分多址的方法有很多种,但大多数方法都对FPGA芯片资源的占用非常巨大。针对这一问题,提出一种改进型方法来实现时分多址。通过使用FPGA芯片内部的双口随机访问存储器(双口RAM),利用同一块RAM采用两套时钟线,地址线和数据线,例化双口RAM的

2011-01-15 15:41:26 29

29 本书共分8章,主要内容包括典型fpga器件的介绍、vhdl硬件描述语言、fpga设计中常用软件简介、用fpga实现数字信号处理的数据规划、多种结构类型的fir数字滤波器的fpga实现、不同结构

2011-11-04 15:50:12 0

0 本文给出了分频技术通用模型。并结合最新的一些分频技术,提出了一种基于FPGA全新的分频系统的设计方法,简单的介绍了设计的思路、原理及其算法,并对该方案的性能进行了分析,

2011-11-08 18:03:32 137

137 提出了一种基于FPGA的小数分频实现方法,介绍了现有分频方法的局限性,提出一种新的基于两级计数器的分频实现方法,给出了该设计方法的设计原理以及实现框图

2011-11-09 09:36:22 121

121 给出了一种基于FPGA的分频电路的设计方法.根据FPGA器件的特点和应用范围,提出了基于Verilog的分频方法.该方法时于在FPGA硬件平台上设计常用的任意偶数分频、奇数分频、半整数分频

2011-11-09 09:49:33 355

355 介绍了一种基于FPGA的双模前置小数分频器的分频原理及电路设计,并用VHDL编程实现分频器的仿真.

2011-11-29 16:43:06 48

48 为了实现对非相干雷达的接收相参处理,基于数字稳定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL编程语言,设计了一种基于FPGA的DSU硬件实现方法。实验结果表明基于FPGA的

2012-06-26 15:48:36 27

27 altera FPGA/CPLD高级篇(VHDL源代码)

2012-11-13 14:40:38 134

134 文中着重介绍了一种基于FPGA利用VHDL硬件描述语言的数字秒表设计方法,在设计过程中使用基于VHDL的EDA工具ModelSim对各个模块仿真验证,并给出了完整的源程序和仿真结果。

2012-12-25 11:19:24 6071

6071 本书比较全面地阐述了fpga在数字信号处理中的应用问题。本书共分8章,主要内容包括典型fpga器件的介绍、vhdl硬件描述语言、fpga设计中常用软件简介、用fpga实现数字信号处理的数据规划、多种

2015-12-23 11:07:46 44

44 Xilinx FPGA工程例子源码:FM收音机的解码及控制器VHDL语言实现

2016-06-07 14:13:43 11

11 Xilinx FPGA工程例子源码:VHDL实现对图像的采集和压缩

2016-06-07 14:54:57 6

6 用 Verilog实现基于FPGA 的通用分频器的设计时钟分频包括奇数和偶数分频

2016-07-14 11:32:47 45

45 vhdl语法介绍FPGA设计实例nios ii设计实例北航版本

2016-07-14 17:34:13 74

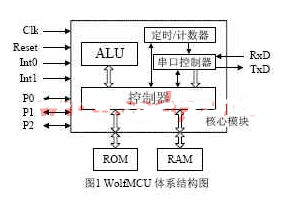

74 目前许多FPGA的逻辑资源(LE)都已超过1万门,使得片上可编程系统SOPC已经成为可能。算术逻辑单元ALU应用广泛,是片上可编程系统不可或缺的一部分。利用VHDL语言在FPGA芯片上设计ALU的研究较少,文中选用FPGA来设计32位算术逻辑单元ALU,通过VHDL语言实现ALU的功能。

2018-07-22 11:22:00 6949

6949

设计背景: 分频在 fpga的设计中一直都担任着很重要的角色,而说到分频,我相信很多人都已经想到了利用计算器来计算达到想要的时钟频率,但问题是仅仅利用计数器来分频,只可以实现偶数分频,而如果我需要

2018-06-13 11:21:48 12390

12390

不太严格的设计,通过自主设计进行时钟分频的实现方法仍然非常流行。首先这种方法可以节省锁相环资源,再者,这种方式只消耗不多的逻辑单元就可以达到对时钟操作的目的。

2019-08-07 08:00:00 9033

9033

本文档的主要内容详细介绍的是FPGA视频教程之FPGA和CPLD与VHDL基础知识的详细资料说明。主要的目的是:1.VHDL入门,2.设计单元,3.体系结构建模基础,4.VHDL逻辑综合,5.层次

2019-03-20 14:35:19 9

9 基于提升框架的小波变换方法,利用FPGA 可编程特性可实现多种小波变换。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近几年提出的一种小波变换方法,用它的框架结构能有效地计算DWT。对于较长的滤波器,LS 的操作次数比滤波器组的操作方式减少将近一半,更适合硬件实现。

2019-08-18 09:47:57 1918

1918

基于提升框架的小波变换方法,利用FPGA 可编程特性可实现多种小波变换。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近几年提出的一种小波变换方法,用它的框架结构能有

2019-08-25 11:01:31 5747

5747

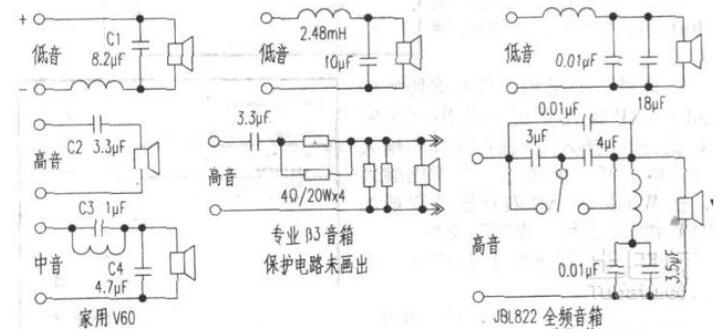

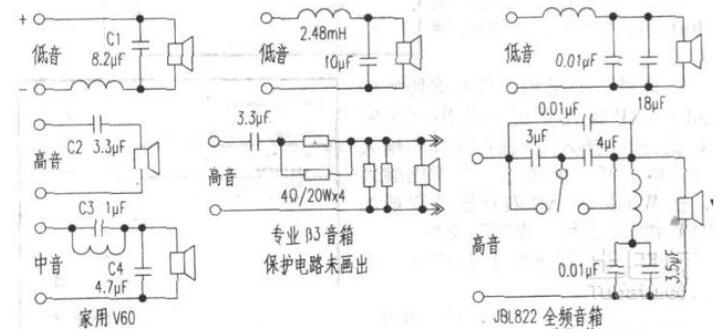

本文主要阐述看音箱分频器的维修方法及音箱分频器接喇叭的方法。

2020-03-28 11:09:59 14938

14938

在数字系统设计中,根据不同的设计需要,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。在基于cpld(复杂可编程逻辑器件)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的实现较为困难。

2020-06-26 09:36:00 825

825

通常情况下,时钟的分频在FPGA设计中占有重要的地位,在此就简单列出分频电路设计的思考思路。

2020-07-10 17:18:03 2192

2192 基于以上讨论,可以看出ASIP+FPGA设计模式可以从很大程度上解决引言中提到的两个难题。为了进行更深入的研究,我们对该设计模式进行了尝试,用VHDL硬件描述语言在FPGA上实现了一个8位微处理器

2020-07-28 17:44:49 562

562

介绍了单片机与FPGA 异步串行通信的实现方法,给出了系统结构原理框图及其部分VHDL 程序,并定义了发送器和接收器的端口信号。

2020-09-29 16:20:00 8

8 本文档的主要内容详细介绍的是使用FPGA实现自动售货机的VHDL程序与仿真资料。

2020-12-21 17:10:00 23

23 本文档的主要内容详细介绍的是使用FPGA实现自动售货机的VHDL程序与仿真资料免费下载。

2020-12-22 17:07:00 15

15 本文档的主要内容详细介绍的是使用FPGA VHDL实现电子点餐项目设计的参考实例资料合集包括了:电子点餐接收端,电子点餐protel格式电路图,电子点餐发送端,电路图和PCB原理图免费下载。

2020-12-23 16:47:39 18

18 本文档的主要内容详细介绍的是使用FPGA实现ADC0809的VHDL控制程序免费下载。

2021-01-18 17:17:00 17

17 本文档的主要内容详细介绍的是使用FPGA实现LCD控制的VHDL程序与仿真资料免费下载。

2021-01-18 17:19:08 10

10 本文档的主要内容详细介绍的是使用FPGA实现LED控制的VHDL程序与仿真资料免费下载。

2021-01-18 17:32:46 12

12 FPGA Express将VHDL描述转换并优化为内部门级等效格式。然后针对给定的FPGA技术编译此格式。

2021-01-21 16:02:09 7

7 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-16 09:45:53 10

10 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为25和15的分频器的设计为例,介绍了在 Maxplus开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法该设计具有结构简单、实现方便、便于系统升级的特点。

2021-04-12 16:29:05 11

11 一种基于FPGA的分频器的实现说明。

2021-05-25 16:57:08 16

16 FPGA分频器是一种常用于数字信号处理、通信系统、雷达系统等领域的电路,其作用是将信号分成多个频段。

2023-05-22 14:29:44 1032

1032

基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 0

0

电子发烧友App

电子发烧友App

评论