锁相环英文名称PLL(Phase Locked Loop),中文名称相位锁栓回路,现在简单介绍一下锁相环的工作原理。

2023-04-28 09:57:31 4380

4380

PLL(锁相环)电路原理是什么?

2022-01-21 07:03:37

,影响系统可靠性,要进一步提高系统实时性,必须研究开发高速嵌入式雷达信号采集系统。这里结合高速嵌入式数据采集系统,提出一种基于CvcloneⅢFPGA实现的异步FIFO和锁相环(PLL)结构来实现

2019-08-21 06:56:32

锁相环仿真,可以参考一下!

2012-08-13 09:11:17

问一下大家,labview的锁相环怎么设计,我不知道怎么设计NCO,计算频率控制字的时候需要系统时钟频率,但是这个不知道怎么弄,大家有知道的吗,帮一下忙,谢谢!

2017-06-20 10:36:08

图解实用电子技术丛书,介绍锁相环(PLL)电路设计与应用,供大家参考

2016-06-21 22:51:39

概述:LTC6946是一款全集成型 VCO 的高性能、低噪声、6.39GHz 锁相环 (PLL),它包括一个基准分频器、具锁相指示器的相位-频率检测器 (PFD)、超低噪声充电泵、整数反馈分频器和 VCO 输出...

2021-04-13 06:31:10

要实现锁相环的基本原理及工作状态,如何编写程序呢?

2014-06-11 21:33:38

请问锁相环仿真用什么软件好,我们需要用到ADF4110VOC选择MAX2606

2016-06-27 15:57:53

锁相环,而他们都是属于软件锁环的范畴。在电力仿真软件中,一般都有PLL模块,只需要将该模块应用一下即可实现锁相环的功能,即该模块可输出系统相角。其实,所谓的PLL模块就是实现上面说的这么一团东西的,在

2015-01-04 22:57:15

听说锁相环可以倍频,倍频时输入输出频率都不一样,如何锁相呢?

2023-04-24 10:14:34

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成器

2018-10-31 15:08:45

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成器

2018-11-06 09:03:16

保证环路所要求的性能, 增加系统的稳定性。压控振荡器受滤波器输出的电压控制, 使得压控振荡器的频率向输入信号的频率靠拢, 也就是使差拍频率越来越低, 直至消除频率差而锁定。锁相环在开始工作时, 通常输入

2022-06-22 19:16:46

本帖最后由 gk320830 于 2015-3-7 20:18 编辑

锁相环的原理,特性与分析所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL 表示。

2008-08-15 13:18:46

第十七章IP核之PLL实验PLL的英文全称是Phase Locked Loop,即锁相环,是一种反馈控制电路。PLL对时钟网络进行系统级的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程

2022-01-18 09:23:55

电荷泵锁相环的基本原理是什么?电荷泵锁相环的噪声模型与相位噪声特性是什么?电荷泵锁相环的相位噪声与环路带宽关系是什么?

2021-06-07 06:57:53

本帖最后由 zhihuizhou 于 2011-12-21 17:43 编辑

锁相环PLL原理与应用 第一部分:锁相环基本原理 一、锁相环基本组成 二、鉴相器(PD) 三

2011-12-21 17:35:00

那个对讲机的锁相环的程序怎么写?是基于STM32单片机的,锁相环芯片使用的是LMX2337

2014-04-09 08:18:49

概述:TLC2932是德州仪器公司出品的一款锁相环电路(PLL)芯片,它由压控振荡器和以沿触发方式工作的鉴相器(PFD:phflse frequency deteclor)组成。

2021-04-08 07:48:53

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号

2022-01-11 06:34:28

本人在进在做锁相环的仿真,进行频率跟踪的用的,可是怎么做都放不出波形,可有会仿真锁相环的?

2014-06-23 11:14:38

频率合成器的主要性能指标锁相环频率合成器原理锁相环频率合成器捕捉过程的分析与仿真

2021-04-22 06:27:35

如题,AD9957的锁相环一直失锁,不用锁相环输出点频信号时正常的,用了锁相环后,PLL_LOCK信号一直为低,sync_clk输出信号也不是稳定的周期信号,环路滤波器的值有点误差,因为现有的器件没有那么精确的电容电阻值,问下锁相环的控制除了控制CFR3之外还有别的要注意的么?

2018-12-10 09:30:24

Actel FPGA PLL锁相环的最大能达到几倍频几分频?我在网上查了一下有人说是20倍频,10分频,但是我没有在芯片手册里面找到资料,想要确认一下。

2014-12-04 11:25:15

求助,CD4046锁相环的参数要怎么设计呀?我设计的时候是根据datasheet设计的,可是用protues仿真的时候,在中心频率也入不了锁,引脚1输出总是一高一低,然后把输入信号的电压调大后,不管

2020-10-11 13:02:47

在我们设计工程中我们会用到100M,500M等时钟,如果我们的晶振达不到我们就需要倍频,再上一个文档中我们了解到了分频,可是倍频我们改怎么做了,这里我们就用了altera的IP核锁相环。今天我们将去

2019-06-17 08:30:00

电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。编辑添加图片注释,不超过 140 字(可选)在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以

2022-05-31 19:58:27

在使用K60的过程中发现自己pllinit()不清楚,才发觉自己锁相环的概念还不懂,so,赶紧补补……锁相环(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制

2021-11-04 08:57:18

`可编程锁相环(PLL)解决方案有多种尺寸和类型可供选择。 PLL以整数N或小数N形式提供同时根据带宽利用无源或有源环路滤波器。 可以通过3线串行接口对其进行快速编程同时提供非常低的杂散抑制和较小

2021-04-03 17:00:58

概述:SC9256是SILAN半导体公司生产的一款锁相环(PLL),大规模集成电路数字调谐系统(DTS),内置2个预分频系数。所有功能都通过3根串行总线控制。这些大规模集成电路,用于配置高性能的数字调谐系统。它采用贴片16脚封装和双列16脚封装。

2021-05-18 06:51:23

概述:SC9257是杭州士兰微电子生产的一款数字调谐系统锁相环(PLL FOR DTS)。该SC9257是锁相环(PLL)的LSI数字调谐系统(DTS)与内置的2模数预分频器。所有功能都通过3根串行

2021-05-18 07:27:48

信号源的任何应用的理想选择,并且利用微带或陶瓷谐振器拓扑结构可提供出色的相位噪声性能。测试仪器雷达系统SFS10500H-LF锁相环SFS10625H-LF锁相环SFS10640H-LF锁相环

2021-04-03 17:05:46

labview虚拟锁相环的跟踪锁定时间过长,请问有什么办法可以解决这个问题

2011-05-17 19:03:34

`PLL锁相环介绍与简单应用实验目的:1.学会配置Altera提供的PLL IP核并进行仿真了解其接口时序2.利用参数化设计一个简易的系统进行验证已配置好的PLL实验平台:芯航线FPGA学习套件主板

2017-01-05 00:00:52

介绍了频率捕获、电荷泵锁相环等热点应用问题。目录:第1章 简介1.1 PLL的性质1.1.1 带宽1.1.2 线性1.2 本书结构1.3 文献及注释1.3.1 推荐书目1.3.2 技术文集1.3.3

2017-08-10 17:44:31

摘要:锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。本文将参考上述各种应用来介绍PLL

2019-10-02 08:30:00

什么是锁相环 (PLL)?一个锁相环PLL电路通常由哪些模块组成?

2022-01-17 06:01:54

锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。今天斑竹带来干货好文,参考上述各种应用来

2019-01-28 16:02:54

本文设计了一种宽频率范围的CMOS锁相环(PLL)电路,通过提高电荷泵电路的电流镜镜像精度和增加开关噪声抵消电路,有效地改善了传统电路中由于电流失配、电荷共享、时钟馈通等导致的相位偏差问题。设计了

2019-07-08 07:37:37

采用后向Euler数值积分法实现二阶锁相环的一个仿真模型,对二阶锁相环进行仿真,那位大侠做过?可以参考下原代码不?

2012-05-28 17:21:05

说明。所提供的组成部分是,没有负债。它可以自由使用和修改。YouTube视频显示组件在行动:自定义锁相环(PLL)演示使用PSOC5微控制器-YouTube当做,奥迪赛1拉链3.4兆字节邮编2.1兆

2018-11-07 17:06:05

全数字锁相环的设计及分析 1 引 言 锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数

2010-03-16 10:56:10

锁相环路是一种反馈控制电路,简称锁相环(PLL)。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环通常由鉴相器(PD)、环路滤波器(LF

2019-03-17 06:00:00

设计并调试锁相环(PLL)电路可能会很复杂,除非工程师深入了解PLL 理论以及逻辑开发过程。本文介绍PLL设计的简易方法,并提供有效、符合逻辑的方法调试PLL 问题。

2021-04-07 06:28:03

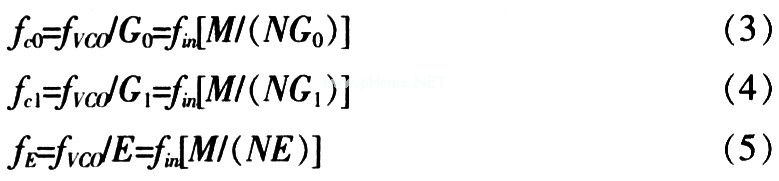

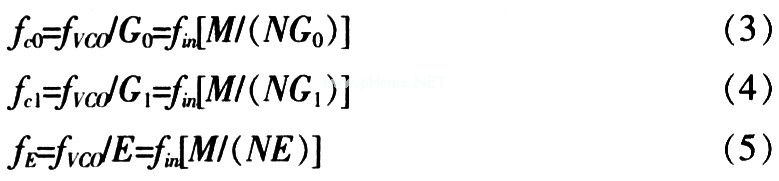

伴随着高频抖阵,估算的反电动势中将存在高频抖阵现象,会导致较大的角度估计误差,因此锁相环系统就显得更加优越。1.1实现框图:由图1可以得到下式:此时,可以将框图等效为下图由图2可得由...

2021-08-27 06:54:13

随着集成电路技术的不断进步,数字化应用逐渐普及,在数字通信、电力系统自动化等方面越来越多地运用了数字锁相环。它的好处在于免去了模拟器件的繁琐,而且成本低、易实现、省资源。本文综合以上考虑,在一片FPGA中以Quartus II为平台用VHDL实现了一个全数字锁相环功能模块,构成了片内锁相环。

2019-10-10 06:12:52

如果没有深入了解 PLL 理论以及逻辑开发过程,可能你在设计并调试锁相环(PLL)电路时会感到非常棘手。那有没有比较容易理解或学习妙招呢?小A今日就为大家送上一份妙计锦囊,并提供有效、符合逻辑的方法助你调试PLL问题。请往下看~

2021-01-27 06:52:20

全数字锁相环由那几部分组成?数字锁相环的原理是什么?如何采用VHDL实现全数字锁相环电路的设计?

2021-05-07 06:14:44

结合高速嵌入式数据采集系统,提出一种基于CvcloneⅢ FPGA实现的异步FIFO和锁相环(PLL)结构来实现高速缓存,该结构可成倍提高数据流通速率,增加数据采集系统的实时性。采用FPGA设计高速缓存,能针对外部硬件系统的改变,通过修改片内程序以应用于不同的硬件环境。

2021-04-30 06:19:52

控制用微处理器的主要性能有哪些?处理器在调频(FM)调谐器中的应用是什么?数字调谐系统有哪些性质?怎样去设计一种基于PLL(锁相环)合成器的数字调谐系统?

2021-08-17 07:03:36

堆叠着鉴相、同相积分、中相积分、滤波等专用名词。这些概念距离硬件设计实现数字锁相环较远。Div20PLL Port(clock : in std_logic; --80M local clkflow

2012-01-12 15:29:12

数字锁相环设计源程序PLL是数字锁相环设计源程序, 其中, Fi是输入频率(接收数据), Fo(Q5)是本地输出频率.目的是从输入数据中提取时钟信号(Q5), 其频率与数据速率一致, 时钟上升沿锁定在数据的上升和下降沿上;顶层文件是PLL.GDF

2009-12-18 10:37:37

最全面最权威的锁相环PLL原理与应用资料非常经典的资料

2022-12-02 22:39:56

模拟锁相环与数字锁相环的主要区别在哪里?

2023-04-24 10:48:52

有没有人用过频率能达到300M以上的集成锁相环PLL,急求推荐!!

2015-07-30 17:09:19

求助PLL 锁相环器件选型指导:1) output: Single End clock2) Work Clock: 1Ghz

2018-09-03 11:49:29

求助:锁相环(PLL)电路设计与应用; 日本人写的. [此贴子已经被作者于2010-1-15 18:23:54编辑过]

2009-11-19 15:47:54

频率源可以说是一个通信系统的心脏,心脏的好坏很大程度上决定着一个机体的健康状况,而锁相环又是频率源的主要组成部分,因此性能优异的锁相环芯片对于通信系统来说是非常重要的。锁相环的相位噪声对电子设备

2019-06-25 06:22:21

。本文就将为大家介绍在DSP系统中如何有效避免噪声和EMI产生,对其中的电源隔离和锁相环进行介绍。 电源隔离和锁相环 如何实现最佳供电是控制噪声和辐射的最大挑战。动态负载开关环境很复杂,包括的因素

2018-11-30 17:14:11

本文介绍了电荷泵锁相环电路锁定检测的基本原理,通过分析影响锁相环数字锁定电路的关键因子,推导出相位误差的计算公式。并以CDCE72010 为例子,通过实验验证了不合理的电路设计或外围电路参数是如何影响电荷泵锁相环芯片数字锁定指示的准确性。

2021-04-20 06:00:37

您好,我们目前在做一个调频连续波的雷达,DDS输出50~60MHz,使用ADI的锁相环ADF4108 96倍频至4.8GHz~5.8GHz,扫频周期4ms,点频测试时锁相环的相位噪声还可

2018-08-16 07:18:19

如题,S3C2440是不是默认不开启锁相环PLL的。另外S3C2440与S3C2440A是同一款芯片吗?为什么这两款芯片我看到的关于时钟分频器设置的参数有些是不一样的

2019-05-09 04:05:32

SYSCLK上使用系统锁相环获得48MHz时,我无法从任何来源——FRC、初级XT或HS——获得48MHz:SYSCLOCK频率出现并随意外周期意外消失。有人与系统锁相环打过架吗? 以上来自于百度翻译 以下

2019-06-04 06:45:57

我刚接触锁相环没多长时间,最近想使用ADF4106搭建一个双环锁相环,我阅读的资料都没有说主环路环路滤波器参数计算问题,我想咨询专家ADIsimPLL是否可以仿真计算双环锁相环,如果可以具体怎么考虑,如果可以告诉我一些主环路环路带宽的知识就更好了.

2019-03-07 10:34:03

音频锁相环相关资料集很多好资料哦! [hide]音频锁相环相关资料等.rar[/hide]

2009-12-04 11:43:03

本文针对一款应用于大规模集成电路的CMOS高频锁相环时钟发生器,提出了一种可行的测试方案,重点讲述了锁相环的输出频率和锁定时间参数的测试,给出了具体的测试电路和测试方法。对于应用在大规模电路系统中的锁相环模块,该测试方案既可用于锁相环的性能评测,也可用于锁相环的生产测试。

2021-04-21 06:28:15

Skyworks Solutions 的 SKY72302-21 是一款锁相环,频率为 400-6100 MHz,相位噪声 -80

2023-06-12 17:22:25

Skyworks Solutions 的 SKY74038-21 是一款锁相环,频率为 100-2600 MHz

2023-06-12 17:24:47

Skyworks Solutions 的 SKY72300-362 是一款锁相环,频率为 100-2100 MHz,相位噪声 -91

2023-06-12 17:30:57

锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 4879

4879 异步FIFO和PLL在高速雷达数据采集系统中的应用

1 引言 随着雷达系统中数字处理技术的飞速发展,需要对雷达回波信号进行高速数据采集。在嵌入式条

2009-12-22 17:41:08 2082

2082

锁相环(PLL),锁相环(PLL)是什么意思

PLL的概念

我们所说的PLL。其

2010-03-23 10:47:48 6005

6005 本书是图解电子工程师实用技术丛书之一,本书主要介绍锁相环(PLL)电路的设计与应用,内容包括PLL工作原理与电路构成、PLL电路的传输特性、PLL电路中环路滤波器的设计方法、PLL电路

2011-09-14 17:55:24 0

0 锁相环英文为PLL,即PLL锁相环。可以分为模拟锁相环和数字锁相环。两种分类的锁相环原理有较大区别,通过不同的锁相环电路实现不同的功能。

2011-10-26 12:40:28

如何设计并调试锁相环(PLL)电路 pdf

2016-01-07 16:20:08 0

0 本文档的主要内容详细介绍的是锁相环PLL的原理与应用的详细资料说明包括了:第一部分:锁相环基本原理,一、锁相环基本组成,二、鉴相器(PD)phase discriminator ,三、压控振荡器

2020-04-29 08:00:00 13

13 锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2022-03-29 09:54:55 11472

11472 锁相环 (PLL) 电路存在于各种高频应用中,从简单的时钟清理电路到用于高性能无线电通信链路的本振 (LO),再到矢量网络分析仪 (VNA) 中的超快速开关频率合成器。本文解释了锁相环电路的一些构建模块,并参考了每种应用,以帮助指导新手和锁相环专家导航器件选择以及每种不同应用固有的权衡取舍。

2022-12-23 14:03:54 3612

3612

PLL锁相环版图设计时应注意以下几点:1)确定PLL的频率范围;2)确定PLL的控制电路;3)确定PLL的调节电路;4)确定PLL的输出电路;5)确定PLL的滤波电路;6)确定PLL的控制参数;7)确定PLL的输出参数。

2023-02-14 15:42:59 2085

2085 PLL锁相环倍频是一种用于改变输入信号频率的技术,它可以将输入信号的频率放大或缩小,以达到某种特定的目的。

2023-02-14 15:56:35 1939

1939 pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频器

2023-09-02 14:59:24 1508

1508 景下的时序要求。尤其对于需要高速数据传输、信号采集处理等场景的数字信号处理系统而言,FPGA PLL的应用更是至关重要。本文将介绍FPGA锁相环PLL的基本原理、设计流程、常见问题及解决方法,以及该技术在外围芯片时钟提供方面的应用实例。 一、FPGA锁相环PLL基本原理 1.时钟频率的调

2023-09-02 15:12:34 1319

1319 pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子技术中广泛应用的一种电路,它的作用是将一个特定频率的输入信号转换为固定频率的输出信号。PLL锁相环的三种配置模式分别为

2023-10-13 17:39:48 1102

1102 siumlink中三相锁相环PLL的输入怎么实现? siumlink中三相锁相环PLL的输入是通过输入三相交流电压来实现的。在交流电力系统中,多数情况下使用的是三相电压,因此三相锁相环(PLL

2023-10-13 17:39:56 482

482 了解锁相环(PLL)瞬态响应 如何优化锁相环(PLL)的瞬态响应? 锁相环(PLL)是一种广泛应用于数字通信、计算机网络、无线传输等领域的重要电路。PLL主要用于时钟恢复、频率合成、时钟同步等领域

2023-10-23 10:10:20 869

869

电子发烧友App

电子发烧友App

评论