上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

本帖最后由 gk320830 于 2015-3-8 17:16 编辑

SoC低功耗设计SoC低功耗设计

2012-08-13 16:21:38

期中看不到明显的数据变化。这类方法能够显著降低功耗,不需要来自系统其它部分的任何输入,对性能也不会有任何影响。其它方法则需要来自系统管理硬件或者软件的大量帮助。一个例子是动态电压频率调整(DVFS

2014-09-02 14:51:19

低功耗DRP-AI动态可配置处理器有哪些关键特性呢?

2021-11-08 09:16:49

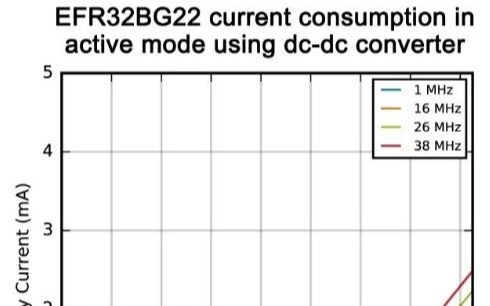

公司最近开发电池供电的低功耗模块,万用表示波器很难测出动态电流,真心问问做低功耗或者穿戴设备方面的工程师或者测试设备技术厂家技术人员或者各路“牛”,你们用什么设备测试?动态定电流范围较大ua - 几十毫安,变化速率快

2015-01-10 22:53:53

低功耗电路设计方法时钟门控技术频繁的信号翻转会造成很大的短路电流,以及对负载电容进行频繁的充放电,即增大所谓的内部功耗(InternalPower)和切换功耗(SwitchPower)。在现代

2021-07-26 06:01:33

功耗存在。静态功耗:也称待机功耗,静态功耗主要由晶体管的漏电流所导致的功耗。动态功耗:包括开关功耗或者成为翻转功耗、短路功耗或者称为内部功耗;动态功耗影响因素:门寄生电容、时钟翻转翻转、时钟频率、供电电压;降低功耗:应当在所有涉及层次上进行,即系统级、逻辑级和物理即,层次越高对功耗降低越有效;在系统

2021-11-11 06:24:53

和NMOS都导通时所引起的功耗;低功耗设计方法在设计一个系统时必须清楚性能和功耗的关系,也就是说需要明白你的系统是需要在尽可能低功耗的条件下提高性能,还是在尽可能高性能的条件下降低功耗,这对于...

2021-11-11 06:03:31

摘要:随着芯片集成度的提高,对一些功能复杂的系统芯片功耗的管理,已经引起大家越来越多的重视,如何控制好SoC的功耗将成为芯片能否成功的重要因素。本文提出一种通过动态管理时钟的策略,达到降低整个So...

2021-04-22 06:00:43

时钟树寄存器配置详解

2021-08-12 06:06:13

ARM日前推出可驱动新一代节能型微控制器(MCU)发展的超低功耗实体IP数据库。ARM 0.18um超低功耗数据库(uLL)具备ARM Cortex处理器系列的内建电源管理优势,结合台积电

2019-07-22 07:00:02

射频前端、低功耗时钟产生架构、振荡器快速启动技术等电路技术,实现最低的峰值、平均和休眠功耗,保证常规200mAH的纽扣电池供电状态下能够持续工作五年以上。 PHY6222通过硬件模块的充分复用以最低

2023-09-18 17:05:13

,如今的终端产品设计大多要求在紧凑的空间内完成,没有更多的空间留给气流和大的散热器,因此热管理、功率管理继续成为FPGA设计的一个重要课题。采用FPGA进行低功耗设计并不是一件容易的事,尽管有许多

2015-02-09 14:58:01

结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。如何减小动态和静态功耗?如何使功耗最小化?

2019-08-27 07:28:24

关于 nRF51 系列 多协议 2.4GHz 射频收发器拥有高性能、超低功耗以及灵活性等好处。它的主要功能包括:在蓝牙低功耗模式下灵敏度为-92.5dB RX, 高达 +4dBm 的输出功率

2012-07-16 13:52:16

RS13100无线MCU超低功耗双模SoC器件

2020-12-21 07:37:19

任务目标配置wakeup唤醒低功耗,上电灯亮5秒后关闭,进入低功耗模式;若未进入低功耗则会灯闪烁;当按下wakeup则唤醒MCU。CubeMx配置PA0配置wakeup唤醒配置LED指示灯别的无需

2021-08-16 08:38:25

MCU学习笔记电源管理系统1. STM32低功耗模式概述2. 寄存器和库函数配置3. HAL库配置PVD实例1.STM32低功耗模式概述系统或电源复位后,微控制器处于运行状态,HCLK位CPU提供

2021-11-03 08:36:30

STM32电源管理有哪几个低功耗模式?分别是什么呢?

2021-09-26 07:29:33

外部中断或RTC唤醒待机模式-(standby):待机模式的功耗为2uA,TAMPER引脚不关断,通过WKUP引脚唤醒在项目中综合选择了停止模式,在该模式下使用两种唤醒方式:WKUP引脚唤醒串口唤醒进入停止模式配置为了尽可能的降低功耗,需要进行IO口的配置,防止它们处于浮空状态,增大电流。ST

2021-08-12 08:15:43

睡眠模式2.停止模式详解停止模式基于 Cortex™-M4F 深度睡眠模式与外设时钟门控。调压器既可以配置为正常模式,也可以配置为低功耗模式。在停止模式下,1.2 V 域中的所有时钟都会停止,PLL、HSI和 HSE RC 振荡器也被禁止。内部 SRAM 和寄存器内容将保留。停止

2021-08-11 07:35:54

STM32的低功耗模式下关闭了时钟怎么进行唤醒

2023-10-09 09:01:01

STM8在低功耗模式下可以直接关闭时钟吗

2023-10-10 08:23:38

: STM32低功耗运行模式之一,该模式下CPU会停止工作,但RAM中的数据仍然保留。待中断或事件触发后程序可以继续运行。note:1、STOP模式退出后,系统时钟会自动配置为MSI或HSI,需要手动重新配置时钟,以及使用时钟的外设。2、为了进一步降低STOP模式下的功耗,可...

2021-08-12 06:54:46

各位大牛,小牛好,我想请教下在max10系列器件的低功耗管理中,通过调用时钟管理控制器和IO缓冲器等IP核,是如何让内核电流下降从而起到降低功耗的效果?

2015-08-17 09:13:50

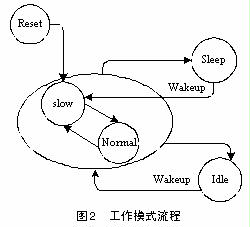

如何实现一套简单的低功耗控制框架。

我觉低功耗的主要核心还是两点:一是根据不同的workload来降频降压;而是外设的休眠。

比如CLK模块,就可以实现对不同外设时钟的管理。

比如DVFS,动态电压频率

2023-10-18 03:27:48

余年经验总结,底层软件低功耗领域里程碑作品(2)系统剖析SoC底层软件低功耗系统的设计、实现与定制化,全面讲解低功耗的知识点以及各种低功耗问题的定位和优化

《SoC底层软件低功耗系统设计与实现

2023-07-28 11:09:40

为什么STM8在停机模式下会出现低功耗管理复位

2023-10-09 07:35:01

的MCU产品。它的RTC最低功耗仅14nA,体积仅3*3mm,最佳计时精度可达+/-2ppm,并集成电源管理、复位、内部RAM。它的MCU采用Cortex-M系列内核,运行功耗仅30μA/MHz,睡眠功耗

2015-02-25 11:07:36

初识电源管理低功耗模式

2021-08-02 06:54:31

。事实上,ATTINY 在深度睡眠模式下消耗0.2 μA 的能量为他们赢得了工程师的尊重,并成为低功耗应用程序设计者的首要任务。今天,ATtiny 由于其在半导体扩展和功率管理方面的快速发展而被纳入

2022-04-02 10:46:30

结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。本文将讨论减小动态和静态功耗的各种方法,并且给出一些例子说明如何使功耗最小化。

2019-07-12 06:38:08

和每立方厘米的能量不断增长。然而,物联网应用在成本和空间方面的限制更高,因此,物联网芯片系统 (SoC) 设计师不能仅依赖更昂贵或更大的电池来延长设备使用时间。本文介绍了设计师如何在低功耗工艺技术上使用Foundation IP(逻辑库和嵌入式存储器)来减少物联网设计的功耗。

2019-07-26 07:01:11

可以轻松实现一个低功耗电子时钟设计。本次微课堂通过讲述MM32L0130 PWR电源控制模式,以及SLCD 和RTC外设配置,实现低功耗应用场景。 MM32L0130 PWR简介 电源控制 PWR

2022-11-09 16:00:17

基于STM8S的Atomthreads低功耗的深度思考

2021-02-01 06:42:39

点”。很显然,降低CPU时钟速率将相应成比例地降低动态功耗,由于动态功耗与电源电压成二次关系,在不影响系统性能的前提下,通过降低电压就可能大大降低功耗。不过,对于特定任务集,降低CPU时钟速率也会成比例地延长

2016-08-20 11:26:46

超低功耗。这4个字在半导体行业随便滥用,特别是当涉及蓝牙低功耗功能的无线电系统单芯片(SoC)。然而,根据无线电SOC的特点和目标应用的需求,声称“超低功耗”可能并不总是准确的或适用的。那么系统级

2018-10-31 09:15:37

如何去设计SoC中的低功耗RF收发器?

2021-05-25 07:04:51

SoC芯片结构及物理实现流程介绍SoC芯片时序约束设计的关键在于功耗管理控制模块的时序约束时钟树设计的内容有哪些?

2021-04-13 06:45:17

通常说来,SoC相对于传统MCU而言能支持更多低功耗模式。其原因在于SoC集成度高,有更多片上组件和多种电源配置,以支持不同的工作需求。

2019-10-30 07:18:33

在设计初始阶段 ,如何选择正确的低功耗蓝牙SoC?

2021-03-11 06:18:48

的更新换代,处理器的设计越来越复杂,资源也越来越丰富,很多嵌入式产品都开始使用嵌入式操作系统,如RTOS,以降低开发难度,加快产品开发效率,缩短产品交付时间。电源管理、低功耗管理在多任务的操作系统下,控制与管理起来,会越来越困难,负责功耗的工程师,不仅需要掌握必备的硬件知识,还需

2021-12-21 07:39:29

Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,工作电压可以进行调整。为了精确地控制DVS,需要采用电压调度模块

2016-06-29 11:28:15

低功耗的特点,也可能将该控制中央芯片的PMIC拆分成主从两路分别进行控制。主路实现全功耗下的电源控制管理。从路则是实现当用户有降功耗的需求情况下的单独电源管理(比如只通过PMIC链路设置激活其中的内部

2023-03-21 13:57:00

`DL-RX809L 基于SOC 的超外差无线接收芯片设计,是一款低功耗、低成本、小体积、带解码(学习码)超外差无线接收模块。内部集成高性价比无线数据接收芯片及性能优异的低功耗单片机,模块具有行业

2019-02-22 18:23:05

、停止模式及待机模式中,若备份域电源正常供电,备份域内的 RTC 都可以正常运行,备份域内的寄存器的数据会被保存,不受功耗模式影响。从表中可以看到,这三种低功耗模式层层递进,运行的时钟或芯片功能越来越少,因而功耗越来越低。模式名称说明进入方式唤醒方式对1.8V区域时钟的影响对VDD区

2021-07-23 08:17:14

如果原本的系统时钟为60MHZ,系统进入低功耗模式-睡眠模式(Sleep):主 LDO 关闭,由超低功耗 ULP-LDO 维持 PMU、内核和基本外设供电。请问这个时候,系统时钟是什么?Fsys是自动切换到32K,还是说需要提前手动切换到32K?

2022-08-15 07:37:57

各位好,我最近用esp32-c3开发了一款产品,由于没有外接32768晶振,没法使用modem sleep模式,我想问能否使用内部的RTC作为低功耗的时钟。还有个问题 espnow可以使用modem sleep来降低功耗吗? PS:ewpnow功耗真的很大,电池吃不消

2023-02-10 06:23:23

行业最低功耗蓝牙SoC NCV-RSL10有什么优势?会给汽车行业带来什么影响?

2019-08-05 06:16:39

不接受时钟触发3在衍生时钟不触发的空闲周期内所产生的冗余态可使触发器的激励函数简化(五)合理的系统划分动态降低功耗设计的出发点是通过增加有限的逻辑来实时地降低功耗。如果所增加的动态逻辑过于复杂,那么其自身

2013-05-16 20:00:33

,这有助于设计出色的系统,实现低功耗优化。不妨来设想一个简单的小型电池供电数字时钟。该设备可用于计时,并在按下按键时能显示当前时间。设备通常处于断电模式以节电,只有在检测到按键动作时才会被唤醒并刷新

2016-07-29 15:25:00

请问一下STM32低功耗模式下GPIO如何配置最节能?

2021-11-23 07:06:38

请问一下ch582在运行stack的情况下,低功耗管理是如何进行的。有没有sleep与idle两种的例程。目前单运行协议stack的peripheral例程时,将近5-6mA .

2022-08-12 07:08:16

翱捷科技(以下简称ASR)正式发布国内首款、采用超低功耗LoRa集成的单芯片SoC - ASR6501。该芯片集成低功耗LoRa Transceiver和低功耗MCU,超小尺寸,超低功耗,集成

2021-09-30 11:26:30

)0.6uA,低速运行85uA@32KHz,高速运行小于4mA@16MHz。低功耗模式及特性:一、 HALT模式系统所有时钟停止,系统不掉电,RAM处于保持状态。因此,可以节省动态功耗。二

2023-02-17 18:04:39

。了解每个组件的功耗拆分信息非常重要,这有助于设计出色的系统,实现低功耗优化。 不妨来设想一个简单的小型电池供电数字时钟。该设备可用于计时,并在按下按键时能显示当前时间。设备通常处于断电模式以节电

2020-08-20 12:30:00

的PM组件,是我自己写的一个简单的低功耗管理线程,线程优先级与idel线程一样,下面是进入和退出低功耗的代码。在唤醒后先打开嘀嗒定时器异常请求再重新配置系统时钟,不知道是否还有其他需要配置的。

2023-02-09 11:37:20

描述TIDA-00675可使用负载开关动态开启/关闭负载,从而降低功耗。设计指南说明了开关频率、占空比和放电电阻的使用如何影响功耗。特性通过动态开启/关闭负载来降低功耗频率、占空比和负载电流对功耗

2022-09-20 07:17:32

功率的情况下最大化功率变得更加困难。如今,性能实际上受到功耗的限制,并且很难在不担心散热和热管理的情况下将功率可靠地输送到芯片的每个部分。矢量的质量(定义为SoC在真实系统中工作时看到的实际活动)对于

2022-03-24 10:45:43

在微控制器的低功耗应用中,对时钟的设置是很重要的一个方面。不同类型的微控制器在低功耗模式下对时钟的配置也各有不同。飞思卡尔公司推出的增强型8 位微控制器HCS08 系列具

2009-04-22 17:03:15 18

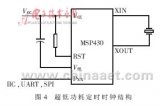

18 时钟和低功耗模式片内集成有PLL(锁相环)电路。外接的基准晶体+PLL(锁相环)电路共同组成系统时钟电路。有关引脚:XTAL1/CLKIN:外接的基准晶体到片内振荡器输入引脚

2009-09-16 12:37:52 12

12 摘要:随着芯片集成度的提高,对一些功能复杂的系统芯片功耗的管理,已

2006-04-16 23:32:20 1063

1063

; 低功耗模式下微控制器时钟配置应用

2007-08-15 15:48:21 456

456

芯海科技开发出低功耗SoC衡器计量芯片

深圳芯海科技公司近日宣布推出低功耗SoC衡器计量芯片CSU11xx系列,包括CSU1182、CSU1181、及CSU1100三款产品。可降低电子

2010-02-22 10:10:26 1059

1059 文结合MSP430系列微处理器,详细论述了通过控制改变MCU的时钟频率来降低功耗的设计方法。

2011-04-15 11:11:36 1999

1999

本文采用自顶而目的设计原则,从体系结构到电路实现上分层次探讨了时钟芯片的功耗来源,并采取相应的控制手段实现芯片的低功耗设计。

2011-10-08 11:50:04 2128

2128

时钟是SOC或块级设计最重要的组成部分之一,本文阐述了目前SOC中各种可配置时钟分频器逻辑的实施方案,强调了各自的问题、优势及局限性。

2013-01-09 10:12:48 2889

2889

瑞萨电子低功耗白皮书——3低功耗设计之 降低时钟 vs MCU待机

2015-12-23 10:40:50 26

26 K60在从Stop、VLPS、LLS等低功耗模式下唤醒后,时钟模式会从进入低功耗模式前的PEE时钟模式变成PBE时钟模式,所以需要在代码中重新配置的。这点可以参考TWR-K60D10的tsi_low_power例程代码。

2017-09-15 17:55:40 8

8 飞思卡尔MQX低功耗管理

2017-10-13 15:37:13 6

6 地影响着芯片的尺寸、成本和性能。本文结合MSP430系列微处理器,详细论述了通过控制改变MCU的时钟频率来降低功耗的设计方法。 1 功耗产生的原因 在CMOS电路中,功耗损失主要包括静态功耗损失和动态功耗损失两部分。其中静态功耗

2017-12-01 17:39:05 341

341

芯片,已不能再只考虑它优化空间的两个方面速度( pe r fo rrnance)和面积(cOst),而必须要注意它已经表现出来的且变得越来越重要的第三个方面功耗,这样才能延长电池的寿命和电子产品的运行时间。 SoC中CMOS电路功耗有:一是静态功耗,主要是由静电流、漏电流

2018-02-06 11:27:40 1

1 面向便携式设备的SoC设计,不仅仅要求性能高、体积小,更要求功耗低。一般而言,SoC的静态功耗很小,而对负载电容充放电的动态功耗很大。 SoC内部,总线上挂着很多功能设备,导致总线的电容负载很大

2018-02-07 14:29:09 1

1 此Zynq低功耗模式(LPM)演示讨论并展示了Xilinx Zynq SOC的动态电源管理功能的实例。

LPM演示清楚地显示了Zynq SOC在提供极低待机功率方面的能力

2018-11-29 06:26:00 4183

4183 STM32低功耗时引脚配置

2020-03-03 13:57:27 7225

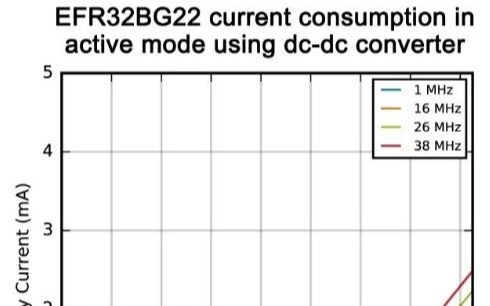

7225 在设计初始阶段,优化低功耗蓝牙(Bluetooth Low Energy)芯片能耗的诀窍会影响存储器大小、时钟速度、工作模式及其他因素的抉择。有鉴于此,Silicon Labs(亦称芯科科技)无线

2020-10-23 14:27:08 4358

4358

门控时钟的设计初衷是实现FPGA的低功耗设计,本文从什么是门控时钟、门控时钟实现低功耗的原理、推荐的FPGA门控时钟实现这三个角度来分析门控时钟。 一、什么是门控时钟 门控时钟技术(gating

2021-09-23 16:44:47 12192

12192

低功耗电路设计方法时钟门控技术频繁的信号翻转会造成很大的短路电流,以及对负载电容进行频繁的充放电,即增大所谓的内部功耗(InternalPower)和切换功耗(SwitchPower)。在现代

2021-10-22 16:51:04 1

1 功耗存在。静态功耗:也称待机功耗,静态功耗主要由晶体管的漏电流所导致的功耗。动态功耗:包括开关功耗或者成为翻转功耗、短路功耗或者称为内部功耗;动态功耗影响因素:门寄生电容、时钟翻转翻转、时钟频率、供电电压;降低功耗:应当在所有涉及层次上进行,即系统级、逻辑级和物理即,层次越高对功耗降低越有效;在系统

2021-11-06 17:21:01 14

14 根据项目需要选择的是停机模式进入停止模式之后,任何外部中断都可以唤醒低功耗,但是需要重新配置时钟,不然系统将以默认时钟(没有经过倍频)运行。1.进入低功耗RCC_APB1PeriphClockCmd

2021-12-07 20:21:22 1

1 置顶/星标公众号,不错过每一条消息! 在后台陆续收到一些关于STM8S低功耗的问题,今天就写一下低功耗相关的内容。1STM8S功耗来源STM8S功耗分静态功耗和动态...

2022-01-05 14:39:05 6

6 只有当FPGA工程需要大量降低功耗时才有必要引入门控时钟,若必须引入门控时钟,则推荐使用基于寄存器的门控时钟设计。

2022-07-03 15:32:17 1617

1617 电子发烧友网站提供《通过动态切换降低功耗的参考设计.zip》资料免费下载

2022-09-06 15:33:14 0

0 门控时钟是一种在系统不需要动作时,关闭特定块的时钟的方法,目前很多低功耗SoC设计都将其用作节省动态功率的有效技术。

2023-04-20 09:15:13 764

764 本文讨论的是基于ARM IP的大规模SoC中的电源(时钟,复位等)管理,适用于众核处理器,手机SoC,汽车SoC等等。如果是小规模的设计可能就不适用了,比如MCU或者是简单应用的IoT芯片。

2023-05-09 10:04:43 1051

1051

门控时钟技术可以用来降低电路的动态功耗,且在一定程度上能减小电路的面积。

2023-06-29 16:45:08 651

651

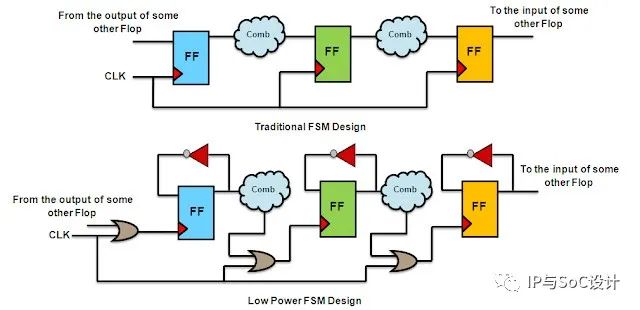

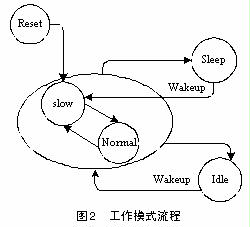

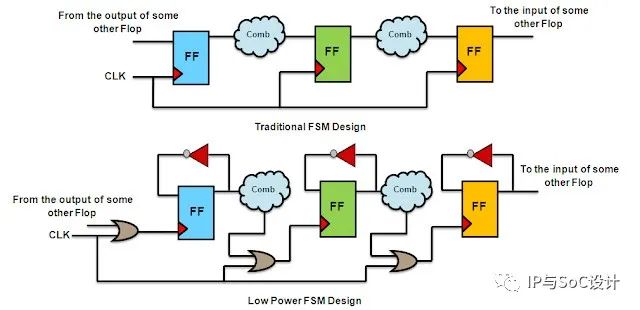

低功耗设计是当下的需要!这篇文章:低功耗设计方法论的必要性让我们深入了解了现代设计的意图和对功耗感知的需求。在低功耗方法标签下的时钟门控和电源门控的后续文章中,讨论了一些SoC低功耗设计的方法。在这篇文章中,我们将考虑一个这样的低功耗设计的FSM,可以推广到任何低功耗时序电路的设计。

2023-10-17 10:41:13 309

309

经常有人问S3模组是怎么配置低功耗模式的?低功耗模式下功耗大概是多少?下面小启就跟大家讲下S3模组低功耗情况。01ESP32S3系列模组三种低功耗模式:•Modem-sleep模式:CPU可运

2024-01-26 08:03:56 546

546

电子发烧友App

电子发烧友App

评论