摩尔定律象一盏明灯推动半导体业进步,特征尺寸缩小立下汗马功劳。然而现阶段尺寸缩小已近极限。从技术路径,自22nm及以下开始由平面晶体管进入三维finFET结构,之后finFET技术成为主导,有可能一直能推进至近3nm,届时晶体管的架构可能要改变,由finFET转向环栅(GAA),纳米片(nanosheet)等架构。时至今日5nm技术已经在手,将于2020年开始试产,然而对于3nm技术,目前仍处于研发之中,一切尚待观察。

不容置疑,全球代工业在进入逻辑制程7nm之后已经开始生变,由于研发费用及成本高耸等因素,2018年格罗方德与联电声言止步,因此导致全球代工业中只剩下台积电,三星,英特尔及中芯国际四家在列,而其中的英特尔在商业代工业中是个“小角色”,以及中芯国际尚未明确它的时间表,所以全球只剩下台积电及三星两家在代工中争霸。

5纳米是个坎

众所周知,7nm是长寿命工艺节点之一,目前台积电及三星均称已经量产,而台积电宣称它拿到全球几乎100%的7nm订单。

台积电的5nm finFET计划已经明朗,它计划2020年上半年开始试生产,估计真正的5nm量产要在2021年,或者之后。台积电的5nm技术相比7nm,它的速度快15%,及功耗低30%。TSMC计划它的5nm的第二个版本也将于2020年中期推出,预期它的速度能再快7%。

根据ICKnowledge及TEL的数据,基于FinFET技术,对于7nm的代工工艺,它的栅间距在56nm到57nm及金属连线间距在40nm。

与此同时,三星最近也高调推出了5nm,预计将于2020年上半年量产。与它的7nm相比,三星的5nm finfet技术,与7nm相比它的速度有25%的增长,功耗降低20%,性能提高10%。

预计到2020年时,苹果、海思和高通等都将采用5纳米的产品设计,推动台积电加速向5nm技术过渡,”国际商业战略(IBS)首席执行官汉德尔•琼斯(Handel Jones)表示。“到2020年第四季度时,TSMC 的5nm晶圆产能将达到每月40,000至60,000片。”

然而估计台积电5nm的订单会低于7nm。因为与7nm相比,5nm完全是一个全新的工艺节点,它需要新的EDA工具和IP等支持。这样导致5nm的成本会更高。根据Gartner的数据,一般来说,5nm产品的设计费用约2.1亿美元到6.8亿美元。

台积电首席执行官魏哲家在近期的一次电话会议上说:N6和N5的数字看起来很接近,但是仍有很大的差别。与N7相比,N5的逻辑密度增加了80%。而N6与N7相比仅为增加18%。因此,N5芯片的总功耗较低。如果愿意跟进N5,它有很多好处,而且是一个完整的工艺节点,但是客户需要时间来重新设计新的产品。而N6的美妙之处在于,如果他们已经用过N7的设计,那么只需花费很少的精力,就可以很快进入N6并获得一些好处。所以根据他们的产品特点和市场情况,(客户)将作出选择。

3纳米技术复杂尚不确定

IMEC的逻辑工程主管Naoto Horiguchi说:“5nm仍然是finFET。“”然后,假设进入到N3时,可能会从finFET过度到其他的器件架构,我们相信它是一种纳米片nanosheet。”

在 5nm之后,下一个完整技术节点为3nm,但是导入3nm是十分困难的。据IBS宣称,设计3nm产品的费用约5亿美元到15亿美元,及它的工艺开发费用约40亿美元到50亿美元,而如果要兴建一条生产线的运营成本约150亿美元到200亿美元。IBS的琼斯说:“基于相同的成熟度,3nm的晶体管成本预计将比5nm高出20%到25%。“与5nm finFET相比,预期性能提高15%,功耗降低25%。

三星是迄今为止唯一宣布其3nm计划的公司。对于这个技术节点,代工将采用一种新的环栅(GAA)技术,或称为纳米片(nanosheet)。由于台积电尚未披露其计划,一些人认为它可能落后于三星。“在3nm,三星在2021年有很大的可能性开始大规模生产,”IBS的琼斯说。“台积电正在加速推进,试图缩小与三星的差距。”

而台积电此次3纳米的制程技术显得有些稳重,它仅宣称进入实验阶段。据报道为迎接它的3纳米厂研发及先期量产,中国***地区环保署于6月11日初审通过竹科宝山用地扩建计划。另外台积电也首度透露,预计把5年后(2024年)的2纳米厂研发及量产都落脚在竹科,以避免研发人才散落或外流的风险。

张忠谋先前曾表示,3纳米制程将在2年内开发成功,即使有“摩尔定律”失效挑战,2纳米仍可能在2025年前问世。

环栅极(GAA)的结构,顾名思义,是FinFET中的栅极被三面环绕的沟道包围,而在GAA中栅极将是被四面沟道包围,预期这样的结构将达到更好的供电与开关特性。只要静电控制能力增加,则栅极的长度微缩就能持续进行下去,摩尔定律重新获得延续的动力。

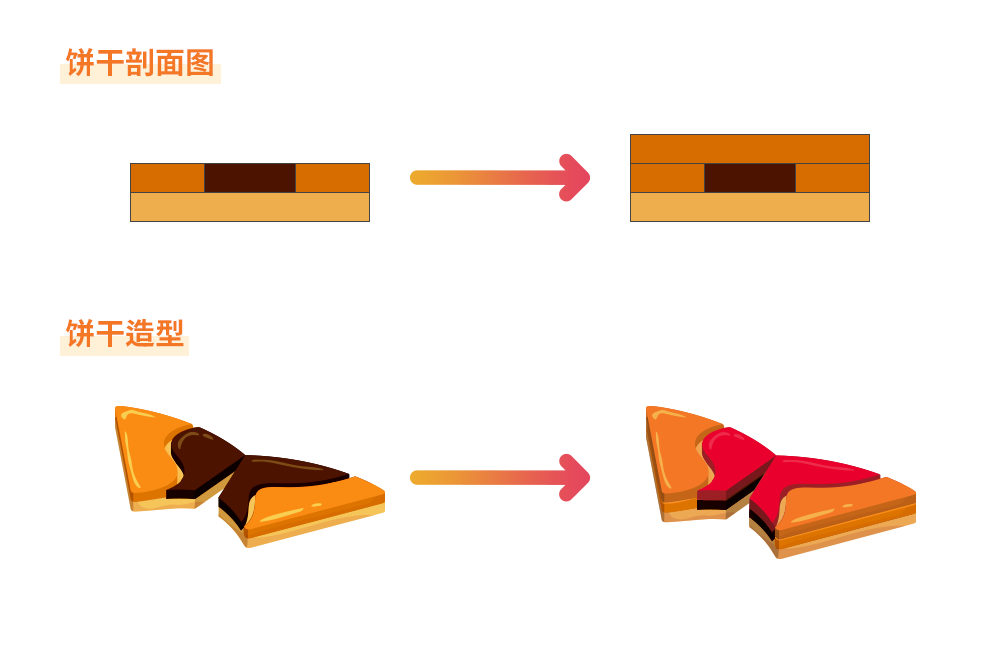

据报道,在纳米片的制程中,第一步是在衬底上交替的沉积薄的硅锗层和硅层的生长。在这种情况下,有硅,硅锗和硅堆,我们称之为超晶格结构,应用材料工程管理高级总监金南成(Namsung Kim)在最近的一次采访中说。因为有锗的含量,需要有一个良好的屏蔽衬层。”

这样每一个Stack由三层SiGe和三层硅组成。然后,在stack上设计微小的片状结构,紧接着再形成浅沟隔离结构,以及形成内间隔区(inner spacers)。

然后,在超晶格结构中去除硅锗层,在它们之间留下带间隔区的硅层。每一个硅层构成器件中的纳米片或者沟道的基础。下一步是为沉积高K材料作为栅极。在纳米片之间,有最小的间隔区。挑战在于如何沉积有功函数的金属厚度。

产业多年来一直在攻克环栅结构,仍存在一些挑战,最主要的挑战是什么,有两个。一个是间隔层,然后是底部的隔离。

业内人士进一步表示,台积电已经做出环栅极的结构,外型就像个园形鼓,因为尺寸比前一代缩小30%,它必须导入新材料InAsGe nanowire 或者 Silicon nanowire,因此制程技术上相当困难,尤其在蚀刻部分是个大挑战,不过以优势来说,环栅极的结构将可以改善ESD静电放电、且优化尖端放电的问题,材料厂的高管也认为,环栅极的结构可以继续微缩栅长尺寸。

什么时候过渡到环栅或纳米片?估计纳米片技术能再延伸2-3个工艺节点。

从研发角度,产业界正走一条在先进工艺节点时延伸环栅及finFET结构。因为环栅结构与finFET相比性能方面仅是适当的提高,如IMEC开初的纳米片工艺,栅间距42nm及金属线间距为21nm。相比5nmfinFET工艺时栅间距为48nm及金属线间距为28nm。

在实验室中IMEC已经开发出用锗作沟道的P型,双堆垒环栅的器件。几乎釆用同样的结构IMEC开发一个栅长近25nm的纳米线。它可以变成纳米片,如同之前的版本它的线宽为9nm。

在5nm以下锗可以起到延伸finFET的功能,IMEC证明Ge n FinFET达到创记录的高Gmsat/SSsat及PBTI可靠性。它是通过改变栅的高k材料工艺来实现。

然而,仍有待观察的是finfet技术能否会扩展到3nm,同样还不能预言纳米片是否会准时出现。事实上,在不断变化的环境中,存在许多未知和不确定性。

本文来自求是缘半导体,本文作为转载分享。

-

三星电子

+关注

关注

34文章

15599浏览量

180091 -

台积电

+关注

关注

43文章

5244浏览量

164761 -

FinFET技术

+关注

关注

1文章

11浏览量

7700 -

5纳米

+关注

关注

0文章

26浏览量

4832 -

莫大康

+关注

关注

0文章

53浏览量

5146

发布评论请先 登录

相关推荐

前段制程FEOL—晶圆上的元件制程

中国大陆半导体成熟制程产能稳步提升

英特尔CEO称公司全力押注18A制程

英特尔宣布推进1.4纳米制程

台积电领跑半导体市场:2纳米制程领先行业,3纳米产能飙升

三星启动二代3纳米制程试制,瞄准60%良率

中国半导体厂商集体发力28nm及更成熟制程

中国看好成熟制程,积极扩增成熟制程产能

全球首款!苹果发布3纳米制程处理器M3系列

台积电高雄厂将以 2 纳米先进制程技术进行生产规划

半导体前端工艺之沉积工艺

博捷芯:晶圆切割提升晶圆工艺制程,国产半导体划片机解决方案

5纳米制程是个坎,半导体先进工艺制程路漫漫

5纳米制程是个坎,半导体先进工艺制程路漫漫

![[<b class='flag-5'>半导体</b>前端<b class='flag-5'>工艺</b>:第二篇] <b class='flag-5'>半导体制程</b><b class='flag-5'>工艺</b>概览与氧化](https://file1.elecfans.com/web2/M00/B1/D7/wKgZomVdeemAEcbqAAInhahz1Ko856.png)

评论