1 引言

1947 年 AT&T 贝尔实验室的科学家 John Bardeen、Walter Brattain 以及 William Shockley 发明世界上第一个半导体晶体管,70 多年来,半导体集成电路得到快速发展。特别是自 1960 年代开始,芯片上的元器件数目几乎每 12 个月就增加一倍,2000年后,半导体集成电路工业发展到了纳米(nm)时代。随着集成电路特征尺寸的逐步缩小到亚纳米 100 nm 范围,在材料、器件结构、工艺以及可靠性等方面出现了一系列新的问题。主要问题包括热载流子效应、短沟道效应、体硅器件的闩锁效应、功耗、寄生电阻、电容增加等等。

为解决这些问题,大量的科研人员进行了大量创新,开发了很多新的技术,如深沟槽隔离技术、HALO 结构、应变硅技术、High K 材料、Low K 材料等等。在众多的新结构器件技术中,绝缘体上硅(SOI: Silicon on Insulator)技术以其独特的结构有效地克服了体硅集成电路的很多不足,充分发挥了体硅集成电路技术的优势,特别是在提高开关速度、减少寄生效应等方面。SOI 技术正逐步成为制造高集成度、高速度、低功耗、高可靠性超大规模集成电路的主流技术[1-5]。

本文就 SOI 技术的发展历史、主要技术及应用、问题与挑战以及将来趋势做出整理和分析。

2 SOI 结构

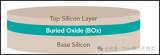

SOI 有两种基本结构,一种是硅-绝缘层型的传 SOI 结构,如图 1(a)所示;另一种是硅-绝缘层-硅三明治型的新型 SOI 结构,如图 1(b)所示。两种基本结构的主要差别是衬底类型不同。

第一种结构中,最熟悉的例子是蓝宝石上外延硅(SOS:Silicon on Sapphire),该结构是在蓝宝石单晶作为衬底,在上面进行外延生长一层单晶硅的薄膜,然后在制作相应的器件。SOS 结构是由 Manasevit 和 Simpson[6]在 1963 和 1964 年间做出。这种结构能提供理想的隔离,并减小 PN 结底部的寄生电容,适合于制作高速大规模集成电路,实现高速和低功耗。一般多采用这种工艺制作 CMOS 电路(互补金属-氧化物-半导体集成电路),即 CMOS/SOS 电路。SOS 是一种异质外延结构,硅膜的缺陷密度较大,因而少数载流子寿命较短(1~10 ns),不适于制作双极器件和电荷耦合器件。

第二种结构中,绝缘层(如 SiO2)位于硅衬底上,在绝缘层上面再由一层单晶硅薄层,形成硅衬底-绝缘层-单晶硅组成的三明治结构。由于顶层的单晶硅薄膜近乎完美的单晶硅,同时它和中间层的界面态很低,且整体应力较小。MOS 等器件能很好地在顶层的单晶硅衬底中制作,且表现出与体硅材料近似的性能,这使得这种结构的 SOI 材料成为当今世界制作 SOI 集成电路元器件的主要材料。下面将重点讲解这种类型的 SOI 技术。

3 SOI 材料的制备技术

3.1 注氧隔离技术(SIMOX)

SIMOX(Seperation by Implant of Oxygen)技术最早由日本的 Izumi 等人在 1970 年代提出[7], 原理很简单,首先将氧注入单晶硅中,为了形成符合化学配比的二氧化硅埋层,氧的注入能量为 200 KeV 剂量为 2e18 cm-2 的氧离子。如此高剂量注入给硅片表面带来很高浓度的缺陷,为了防止硅在注入过程中非晶化并促使注入的氧离子形成致密的 SiO2 以及形成良好的 Si/Si02 界面,注入过程中需要在 600 ℃ 的环境下实现,并且在注入后必须高温(1 300℃)长时间(5 h)来退火,因而 SIMOX 材料成本较高。

在 SIMOX 技术中,注入剂量越大,注入的成本就越高,引入的缺陷就越多,针对这些问题,各地研究者进行不断持续的改进,到了 1990 年代,Nakashima 和 Izumi 提出了低剂量注入的方法来[8]降低表面缺陷,他们发现在注入能量在 180 KeV 和剂量在 1.4e18 cm-2 以下时,表面位错密度会有明显下降,如图 2 所示。

但是注入的剂量不能太低,太低的话,氧的分布曲线是不对称得高斯分布[9],如图 3 所示,形成的二氧化硅不连续。而剂量太大的话则容易造成 Silicon 空洞,如图 4 所示。剂量在 1.4e18 cm-2 时,二氧化硅层连续且均匀。

随着工艺制程的不断进步,对晶圆(Wafer)表面的缺陷要求也越来越高,SIMOX 制备方法就遇到了瓶颈。

3.2 键合技术(WB)

1980 年代开始,已经出现了一些键合技术(WB:Wafer Bonding),它的原理十分简单:将两片被氧化的晶圆(或者一片被氧化)键合在一起,将其中的一片硅片用于研磨、抛光或者化学腐蚀等方法减薄到合适于 SOI 器件要求的厚度,称为 Device wafer,另一片晶圆作为机械支撑衬底,称为 Handle wafer,如图 5 所示。

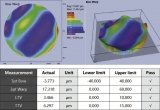

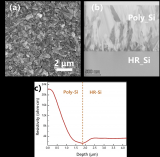

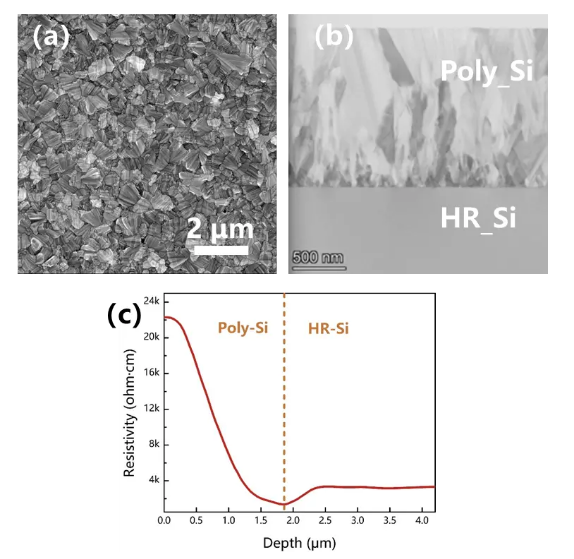

由于键合技术的减薄主要依赖机械抛光、研磨或者化学腐蚀等方法来实现,一方面表面的 EPI 层不可能做得很薄,一般>2μm。另一方面,表面比较粗糙,均匀性比较差,如图 6 所示,这样就限制了该技术的应用。

3.3 智能剥离技术(Smart-cut)

智能剥离技术(Smart-cut)是由 M.Bruel 等人在 1995 年提出的[10],它是建立在离子注入和健合两种技术相结合的基础上。其原理是利用 H+(或者 He+)注入在硅中形成注入层(深度通常小于 1μm),将注氢片与另一支撑片健合(两片中至少有一片表面有一层热氧化的 SiO2 层),经适当的处理后,使注氢片从粒子注入层完整分裂,形成 SOI 结构,如图 7 所示。然后对 Wafer 表面进行抛光处理,再使用外延的方式达到想要的 Silicon 厚度。

Smart-cut 技术的优点主要包括。①H+ 离子的诸如剂量约为 1e16 cm-2,比 SIMOX 注氧剂量要低 2 个数量级,可采用普通的离子注入机就可以完成。②因为是离子注入形成表面的 Silicon,其厚膜均匀性较好,厚度可控,厚薄可用注入能量来控制。③表面缺陷小,单晶性保持较好。④ 埋氧化层(BOX: Buried Oxide)是由热氧化形成的,具有良好的 Si-SiO2 界面。⑤ 玻璃下的硅片仍然可以继续注氢键合,循环使用,大大降低了制备成本。

基于上述优点,Smart-cut 技术在 SOI 材料制备技术中成为最具竞争力的一项技术。自 1995 年以来的短短 20 年里,这种技术得到飞速发展。目前,法国的 Soitec、日本的信越、中国***环球晶圆等公司已经能使用该技术提供大量商用的 SOI 硅片。2014 年,Soitec 还和上海新傲科技股份有限公司(Simgui)达成了有关射频和功率半导体市场 200 mm SOI 晶圆的战略伙伴关系并签署了经销协议,合作主要包括许可和技术转移协议。其中,上海新傲科技可以用 Soitec 的 Smart-Cut 专利技术生产 200 mm SOI 晶圆。

4 SOI 主要制程技术及应用

4.1 RF SOI

当射频芯片在体硅基上形成时, 硅的半导特性引起了基板中射频信号的衰减。同时, 硅基半导体元器件特性还会导致寄生干扰(串扰噪声)的传输。如将 SOI 应用于高阻抗基板上能够显著地改善芯片的高频特性, 极大地降低电阻衰减以及串扰噪声。

RF SOI 称为射频绝缘体上硅技术,该技术不仅可以提供无与伦比的集成度,还可以给窄带物联网带来优越的低功耗性能,如图 8 所示。现今大多数 RF应用在智能手机、WiFi 等无线通信领域,其中绝大多数使用了 RF SOI 工艺制造。RF SOI 对 RF 射频与系统芯片的集成、支持 5G 毫米波技术以及在超低功耗的实现,在手机网络转向 LTE 或 5G 的过程中,设备设计会更加复杂,并且随着 5G 与物联网的不断进化,RF SOI 具有广泛的应用前景,预计每年有 15% 的年增长率,如图 8 所示。

今天,世界上主要代工厂都在大力发展 RF SOI 技术,如 Global Foundries(GF)、TowerJazz、台积电、联电、意法半导体、索尼以及国内的中芯国际、华虹宏力等等。他们均拥有 200 mm RF SOI 晶圆厂产能,较大的代工厂正在生产 300 mm RF SOI 晶圆,如 GF、TowerJazz、台积电和联电等等,工艺节点从 130 nm 到 45 nm 不等。例如,GF 正在两座晶圆厂:纽约 East Fishkill 和新加坡推出 300 mm RF SOI 晶圆,包括 130 nm 和 45 nm 工艺,表 1 为 RF SOI 技术能力及应用市场。Tower Jazz 也在日本的晶圆厂增加 300 mm RF SOI 晶圆产能,该工艺基于 65 nm。联电和台积电也计划进军 300 mm。

300 mm 晶圆相比于 200 mm 有以下优点:① 集成度是 300 mm 晶圆最大的优势,元器件的特征尺寸可以做到 90 nm 以下,可以在更小的面积内集成更多的元器件,满足更加复杂的设计。② 300 mm 提供了更多的过程控制和完全自动化,产品的公差、可重复性和良品率优于 200 mm。③ 300 mm 晶圆采用铜互连层,寄生电阻、电容大大降低,同时元器件间的干扰或耦合也可以大大降低。

4.2 FD SOI

FD-SOI 技术又称完全耗尽型绝缘体上硅(Fully Depleted Silicon On Insulator),是由伯克利教授胡正明在 2000 年发明的。FD-SOI(图 9)可以实现对纳米节点工艺制程下晶体管电流的有效控制和阈值电压的灵活调控,因而 21 世纪伊始,以 Leti、Soitec、 STM 等为代表的欧洲半导体科研机构和公司开始投入该技术的研发[11]。

与体硅材料相比,FD-SOI 具有如下优点:① 减小了寄生电容,提高了运行速度。② 由于减少了寄生电容,降低了漏电,具有更低的功耗。③ 消除了闩锁效应。④ 抑制了衬底的脉冲电流干扰,减少了软错误的发生。⑤ 与现有硅工艺兼容,还可减少工序,成本比较低。从 ISB CEO Handel Jones 公布的数据看,目前 22 nm FD-SOI 的成本将和 28 nm HKMG成本相近。如果线宽再继续缩小,例如到 12 nm 节点,FD-SOI 的成本将显著低于 FinFET,12 nm FD-SOI 的成本比 16 nm FinFET 低 22.4%,比 10 nm FinFET 低 23.4%,比 7 nm FinFET 低 27%。这是因为 12nm FD-SOI 的掩膜数量要少一些,抵消了其衬底成本高于 FinFET 的部分。

4.3 Power SOI

Power SOI 又称为功率绝缘体上硅技术,是 SOI 技术应用的另一个大的领域。在传统的体硅功率集成电路中,由元器件注入衬底的载流子往往会被与其临近的大面积的功率器件所收集,引起不必要的串扰甚至引起功率器件的误开启,这些限制了以 PN 节为隔离的功率器件的应用。而 SOI 技术,元器件在纵向可以通过埋层氧化层(BOX, Buried Oxide Layer)实现纵向隔离,在横向可以通过深沟槽氧化层(DTI, Deep Trench Isolation)实现横向隔离,元器件可以分别做到不同的隔离岛上,避免了以 PN 节为隔离体硅功率集成电路的很多缺点,如串扰、闩锁效应、大泄漏电流以及大面积的隔离区等问题,提高了电路的集成密度。同时,由于 SOI 技术具有比体硅元器件更低的泄漏电流,使其可以在更高电压、更高的温度下进行工作。图13为两种典型的功率SOI器件截面图,图 13(a)为高压 LDMOS 产品,图 13(b)为超高压 LDMOS 产品,它们都分别做到不同的隔离岛上,横向、纵向都与其他元器件用介质隔离。

5 SOI 技术的主要问题与挑战

虽然 SOI 技术比传统的体硅技术具有隔离效果好、寄生效应小、泄漏电流低、集成密度高等优点,但还有很多不足,限制了该技术大规模的应用。

5.1 SOI 晶圆成本偏高

现有 SOI 晶圆的制造成本比较昂贵,在采购价格上比普通硅基晶圆要贵出几倍甚至几十倍,限制了其大规模的应用。现有世界上主流的技术有 WB 技术和 Smart-cut 技术,其中,WB 技术是由两片晶圆经过键合、减薄、抛光等一系列步骤完成,增加了额外的工艺成本;同时,其中的一片会牺牲掉,也将计算在 SOI 的成本之中。而 Smart-cut 技术,目前还是 Soitec 的专利,其他厂商需要得到专利授权、转让等方式才能获得;同时,该技术也需要注入、分离、抛光、外延等工序,工艺成本也比较昂贵。

5.2 浮体效应

SOI 晶体管相对衬底会形成一个寄生电容。电荷在电容上积累,而造成不利的效应,被称作浮体效应。由于浮体效应导致寄生双极晶体管效应、记忆效应、迟滞效应、Kink 效应等等。研究发现,浮体效应不仅可以严重影响模拟电路的特性,还会引起数字电路的逻辑失真和功耗增大。为了抑制浮体效应,研究人员使用了各种方法,如用氩(Ar)注入引入复合中心、源区注入锗(Ge)减小禁带宽度、使用超薄 FD SOI 等等,但是这些工艺复杂,控制困难,往往达不到理想的效果。近年来材料及器件制备技术的发展,问题有了明显改善。

5.3 SOI 晶圆导热性能差

SOI 产品的纵向隔离 BOX 层次以及横向隔离的沟槽中,往往采用 SiO2、Poly 等材质,这些材质在隔离泄漏电流、提高耐压的同时,也使得 SOI 元器件的散热性能变得比传统的体硅器件差很多。特别是针对功率的 SOI 元器件,散热性能差使得安全工作区(SOA, Safe Operation Area)缩小,限制了其使用范围。除非增加晶圆表面的金属面积来增加散热,或者通过额外的工艺,使隔离岛中器件的热从衬底中散出。这些一方面增加了元器件的面积,另一方面增加工艺的难度,提高了生产成本。

5.4 背栅效应

SOI 元器件中,背面栅压通过衬底、埋氧化层对器件的体区产生影响。在不同的背栅条件下,体区的耗尽层宽度会随着衬底电压变化,进而影响到器件的性能。例如阈值电压电压随着背面栅压的增加而线形减小。器件的耐压也随着背面栅压的变化而变化,对于具有上下管(high side 和 low side)的器件,需要兼容在不同背面栅压下耐压都能满足需求,有时会设计出更高耐压的器件,这样在面积上便会有一定的牺牲。

5.5 SOI 产业链不够完善

经过几年的发展,虽然在全球逐渐打造出较为完整的产业链,覆盖材料、设计、代工、封测、应用等各个环节,具备了一定的产业基础,但是起步晚、欠完善,导致 SOI 没能大规模地应用,与传统的 FinFET 展开竞争。随着各个厂商的努力,特别是中国力量的加入,SOI 具有无与伦比的优势,将会带动 SOI 产品更大规模的应用。随着 5G、IoT、智能驾驶时代的来临, SOI 技术将得到更加广泛的使用。

6 结语

SOI 技术从 1960 年代诞生以来,人们研究开发了多种 SOI 技术,在众多的技术中,直接键合和智能剥离技术在获得 SOI 材料中最具潜力,特别是智能剥离技术,已大量应用于现有产品中。如 RF SOI、FD SOI、Power SOI 等技术,已在 5G、loT、汽车、家电等领域得到广泛应用。虽然 SOI 技术也有一些劣势、产业链还不很完善,但是它有传统体硅器件无法比拟的优势,相信在不久的未来,SOI 技术将大规模地爆发。

-

集成电路

+关注

关注

5319文章

10713浏览量

353262 -

绝缘

+关注

关注

1文章

363浏览量

21555 -

SOI

+关注

关注

4文章

63浏览量

17418 -

硅技术

+关注

关注

0文章

5浏览量

4027

原文标题:绝缘衬底上的硅技术 SOI 发展与应用分析

文章出处:【微信号:appic-cn,微信公众号:集成电路应用杂志】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

国产SOI晶圆技术迎来突破性进展,SOI赛道大有可为

射频前端底层技术的卓越性能,RF-SOI为5G赋能

半导体衬底材料的选择

碳化硅单晶衬底的常用检测技术

上海微系统所在300mm RF-SOI晶圆制造技术方面实现突破

上海微系统所在300mm SOI晶圆制造技术方面实现突破

什么是SOI衬底?SOI衬底的优势是什么?

新能源汽车拉动SiC第三代半导体上车:衬底与外延环节的材料,设备国产化机遇

氮化镓衬底和外延片哪个技术高 衬底为什么要做外延层

【贴片SD Card介绍】贴片式tf卡/SD NAND/SD2.0协议

绝缘衬底上的硅技术 SOI发展与应用分析

绝缘衬底上的硅技术 SOI发展与应用分析

评论