VGA(视频图形阵列)作为一种标准的显示接口得到广泛的应用。依据VGA显示原理,介绍了利用FPGA实现对VGA图形控制器的Verilog设计方法。详细描述了各硬件模块的工作原理及实现途径,并给出了软件设计思路。

随着可编程逻辑器件的不断发展及其价格的不断下降,EDA开发软件的不断完善,可编程逻辑设计的应用优势逐渐显示出来,特别是大规模可编程器件。而FPGA具有功能强大,开发过程投资小、周期短等特点,成为当今硬件设计的首选方式之一。VGA(视频图形阵列)作为一种标准的显示接口得到广泛地应用。利用FPGA芯片和EDA设计方法,可以灵活地根据用户需求,设计出针对性强的VGA显示控制器,不仅降低了生产成本也可以方便快速地对产品进行升级换代。设计采用 Quartus II 软件工具,并以 Altera公司的Cyclone系列FPGA的器件为主实现硬件平台的设计。

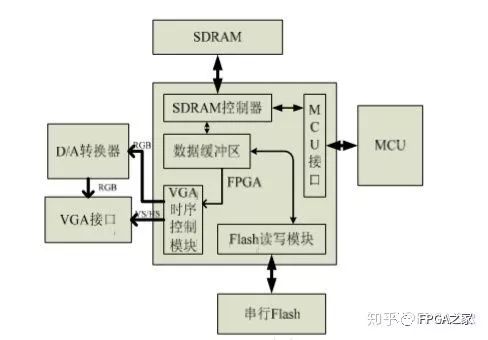

1. 硬件系统框图采用模块化设计方法。

本设计的VGA控制器主要由以下模块组成:VGA 时序控制模块、内部时钟产生模块、SDRAM控制模块、串行Flash读取模块等,如图1所示。

图1 系统框图

2. 主要模块设计

2.1 VGA 时序控制模块

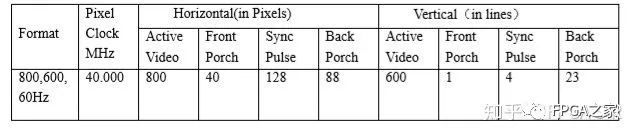

VGA时序控制模块是整个显示控制器的关键部分,其实质就是完成VGA显示卡的功能。主要作用就是在一定的工作频率下,产生准确的时序关系(VS-垂直同步信号,HS-水平同步信号,消隐信号之间的关系)。及其在准确的时序下对数据缓存区对数据进行读取,读完数据后使 SDRAM 控制器及时的刷新缓存区的数据。其中产生准确的时序关系为此模块重点,在VGA显示过程中,完成一行扫描所需要的时间称为水平扫描时间,完成一帧扫描所需要的时间称为垂直扫描时间。每扫描完一行用行同步信号进行同步;扫描完所有行后用场同步信号进行同步。本设计采用的是800Hz x 600Hz x 60Hz模式。依据时序标准,每显示行包含1056点,其中800点为有效显示区,256点为消隐区,每行的行同步脉冲低电平宽度为128个像素点;同理每场有628行,有效行为600行,其中场同步脉冲低电平宽度为4行。其行、场时序如表 1 。

表 1 行扫描、场扫描时序

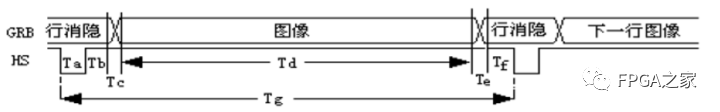

图2 HS时序

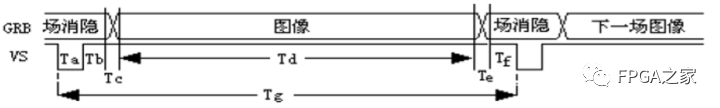

图3 VS时序

其中图2,td=800,tg=1056,ta=80,te+tf=80,tb+tc=128,单位为一个像素时钟周期。

其中图3,td=600,tg=628,ta=1,te+tf=23,tb+tc=4,单位为一个line时间。

依据这个标准,外部50MHz时钟经过FPGA内部PLL得到所需要的40MHz像素时钟,并进行对应的像素点数和扫描行数进行分频处理,可以得到符合要求的行频率、场频率和消隐信号。

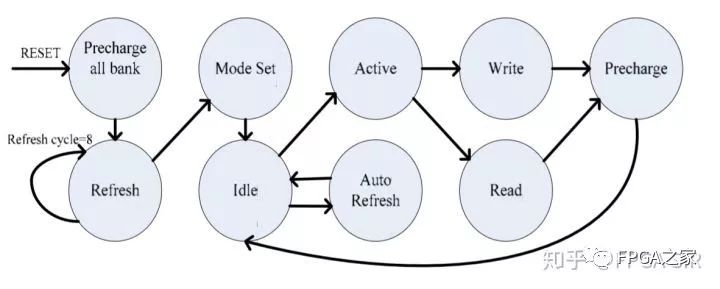

2.2 SDRAM控制模块及动态数字显示方法

在基于FPGA的图像显示系统中,常常需要用到大容量、高速度的存储器。而在各种随机存储器件中,SDRAM的价格低、速度快、容量大是比较理想的器件。但SDRAM控制逻辑较为复杂,要采用状态机的设计方法来实现 SDRAM 的控制模块(也可以使用SDRAM IP核实现)。其 SDRAM控制状态机如图 4 。

图4 SDRAM状态机

其中包含了9个状态,其中从Precharge到ModeSet为SDRAM上电后的初始化过程,其余状态为SDRAM的正常读写及刷新操作过程。对于SDRAM自身的操作本文不做详细介绍,下面具体介绍动态显示数字的方法。

系统上电后,SDRAM上电后的初始化完成后。先通过Flash读写控制模块,把Flash中的静态图片读取出来,然后写入SDRAM中直到Flash中的图片完全存入SDRAM。此时启动VGA时序控制模块进行图片的显示。

对于动态显示数字方法,可以先利用字模提取软件把字模信息提取出来。而 Altera公司的FPGA器件内均内置了嵌入式阵列块,通过调用其中的LPM_ROM模块。可以任意设置参数,构成内置的ROM存储器,存储所摘要的字模信息。本系统的字模为16pixels长 x 16pixels宽 x 16位色(R5G6B5),所以利用LPM_ROM模块,占用了将近10个 M4K(FPGA内置 块ram)。

本系统通过接受外部 MCU 发来的命令来确定显示数字的区域及要显示的数字。因为VGA时序中存在较长的消隐期间,其期间是没有显示数据传递的。所以可以通过消隐期间实行对SDRAM的写操作,对图片固定地址写入字模信息。其具体步骤:

(1)、确定要显示数字的图像区域首地址;

(2)、确定要显示数字信息位于ROM中的地址;

(3)、启动 SDRAM 写操作;

(4)、SDRAM 写操作地址增加16后,地址继续增加800(即一行),而 ROM地址每次增加 1;

(5)、如此循环16 次(字模为 16 x16)后,如果还有要写的数字则继续(1)步骤,否则停止写操作。

因为只是动态的改变数字,所以对原图像改动的数据量不是很大,所以不会造成图像闪烁现象。此方法缺点就是字模占用的 块RAM 资源较多,如果字模只是固定颜色的情况,则 块RAM 资源只用到 1 个 M4K,所以在资源紧张的情况下还得需要各方面比较,得到最合适的颜色分配。

2.3 Flash 的读写模块

现在数字电路设计中,经常需要保存大量数据,Flash Memory 以其集成度高、低成本、使用方便等优点,因此也成为设计人员的首选。

Flash可以分两类:并行和串行。并行存储量大,速度快;而串行存储量相对较小,但体积小连线简单,可减少电路面积,节约成本,二者各有优缺点,根据实际需要选取。本系统对速度要求不是很高,所以选用了串行 Flash,为意法半导体推出的 M25P32。M25P32为SPI 接口,具有 4MB 容量,对与本设计每幅图片接近 1MB,则可以存储 4 副图片,可以进行 4 个界面的切换显示。

其模块设计必须严格按照 Flash 的时序控制信号。对于首次使用 Flash,先需要进行擦除操作,编程指令可以将 1 变成 0。往 Flash 写入图片数据时,还是需要调用 FPGA 中的宏模块制作一个 ROM,但是由于 Flash 容量较大,一般FPGA没有这么大的存储空间,所以数据需要分多次写入。FPGA的ROM数据保存在.mif文中,.mif 由 Matlab 直接生成.mif文件,也可以在 Quartus II 中生成。

在对 M25P32 的操作中,需要注意的是一些指令在操作完成后,需要留出一段时间 Flash进行数据处理,比如写寄存器为 5ms~15ms等,如果没有等待这段处理过程,则会出现一些误操作。

FLASH操作步骤:

(1)、FLASH擦除,一般通过SPI发FLASH擦除命令,等待结束。

(2)、FLASH写,发送写命令,写地址,数据。一般FLASH保存一些参数,或者数据存储用,如果FLASH内已经有可用的数据,可以根据实际情况,也可以先读FLASH。

(3)、FLASH读,发送读命令,读地址。

3、验证

利用可编程逻辑器件(FPGA)可以很方便地实现数字系统设计,而在Altera的QuartusII软件平台下,FPGA 设计的各个阶段都得到了很好的支持,两者有效结合使得数字系统的设计更加方便快捷。

通过硬件平台的验证,基于 FPGA 的VGA图形显示器已达到设计要求,可以稳定地实现界面的显示,并可以在界面上根据需要进行数字的动态改变显示,对于一些工业监控场合的应用,尤其数据量不是很大的场合尤为适合,不仅可以及时显示当前状态,还可以保存关机时状态。

-

FPGA

+关注

关注

1602文章

21309浏览量

593128 -

图形控制器

+关注

关注

0文章

8浏览量

11224

原文标题:基于FPGA的VGA图形控制器的设计

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PIC32MZDA图形控制器问题

如何使用Verilog实现基于FPGA的SDRAM控制器?

基于FPGA的LCD&VGA控制器设计

VGA图形控制器的FPGA实现

基于FPGA的VGA图形控制器设计

基于FPGA的图形式AMLCD控制器的设计

采用FPGA对VGA图形控制器的Verilog设计方法

采用FPGA对VGA图形控制器的Verilog设计方法

评论